# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 20MHz                                                                        |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622at-20i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the                                                   | Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En                                                    | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                        | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                         | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |  |  |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                         | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                         | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                                                                        | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                    | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the                                                                                                         | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                      | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                                                                           | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                        | pts                                                                                                                     | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| TMR0 Ove<br>nables the<br>sables the                                                                                                                                           | rflow Interrupt Er<br>TMR0 interrupt                                                                                               |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| nables the<br>isables the                                                                                                                                                      | TMR0 interrupt                                                                                                                     | nable bit                                                                                                               |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| sables the                                                                                                                                                                     |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                | I MRU interrupt                                                                                                                    |                                                                                                                         | 1 = Enables the TMR0 interrupt                                                                                                                                       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| INTE: RB0/INT External Interrupt Enable bit                                                                                                                                    |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| <ul> <li>1 = Enables the RB0/INT external interrupt</li> <li>0 = Disables the RB0/INT external interrupt</li> </ul>                                                            |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 3 <b>RBIE</b> : RB Port Change Interrupt Enable bit                                                                                                                            |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 1 = Enables the RB port change interrupt                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                | RB port change                                                                                                                     | •                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| TMR0 Ove                                                                                                                                                                       | rflow Interrupt Fl                                                                                                                 | ag bit                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MR0 registe                                                                                                                                                                    | er has overflowed                                                                                                                  | d (must be cle                                                                                                          | eared in soft                                                                                                                                                        | ware)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MR0 registe                                                                                                                                                                    | er did not overflov                                                                                                                | W                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RB0/INT E                                                                                                                                                                      | xternal Interrupt                                                                                                                  | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RB Port Cl                                                                                                                                                                     | hange Interrupt F                                                                                                                  | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

| <ul> <li>1 = When at least one of the RB&lt;7:4&gt; pins changed state (must be cleared in software)</li> <li>0 = None of the RB&lt;7:4&gt; pins have changed state</li> </ul> |                                                                                                                                    |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                               | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |  |  |  |  |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

|                                                                                  | = =                   |  |  |  |  |  |

|----------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|

| ; Initial PORT settings:                                                         | PORTB<7:4> Inputs     |  |  |  |  |  |

| ;                                                                                | PORTB<3:0> Outputs    |  |  |  |  |  |

| ; PORTB<7:6> have external pull-up and are not<br>; connected to other circuitry |                       |  |  |  |  |  |

| ;                                                                                |                       |  |  |  |  |  |

| ;                                                                                | PORT latch PORT pins  |  |  |  |  |  |

| ;                                                                                |                       |  |  |  |  |  |

|                                                                                  | -                     |  |  |  |  |  |

|                                                                                  |                       |  |  |  |  |  |

| BCF PORTB, 7                                                                     | ; 01pp pppp 11pp pppp |  |  |  |  |  |

| BCF PORTB, 6                                                                     | ; 10pp pppp 11pp pppp |  |  |  |  |  |

| BSF STATUS, RPO                                                                  | ;                     |  |  |  |  |  |

| BCF TRISB, 7                                                                     | ;10pp pppp 11pp pppp  |  |  |  |  |  |

| BCF TRISB, 6                                                                     | ;10pp pppp 10pp pppp  |  |  |  |  |  |

| ;                                                                                |                       |  |  |  |  |  |

| ; Note that the user may h                                                       | nave expected the pin |  |  |  |  |  |

| ; values to be 00pp pppp.                                                        | The 2nd BCF caused    |  |  |  |  |  |

| ; RB7 to be latched as the                                                       | e pin value (High).   |  |  |  |  |  |

|                                                                                  |                       |  |  |  |  |  |

# 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

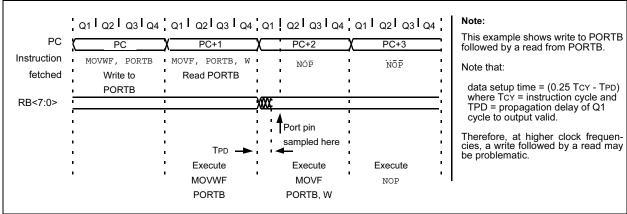

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-7: SUCCESSIVE I/O OPERATION

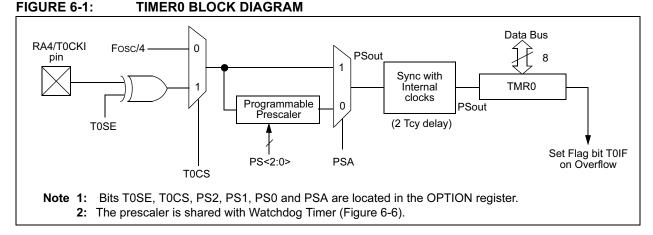

### 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

#### 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

#### FIGURE 6-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| (Program<br>Counter) | ( PC-1      | ) PC        | ( <u>PC+1</u> )        | PC+2                   | <u>PC+3</u> χ          | PC+4                   | PC+5 χ                     | PC+6                     |

|----------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch |             | MOVWF TMR   | 0MOVF TMR0,V           | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                | 1                        |

|                      | i.          | 1           |                        |                        | i                      |                        | i                          |                          |

| TMR0                 | то х        | T0+1 )(     | T0+2 X                 | 1                      | NT0                    |                        | NT0+1 \                    | NT0+2 )                  |

| Instruction          | 1<br>1<br>1 | 1<br>1<br>1 | <b></b>                | <b>≜</b>               | <b>≜</b>               | <b>†</b>               | <b>†</b>                   | <b>≜</b>                 |

| Executed             | 1           | 1           | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + |

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          |              | ,                                             |

|----------|--------------|-----------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in<br>;Bank 0                |

| 2.CLRWDT |              | ;Clear WDT                                    |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                       |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                       |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                      |

| 6.MOVWF  | OPTION       | ;are required only if<br>;desired PS<2:0> are |

| 7.CLRWDT |              | ;000 or 001                                   |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                            |

| 9.MOVWF  | OPTION       | ;desired WDT rate                             |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                             |

|          |              |                                               |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

## EXAMPLE 6-2:

#### CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                                        |

|--------|-------------|------------------------------------------|

| CLRWDT |             | ;Clear WDT and                           |

|        |             | ;prescaler                               |

| BSF    | STATUS, RPO |                                          |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new<br>;prescale value and |

|        |             | ;clock source                            |

| MOVWF  | OPTION REG  |                                          |

| BCF    | STATUS, RPO |                                          |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 r | nodule regi | ster  |        |        |        |        |        | XXXX XXXX       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG      | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        |             | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**Note:** Shaded bits are not used by TMR0 module.

NOTES:

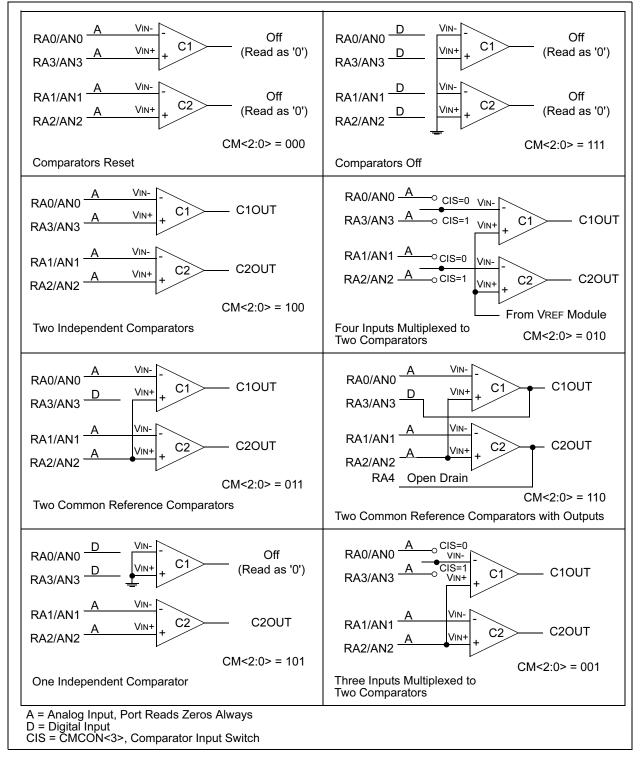

## 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

#### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                              |                                 | <b>(</b> | ,   |       |       |       |       |

|---------|------------------------------|---------------------------------|----------|-----|-------|-------|-------|-------|

|         | R-0                          | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT                        | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |

|         | bit 7                        |                                 |          |     |       |       |       | bit 0 |

|         |                              |                                 |          |     |       |       |       |       |

| bit 7   | <b>C2OUT</b> : Co            | omparator 2                     | output   |     |       |       |       |       |

|         | 1 = C2 VIN                   | + > C2 VIN-                     |          |     |       |       |       |       |

|         | 0 = C2 VIN                   | + < C2 VIN-                     |          |     |       |       |       |       |

| bit 6   | C10UT: Co                    | omparator 1                     | output   |     |       |       |       |       |

|         | 1 = C1 VIN                   | + > C1 VIN-                     |          |     |       |       |       |       |

|         | 0 = C1 VIN                   | + < C1 VIN-                     |          |     |       |       |       |       |

| bit 5-4 | Unimplemented: Read as '0'   |                                 |          |     |       |       |       |       |

| bit 3   | CIS: Comparator Input Switch |                                 |          |     |       |       |       |       |

|         | When CM<                     | <2:0>: = 001                    | :        |     |       |       |       |       |

|         | 1 = C1 VIN-                  | - connects to                   | o RA3    |     |       |       |       |       |

|         | 0 = C1 VIN                   | - connects to                   | o RA0    |     |       |       |       |       |

|         | When CM<                     | <2:0> = 010:                    |          |     |       |       |       |       |

|         |                              | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |

|         |                              | I- connects t                   |          |     |       |       |       |       |

|         |                              | - connects to                   |          |     |       |       |       |       |

|         | C2 VIN                       | I- connects t                   | 0 RA1    |     |       |       |       |       |

| bit 2-0 | CM<2:0>:                     | Comparator                      | mode.    |     |       |       |       |       |

|         |                              |                                 |          |     |       |       |       |       |

|         | Legend:                      |                                 |          |     |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

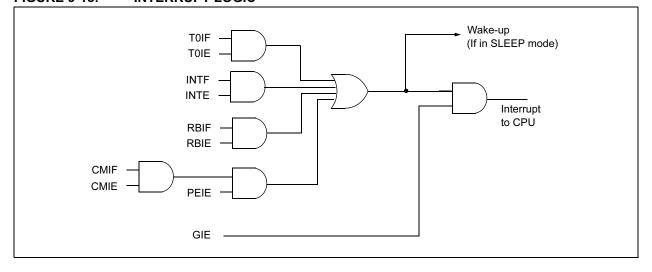

#### 9.5 Interrupts

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

# **10.1** Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                                  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and<br>the result is placed in the W<br>register. |  |  |  |  |

| Words:           | 1                                                                                                                          |  |  |  |  |

| Cycles:          | 1                                                                                                                          |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                      |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |

| Words:           | 1                                                                                                                      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                      |  |  |  |  |  |

| Example          | ANDLW 0x5F                                                                                                             |  |  |  |  |  |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                        |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                           |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                    |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                              |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                              |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                              |  |  |  |  |  |  |

| Example          | ADDWF FSR, <b>O</b>                                                                                                                                                            |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                    |  |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |  |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                    |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |

| MOVWF            | Move W to f                                                                                                                                                                                                                                                                          |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                    |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                                                                 |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |

| Description:     | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVWF OPTION                                                                                                                                                                                                                                                                         |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F                                                                                                                                                                                                |

|                  | $\begin{array}{rcl} \text{OPTION} &= & 0x4F \\ \text{W} &= & 0x4F \end{array}$                                                                                                                                                                                                       |

| NOP              | No Operation |        |      |      |  |  |

|------------------|--------------|--------|------|------|--|--|

| Syntax:          | [ label ]    | NOP    |      |      |  |  |

| Operands:        | None         |        |      |      |  |  |

| Operation:       | No opera     | ation  |      |      |  |  |

| Status Affected: | None         |        |      |      |  |  |

| Encoding:        | 00           | 0000   | 0xx0 | 0000 |  |  |

| Description:     | No opera     | ition. |      |      |  |  |

| Words:           | 1            |        |      |      |  |  |

| Cycles:          | 1            |        |      |      |  |  |

| Example          | NOP          |        |      |      |  |  |

| OPTION           | Load Option Register                                                                                                 |                                                              |                                                              |                                     |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------|--|--|--|--|

| Syntax:          | [ label ]                                                                                                            | OPTION                                                       | N                                                            |                                     |  |  |  |  |

| Operands:        | None                                                                                                                 |                                                              |                                                              |                                     |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                             |                                                              |                                                              |                                     |  |  |  |  |

| Status Affected: | None                                                                                                                 |                                                              |                                                              |                                     |  |  |  |  |

| Encoding:        | 00                                                                                                                   | 0000                                                         | 0110                                                         | 0010                                |  |  |  |  |

| Description:     | The control<br>loaded in<br>This instr<br>code con<br>products.<br>able/writa<br>directly a                          | the OP<br>fuction is<br>apatibility<br>Since C<br>able regis | FION regi<br>supporte<br>with PIC<br>PTION is<br>ster, the u | ster.<br>ed for<br>16C5X<br>a read- |  |  |  |  |

| Words:           | 1                                                                                                                    |                                                              |                                                              |                                     |  |  |  |  |

| Cycles:          | 1                                                                                                                    |                                                              |                                                              |                                     |  |  |  |  |