Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                     |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

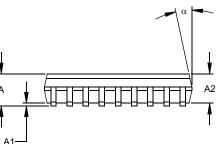

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c622t-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

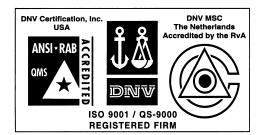

#### FIGURE 3-1: BLOCK DIAGRAM

# 4.3 PCL and PCLATH

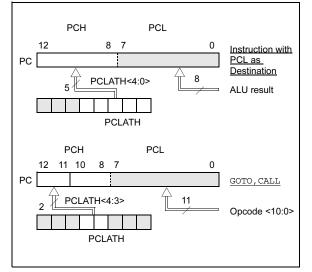

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any RESET, the PC is cleared. Figure 4-8 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-8: LOADING OF PC IN DIFFERENT SITUATIONS

# 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

## 4.3.2 STACK

The PIC16C62X family has an 8-level deep x 13-bit wide hardware stack (Figure 4-2 and Figure 4-3). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

#### TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |  |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|--|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |  |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |  |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |  |

Legend: ST = Schmitt Trigger input

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

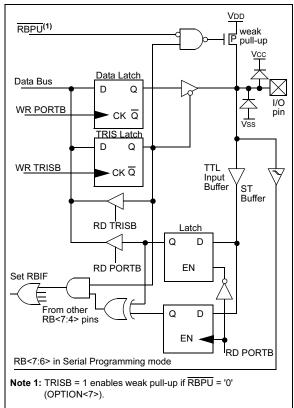

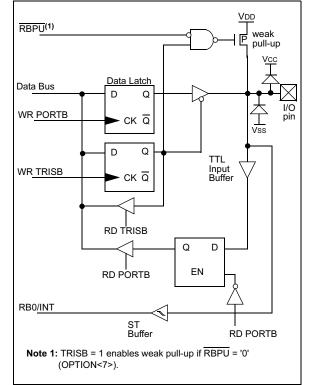

### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a High Impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A \ typical$ ). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (e.g., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

#### FIGURE 5-5: BLOCK DIAGRAM OF RB<7:4> PINS

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes.)

| Note: | If a change on the I/O pin should occur       |  |  |  |

|-------|-----------------------------------------------|--|--|--|

|       | when the read operation is being executed     |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

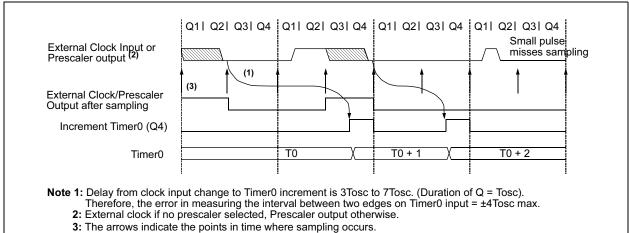

### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |  |

|-------|--------------|-----------------------------------|--|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |  |

| CLRF  | PORTA        | ;Init PORTA                       |  |

| BSF   | STATUS, RPO  | ;Select Bank1                     |  |

| MOVLW | 0x07         | ;Initialize data direction        |  |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |  |

|       |              | ;RA<4:3> as outputs               |  |

|       |              | ;TRISA<7:5> always read `0'       |  |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |  |

| CALL  | DELAY 10     | ;10µs delay                       |  |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |  |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |  |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |  |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |  |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |  |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |  |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |  |

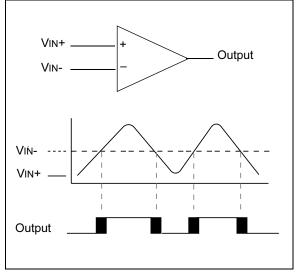

# 7.2 Comparator Operation

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

## 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

#### 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

#### 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |

|       | interrupt flag may not get set.            |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

# 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will

Vdd ∆Vt = 0.6V RIC Rs < 10K Δικ **I**LEAKAGE CPIN VT = 0.6V ±500 nA 5 pF Vss Input Capacitance Legend CPIN = Threshold Voltage Vт = Leakage Current at the pin due to various junctions ILEAKAGE = = Interconnect Resistance RIC Rs = Source Impedance Analog Voltage VA =

FIGURE 7-4: ANALOG INPUT MODEL

wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

#### 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

#### 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A maximum source impedance of  $10 \ k\Omega$ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16C62X devices can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

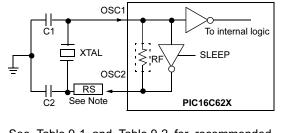

# 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

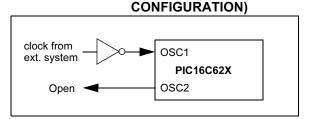

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 9-1). The PIC16C62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

See Table 9-1 and Table 9-2 for recommended values of C1 and C2.

**Note:** A series resistor may be required for AT strip cut crystals.

#### FIGURE 9-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

# TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| R                                                                                                                                                                                                                                                                                                                  | anges Charao                  | 21                                      |                                         |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|--|--|

| Mode                                                                                                                                                                                                                                                                                                               | Freq                          | <b>0562(C2)</b>                         |                                         |  |  |

| ХТ                                                                                                                                                                                                                                                                                                                 | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 82 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |

| HS                                                                                                                                                                                                                                                                                                                 | 8.0 MHz<br>16.0 MHz 🔨         | 10-68 pF<br>10-22 pF                    | 10 - 68 pF<br>10 - 22 pF                |  |  |

| Higher capacitance increases the stability of the oscil-<br>lator but also increases the start-up time. These<br>walkes are for design guidance only. Since each<br>resonator has its own characteristics, the user<br>should consult the resonator manufacturer for<br>appropriate values of external components. |                               |                                         |                                         |  |  |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                                                                                                                                                                                                                                                                                                                                                                                                                    | Freq     | OSC1(C1)    | OSC2(C2)                |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------------------------|--|--|--|

| LP                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32 kHz   | 68 - 100 pF | 68 - 100 pF             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | 200 kHz  | 15 - 30 pF  | 15 - 30 pF              |  |  |  |

| хт                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100 kHz  | 68 - 150 pF | 150-300 pF              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 MHz    | 15 - 30 pF  | 15-30 pF                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4 MHz    | 15 - 30 pF  | 15-30 pF                |  |  |  |

| HS                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8 MHz    | 15-30 pF    | <sup>V</sup> 15 - 30 pF |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 MHz   | 15-30 pF    | 15 - 30 pF              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 MHz 🔨 | 15-30 pF    | 15 - 30 pF              |  |  |  |

| Higher capacitance increases the stability of the<br>oscillator but also increases the stat-up time.<br>These values are for design guidance only. Rs may<br>be required in HS mode as well as XT mode to<br>avoid overdriving crystals with low drive level<br>specification. Since each crystal has its own<br>characteristics, the user should consult the crystal<br>manufacturer for appropriate values of external<br>components. |          |             |                         |  |  |  |

#### TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | <u>uuuu</u> uuuu                                                                                                                                           | <u></u>                                                                                                           |

| INDF     | 00h     |                | _                                                                                                                                                          | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | <u>uuuu</u> uuuu                                                                                                  |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

#### TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

# PIC16C62X

| CLRW                                                                               | Clear W                                                                                                                                                                                                                                                                                                                                                | COMF                                                                                          | Complement f                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                            | [ <i>label</i> ] CLRW                                                                                                                                                                                                                                                                                                                                  | Syntax:                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                           |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                   | Operands:                                                                                     | $0 \leq f \leq 127$                                                                                                                                                                                                                                                                                 |

| Operation:                                                                         | $00h \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                  |                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                           |

|                                                                                    | $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                      | Operation:                                                                                    | $(\overline{f}) \rightarrow (dest)$                                                                                                                                                                                                                                                                 |

| Status Affected:                                                                   | Z                                                                                                                                                                                                                                                                                                                                                      | Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                          | 00 0001 0000 0011                                                                                                                                                                                                                                                                                                                                      | Encoding:                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                   |

| Description:                                                                       | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                            | Description:                                                                                  | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the                                                                                                                                                                                       |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | result is stored back in register 'f'.                                                                                                                                                                                                                                                              |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                      | Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                   |

| Example                                                                            | CLRW                                                                                                                                                                                                                                                                                                                                                   | Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                   |

|                                                                                    | Before Instruction<br>W = 0x5A                                                                                                                                                                                                                                                                                                                         | Example                                                                                       | COMF REG1,0                                                                                                                                                                                                                                                                                         |

|                                                                                    | W = 0x5A<br>After Instruction                                                                                                                                                                                                                                                                                                                          |                                                                                               | Before Instruction                                                                                                                                                                                                                                                                                  |

|                                                                                    | W = 0x00 $Z = 1$                                                                                                                                                                                                                                                                                                                                       |                                                                                               | REG1 = 0x13 After Instruction $REG1 = 0x13$ $W = 0xEC$                                                                                                                                                                                                                                              |

| CLRWDT                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                   |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Syntax:                                                                            | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| <b>-j</b>                                                                          |                                                                                                                                                                                                                                                                                                                                                        | DECF                                                                                          | Decrement f                                                                                                                                                                                                                                                                                         |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                   | DECF<br>Svntax:                                                                               | Decrement f                                                                                                                                                                                                                                                                                         |

| -                                                                                  | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                             | Syntax:                                                                                       | [label] DECF f,d                                                                                                                                                                                                                                                                                    |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,                                                                                                                                                                                                                                                                                        | _                                                                                             |                                                                                                                                                                                                                                                                                                     |

| Operands:                                                                          | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                             | Syntax:                                                                                       | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                            |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow TO$                                                                                                                                                                                                                                                                  | Syntax:<br>Operands:                                                                          | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                               |

| Operands:<br>Operation:                                                            | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                      | Syntax:<br>Operands:<br>Operation:                                                            | $\begin{bmatrix} label \end{bmatrix} DECF f,d$<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:                                        | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow PD$<br>$\overline{TO}, PD$                                                                                                                                                                                                          | Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | [ <i>label</i> ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow PD$<br>$\overline{TO}, PD$<br>00  0000  0110  0100<br>CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>pres <u>caler</u> of <u>the</u> WDT. STATUS                                                            | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                                    |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO$<br>$1 \rightarrow PD$<br>TO, PD<br>OUDIMIC OTIO<br>CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.                                                                                | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011 \qquad dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 & 0000 & 0110 & 0100 \\ \hline \end{array}$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.<br>1 | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1     |

| SUBLW        | Subtract W from Literal                                                       | SUBWF               | Subtract W from f                                                              |

|--------------|-------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------|

| Syntax:      | [ <i>label</i> ] SUBLW k                                                      | Syntax:             | [ <i>label</i> ] SUBWF f,d                                                     |

| Operands:    | $0 \le k \le 255$                                                             | Operands:           | $0 \le f \le 127$                                                              |

| Operation:   | $k - (W) \to (W)$                                                             |                     | d ∈ [0,1]                                                                      |

| Status       | C, DC, Z                                                                      | Operation:          | (f) - (W) $\rightarrow$ (dest)                                                 |

| Affected:    |                                                                               | Status<br>Affected: | C, DC, Z                                                                       |

| Encoding:    | 11 110x kkkk kkkk                                                             |                     |                                                                                |

| Description: | The W register is subtracted (2's                                             | Encoding:           | 00 0010 dfff ffff                                                              |

|              | complement method) from the eight<br>bit literal 'k'. The result is placed in | Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0, |

|              | the W register.                                                               |                     | the result is stored in the W register.                                        |

| Words:       | 1                                                                             |                     | If 'd' is 1, the result is stored back in                                      |

| Cycles:      | 1                                                                             |                     | register 'f'.                                                                  |

| Example 1:   | SUBLW 0x02                                                                    | Words:              | 1                                                                              |

| ·            | Before Instruction                                                            | Cycles:             | 1                                                                              |

|              | W = 1                                                                         | Example 1:          | SUBWF REG1,1                                                                   |

|              | C = ?                                                                         |                     | Before Instruction                                                             |

|              | After Instruction                                                             |                     | REG1= 3<br>W = 2                                                               |

|              | W = 1<br>C = 1; result is positive                                            |                     | C = ?                                                                          |

| Example 2:   | Before Instruction                                                            |                     | After Instruction                                                              |

| Example 2.   | W = 2                                                                         |                     | REG1= 1                                                                        |

|              | C = ?                                                                         |                     | W = 2<br>C = 1; result is positive                                             |

|              | After Instruction                                                             | Example 2:          | Before Instruction                                                             |

|              | W = 0                                                                         | ·                   | REG1= 2                                                                        |

|              | C = 1; result is zero                                                         |                     | W = 2                                                                          |

| Example 3:   | Before Instruction                                                            |                     | C = ?                                                                          |

|              | W = 3<br>C = ?                                                                |                     | After Instruction                                                              |

|              | After Instruction                                                             |                     | REG1= 0<br>W = 2                                                               |

|              | W = 0 x F F                                                                   |                     | C = 1; result is zero                                                          |

|              | C = 0; result is negative                                                     | Example 3:          | Before Instruction                                                             |

|              |                                                                               |                     | REG1= 1<br>W = 2                                                               |

|              |                                                                               |                     | W = 2<br>C = ?                                                                 |

|              |                                                                               |                     | After Instruction                                                              |

|              |                                                                               |                     | REG1= 0xFF                                                                     |

|              |                                                                               |                     | W = 2                                                                          |

|              |                                                                               |                     | C = 0; result is negative                                                      |

# PIC16C62X

NOTES:

# 11.0 DEVELOPMENT SUPPORT

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ®

- PICDEM MSC

- microID®

- CAN

- PowerSmart®

- Analog

#### 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PICmicro emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

#### 11.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PICmicro MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- · User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# PIC16C62X

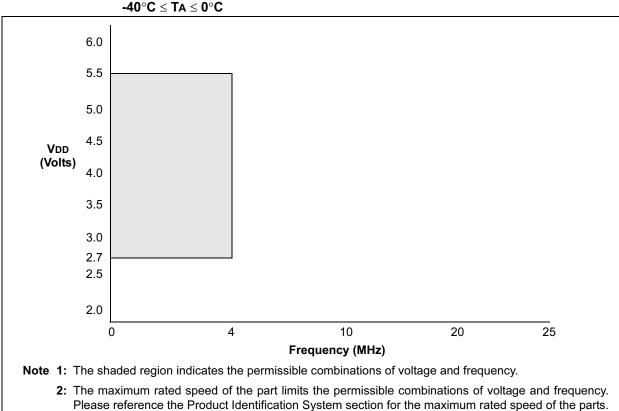

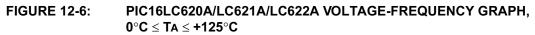

#### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended) (CONT.)

| PIC16C62X                                                         |                                                                   |                                                                                                                                                                                                                                                                        |                  | Standard Operating Conditions (unless otherwise stated)                                                                                                                                                              |                                                   |                                        |                                                                                                                                   |  |  |  |

|-------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                   |                                                                   |                                                                                                                                                                                                                                                                        |                  | Operating temperature $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and<br>$0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and<br>$-40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extended |                                                   |                                        |                                                                                                                                   |  |  |  |

| PIC16LC62X                                                        |                                                                   |                                                                                                                                                                                                                                                                        |                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                 |                                                   |                                        |                                                                                                                                   |  |  |  |

| Param<br>. No.                                                    | Sym                                                               | Characteristic                                                                                                                                                                                                                                                         | Min              | Тур†                                                                                                                                                                                                                 | Мах                                               | Units                                  | Conditions                                                                                                                        |  |  |  |