Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc620a-04-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0     | General Description                 | . 5 |

|---------|-------------------------------------|-----|

| 2.0     | PIC16C62X Device Varieties          | . 7 |

|         | Architectural Overview              |     |

|         | Memory Organization                 |     |

| 5.0     | I/O Ports                           | 25  |

| 6.0     | Timer0 Module                       | 31  |

| 7.0     | Comparator Module                   | 37  |

| 8.0     | Voltage Reference Module            | 43  |

| 9.0     | Special Features of the CPU         | 45  |

| 10.0    | Instruction Set Summary             | 61  |

|         | Development Support                 |     |

| 12.0    | Electrical Specifications           | 81  |

| 13.0    | Device Characterization Information | 09  |

| 14.0    | Packaging Information 1             | 13  |

|         | Jix A: Enhancements 1               |     |

| Append  | Jix B: Compatibility                | 19  |

| Index   |                                     | 21  |

| On-Line | e Support 1                         | 23  |

| System  | Is Information and Upgrade Hot Line | 23  |

|         | Response 1                          |     |

| Product | t Identification System 1           | 25  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

# 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

# FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C620/621

| File     |                     |                     | File        |

|----------|---------------------|---------------------|-------------|

| Address  | 3                   |                     | Address     |

| 00h      | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h         |

| 01h      | TMR0                | OPTION              | 81h         |

| 02h      | PCL                 | PCL                 | 82h         |

| 03h      | STATUS              | STATUS              | 83h         |

| 04h      | FSR                 | FSR                 | 84h         |

| 05h      | PORTA               | TRISA               | 85h         |

| 06h      | PORTB               | TRISB               | 86h         |

| 07h      |                     |                     | 87h         |

| 08h      |                     |                     | 88h         |

| 09h      |                     |                     | 89h         |

| 0Ah      | PCLATH              | PCLATH              | 8Ah         |

| 0Bh      | INTCON              | INTCON              | 8Bh         |

| 0Ch      | PIR1                | PIE1                | 8Ch         |

| 0Dh      |                     |                     | 8Dh         |

| 0Eh      |                     | PCON                | 8Eh         |

| 0Fh      |                     |                     | 8Fh         |

| 10h      |                     |                     | 90h         |

| 11h      |                     |                     | 91h         |

| 12h      |                     |                     | 92h         |

| 13h      |                     |                     | 93h         |

| 14h      |                     |                     | 94h         |

| 15h      |                     |                     | 95h         |

| 16h      |                     |                     | 96h         |

| 17h      |                     |                     | 97h         |

| 18h      |                     |                     | 98h         |

| 19h      |                     |                     | 99h         |

| 1Ah      |                     |                     | 9Ah         |

| 1Bh      |                     |                     | 9Bh         |

| 1Ch      |                     |                     | 9Ch         |

| 1Dh      |                     |                     | 9Dh         |

| 1Eh      |                     |                     | 9Eh         |

| 1Fh      | CMCON               | VRCON               | 9Fh         |

| 20h      |                     | _                   | A0h         |

|          | General             |                     |             |

|          | Purpose<br>Register |                     |             |

| 6Fh      | 5                   |                     |             |

| 70h      |                     |                     |             |

|          |                     |                     |             |

|          |                     |                     |             |

|          |                     |                     |             |

| 7Fh      |                     |                     | FFh         |

|          | Bank 0              | Bank 1              |             |

| <b>—</b> |                     | 1 4                 |             |

| Unimp    | plemented data me   | mory locations, r   | ead as '0'. |

| Note 1:  | Not a physical re   | egister.            |             |

|          |                     |                     |             |

|          |                     |                     |             |

# FIGURE 4-5:

# DATA MEMORY MAP FOR THE PIC16C622

|                 | 1116                |                     |                 |

|-----------------|---------------------|---------------------|-----------------|

| File<br>Address | 8                   |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                | OPTION              | 81h             |

| 02h             | PCL                 | PCL                 | 82h             |

| 03h             | STATUS              | STATUS              | 83h             |

| 04h             | FSR                 | FSR                 | 84h             |

| 05h             | PORTA               | TRISA               | 85h             |

| 06h             | PORTB               | TRISB               | 86h             |

| 00h             | TOILID              | TRIOD               | 87h             |

| 07h<br>08h      |                     |                     | 88h             |

| 00h             |                     |                     | 89h             |

| 03h<br>0Ah      | PCLATH              | PCLATH              | 8Ah             |

| 0An<br>0Bh      | INTCON              | INTCON              | 8Bh             |

| 0Dh             | PIR1                | PIE1                | 8Ch             |

| 0Ch<br>0Dh      | PIRI                | PIEI                | 8Dh             |

|                 |                     | PCON                |                 |

| 0Eh<br>0Fh      |                     | PCON                | 8Eh             |

|                 |                     |                     | 8Fh             |

| 10h             |                     |                     | 90h             |

| 11h             |                     |                     | 91h             |

| 12h             |                     |                     | 92h             |

| 13h             |                     |                     | 93h             |

| 14h             |                     |                     | 94h             |

| 15h             |                     |                     | 95h             |

| 16h             |                     |                     | 96h             |

| 17h             |                     |                     | 97h             |

| 18h             |                     |                     | 98h             |

| 19h             |                     |                     | 99h             |

| 1Ah             |                     |                     | 9Ah             |

| 1Bh             |                     |                     | 9Bh             |

| 1Ch             |                     |                     | 9Ch             |

| 1Dh             |                     |                     | 9Dh             |

| 1Eh             |                     |                     | 9Eh             |

| 1Fh             | CMCON               | VRCON               | 9Fh             |

| 20h             |                     |                     | A0h             |

|                 | General<br>Purpose  | General<br>Purpose  |                 |

|                 | Register            | Register            |                 |

|                 | 0                   | 5                   | BFh             |

|                 |                     |                     | C0h             |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

| 7Fh             |                     |                     | FFh             |

| , , , , , ,     | Bank 0              | Bank 1              |                 |

|                 |                     |                     |                 |

| Unim            | plemented data me   | mory locations, re  | ad as '0'.      |

| Note 1:         | Not a physical re   | aister              |                 |

|                 |                     |                     |                 |

|                 |                     |                     |                 |

# FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

|                 | 11010002                       |                     | - 17 (          |

|-----------------|--------------------------------|---------------------|-----------------|

| File<br>Address | 3                              |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                           | OPTION              | 81h             |

| 02h             | PCL                            | PCL                 | 82h             |

| 03h             | STATUS                         | STATUS              | 83h             |

| 04h             | FSR                            | FSR                 | 84h             |

| 05h             | PORTA                          | TRISA               | 85h             |

| 06h             | PORTB                          | TRISB               | 86h             |

| 07h             |                                |                     | 87h             |

| 08h             |                                |                     | 88h             |

| 09h             |                                |                     | 89h             |

| 0Ah             | PCLATH                         | PCLATH              | 8Ah             |

| 0Bh             | INTCON                         | INTCON              | 8Bh             |

| 0Ch             | PIR1                           | PIE1                | 8Ch             |

| 0Dh             |                                |                     | 8Dh             |

| 0Eh             |                                | PCON                | 8Eh             |

| 0Fh             |                                |                     | 8Fh             |

| 10h             |                                |                     | 90h             |

| 11h             |                                |                     | 91h             |

| 12h             |                                |                     | 92h             |

| 13h             |                                |                     | 93h             |

| 14h             |                                |                     | 94h             |

| 15h             |                                |                     | 95h             |

| 16h             |                                |                     | 96h             |

| 17h             |                                |                     | 97h             |

| 18h             |                                |                     | 98h             |

| 19h             |                                |                     | 99h             |

| 1Ah             |                                |                     | 9Ah             |

| 1Bh             |                                |                     | 9Bh             |

| 1Ch             |                                |                     | 9Ch             |

| 1Dh             |                                |                     | 9Dh             |

| 1Eh             |                                |                     | 9Eh             |

| 1Fh             | CMCON                          | VRCON               | 9Fh             |

| 20h             | General<br>Purpose<br>Register |                     | A0h             |

| 6Fh             |                                |                     |                 |

| 70h             | General                        |                     | F0h             |

|                 | Purpose<br>Register            | Accesses<br>70h-7Fh |                 |

| 7Fh             | Bank 0                         | Bank 1              | 」 FFh           |

| Unimp           | lemented data mer              | mory locations, rea | ad as '0'.      |

| Note 1:         | Not a physical re              | gister.             |                 |

|                 |                                |                     |                 |

# FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                                         |                     | C10C022A            |                 |  |  |  |

|-----------------------------------------|---------------------|---------------------|-----------------|--|--|--|

| File<br>Address                         | 3                   |                     | File<br>Address |  |  |  |

| 00h                                     | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |  |

| 01h                                     | TMR0                | OPTION              | 81h             |  |  |  |

| 02h                                     | PCL                 | PCL                 | 82h             |  |  |  |

| 03h                                     | STATUS              | STATUS              | 83h             |  |  |  |

| 04h                                     | FSR                 | FSR                 | 84h             |  |  |  |

| 05h                                     | PORTA               | TRISA               | 85h             |  |  |  |

| 06h                                     | PORTB               | TRISB               | 86h             |  |  |  |

| 07h                                     |                     |                     | 87h             |  |  |  |

| 08h                                     |                     |                     | 88h             |  |  |  |

| 09h                                     |                     |                     | 89h             |  |  |  |

| 0Ah                                     | PCLATH              | PCLATH              | 8Ah             |  |  |  |

| 0Bh                                     | INTCON              | INTCON              | 8Bh             |  |  |  |

| 0Ch                                     | PIR1                | PIE1                | 8Ch             |  |  |  |

| 0Dh                                     |                     |                     | 8Dh             |  |  |  |

| 0Eh                                     |                     | PCON                | 8Eh             |  |  |  |

| 0Fh                                     |                     |                     | 8Fh             |  |  |  |

| 10h                                     |                     |                     | 90h             |  |  |  |

| 11h                                     |                     |                     | 91h             |  |  |  |

| 12h                                     |                     |                     | 92h             |  |  |  |

| 13h                                     |                     |                     | 93h             |  |  |  |

| 14h                                     |                     |                     | 94h             |  |  |  |

| 15h                                     |                     |                     | 95h             |  |  |  |

| 16h                                     |                     |                     | 96h             |  |  |  |

| 17h                                     |                     |                     | 97h             |  |  |  |

| 18h                                     |                     |                     | 98h             |  |  |  |

| 19h                                     |                     |                     | 99h             |  |  |  |

| 1Ah                                     |                     |                     | 9Ah             |  |  |  |

| 1Bh                                     |                     |                     | 9Bh             |  |  |  |

| 1Ch                                     |                     |                     | 9Ch             |  |  |  |

| 1Dh                                     |                     |                     | 9Dh             |  |  |  |

| 1Eh                                     |                     |                     | 9Eh             |  |  |  |

| 1Fh                                     | CMCON               | VRCON               | 9Fh             |  |  |  |

| 20h                                     |                     |                     | A0h             |  |  |  |

|                                         | General             | General             | Aon             |  |  |  |

|                                         | Purpose<br>Register | Purpose<br>Register |                 |  |  |  |

|                                         | rtegister           | rtegister           | BFh             |  |  |  |

|                                         |                     |                     | C0h             |  |  |  |

| 0.51                                    |                     |                     |                 |  |  |  |

| 6Fh                                     | 0                   |                     | F0h             |  |  |  |

| 70h                                     | General<br>Purpose  | Accesses            |                 |  |  |  |

| 754                                     | Register            | 70h-7Fh             | FFh             |  |  |  |

| 7Fh                                     | Bank 0              | Bank 1              | → FF11          |  |  |  |

|                                         |                     |                     |                 |  |  |  |

| Unimp                                   | plemented data me   | mory locations, re  | ad as '0'.      |  |  |  |

| <b>Note 1:</b> Not a physical register. |                     |                     |                 |  |  |  |

# 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The Special Function Registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7               | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|---------------|---------------------|--------------------|-------------|--------------|--------------|--------------|-------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                     |                    |             |              |              |              |             |            |                       |                                                |

| 00h     | INDF          | Addressin register) | g this locati      | ion uses co | ntents of FS | SR to addre  | ess data me  | mory (not a | n physical | XXXX XXXX             | XXXX XXXX                                      |

| 01h     | TMR0          | Timer0 Mo           | odule's Reg        | ister       |              |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program 0           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         | —                   | _                  | _           | RA4          | RA3          | RA2          | RA1         | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                 | RB6                | RB5         | RB4          | RB3          | RB2          | RB1         | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h-09h | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 0Ah     | PCLATH        | _                   | _                  | —           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                 | PEIE               | TOIE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | _                   | CMIF               | —           | _            | —            | _            | —           | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 1Fh     | CMCON         | C2OUT               | C1OUT              | —           | _            | CIS          | CM2          | CM1         | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                     |                    |             |              |              |              |             |            |                       |                                                |

| 80h     | INDF          | Addressin register) | g this locati      | on uses co  | ntents of FS | SR to addre  | ess data me  | mory (not a | ı physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                | INTEDG             | TOCS        | TOSE         | PSA          | PS2          | PS1         | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program 0           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |            | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |            | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | —                   | _                  | _           | TRISA4       | TRISA3       | TRISA2       | TRISA1      | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7              | TRISB6             | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1      | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h-89h | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 8Ah     | PCLATH        | —                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram coui  | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                 | PEIE               | T0IE        | INTE         | RBIE         | T0IF         | INTF        | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | —                   | CMIE               | —           | —            | —            | —            | —           | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 8Eh     | PCON          | —                   |                    | _           |              | _            |              | POR         | BOR        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                     |                    |             |              |              |              |             |            | _                     | _                                              |

| 9Fh     | VRCON         | VREN                | VROE               | VRR         | —            | VR3          | VR2          | VR1         | VR0        | 000- 0000             | 000- 0000                                      |

TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown,

${\rm q}$  = value depends on condition, shaded = unimplemented

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved; always maintain these bits clear.

# 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

# REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved                                                                                                          | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x          |  |

|---------|-------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|----------------|----------------|--------------|----------------|--|

|         | IRP                                                                                                               | RP1                                | RP0            | TO             | PD             | Z              | DC           | С              |  |

|         | bit 7                                                                                                             |                                    |                |                |                |                |              | bit 0          |  |

|         |                                                                                                                   |                                    |                |                |                |                |              |                |  |

| bit 7   | -                                                                                                                 | ter Bank Sel                       | -              | d for indirect | addressing     | )              |              |                |  |

|         |                                                                                                                   | , 3 (100h - 1<br>, 1 (00h - FF     |                |                |                |                |              |                |  |

|         |                                                                                                                   | t is reserved                      |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |                |  |

| bit 6-5 |                                                                                                                   | Register Ban                       |                |                | -              |                |              |                |  |

|         |                                                                                                                   | 1 (80h - FFh                       |                |                |                |                |              |                |  |

|         |                                                                                                                   | 0 (00h - 7Fh                       |                |                |                |                |              |                |  |

|         | Each bank<br>clear.                                                                                               | is 128 bytes                       | 5. The RP1 t   | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit   |  |

| bit 4   | TO: Time-c                                                                                                        | out bit                            |                |                |                |                |              |                |  |

|         |                                                                                                                   | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |                |  |

|         |                                                                                                                   | time-out oc                        |                | ,              |                |                |              |                |  |

| bit 3   | PD: Power                                                                                                         | -down bit                          |                |                |                |                |              |                |  |

|         | -                                                                                                                 | ower-up or b<br>cution of the      | -              |                | n              |                |              |                |  |

| bit 2   | Z: Zero bit                                                                                                       |                                    |                |                |                |                |              |                |  |

|         |                                                                                                                   | sult of an arit<br>sult of an arit |                |                |                | )              |              |                |  |

| bit 1   |                                                                                                                   |                                    |                | • •            |                |                | )(for borrow | the polarity   |  |

|         | <b>DC</b> : Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(for borrow the polarity is reversed) |                                    |                |                |                |                |              |                |  |

|         |                                                                                                                   | -out from the                      |                |                |                | rred           |              |                |  |

|         |                                                                                                                   | ry-out from th                     |                |                |                |                |              |                |  |

| bit 0   | •                                                                                                                 | orrow bit (AD                      |                |                |                |                |              |                |  |

|         | •                                                                                                                 | -out from the<br>ry-out from th    | -              |                |                |                |              |                |  |

|         | Note:                                                                                                             | For borrow t                       | he polarity i  | s reversed.    | A subtraction  | on is execut   | ed by addin  | g the two's    |  |

|         |                                                                                                                   | complement                         |                |                |                |                |              | s, this bit is |  |

|         |                                                                                                                   | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg     | ister.       |                |  |

|         | Legend:                                                                                                           | L. L. 14                           |                |                |                |                | hit on all   | 0              |  |

|         | R = Reada                                                                                                         |                                    |                | ritable bit    |                | •              | bit, read as |                |  |

|         | - n = Value                                                                                                       | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown         |  |

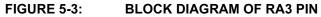

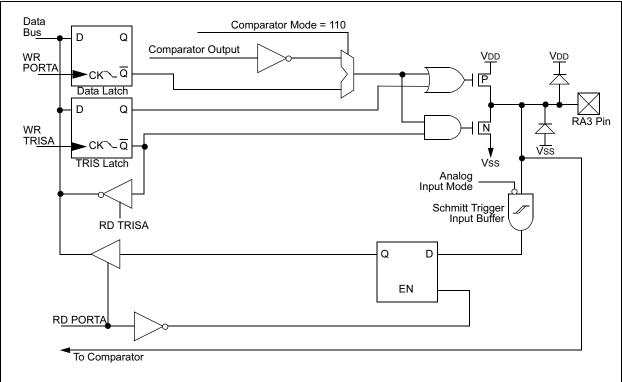

# TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

# TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

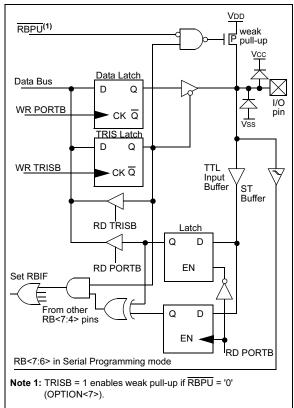

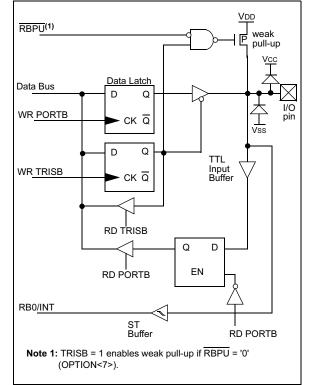

# 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a High Impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A \ typical$ ). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (e.g., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

## FIGURE 5-5: BLOCK DIAGRAM OF RB<7:4> PINS

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes.)

| Note: | If a change on the I/O pin should occur       |  |  |

|-------|-----------------------------------------------|--|--|

|       | when the read operation is being executed     |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |

|       | rupt flag may not get set.                    |  |  |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

| <b>TABLE 7-1</b> : | REGISTERS ASSOCIATED WITH COMPARATOR MODULE |

|--------------------|---------------------------------------------|

|--------------------|---------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 1Fh     | CMCON  | C2OUT | C10UT |       | _      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 9Fh     | VRCON  | VREN  | VROE  | VRR   |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch     | PIR1   | _     | CMIF  | _     | _      | _      | _      | _      | _      | -0              | -0                              |

| 8Ch     | PIE1   | _     | CMIE  | _     | _      | _      | _      | _      | _      | -0              | -0                              |

| 85h     | TRISA  |       |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as "0"

-

# TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | MCLR Reset during<br><u>normal</u> operation     MCLR Reset during<br>SLEEP     WDT Reset     Brown-out Reset <sup>(1)</sup> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | นนนน นนนน                                                                                                                    | นนนน นนนน                                                                                                         |

| INDF     | 00h     |                | _                                                                                                                            | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                    | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                    | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                     | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                    | <u>uuuu</u> uuuu                                                                                                  |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                       | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | սսսս սսսս                                                                                                                    | սսսս սսսս                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                      | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                       | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                    | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                           | -q <sup>(2,5)</sup>                                                                                               |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                    | սսսս սսսս                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                       | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                    | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                           | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                          | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                    | uuu- uuuu                                                                                                         |

# TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

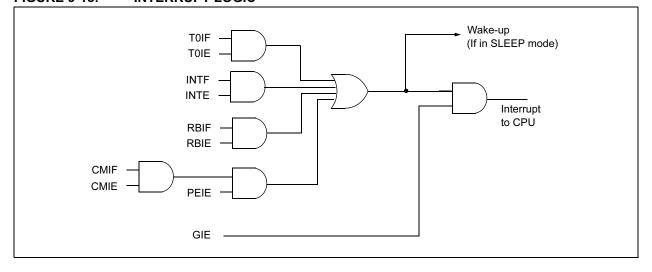

# 9.5 Interrupts

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

| TABLE 10-2: PIC16C62X INSTRUCTION SET |

|---------------------------------------|

|---------------------------------------|

| Mnemonic  | ,        | Description                  |       | 14-Bit Opcode |      |      |      | Status   | Notes |  |

|-----------|----------|------------------------------|-------|---------------|------|------|------|----------|-------|--|

| Operands  |          |                              |       | MSb           | )    | LSb  |      | Affected |       |  |

| BYTE-ORI  | IENTED I | FILE REGISTER OPERATIONS     |       |               |      |      |      |          |       |  |

| ADDWF     | f, d     | Add W and f                  | 1     | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |  |

| ANDWF     | f, d     | AND W with f                 | 1     | 00            | 0101 | dfff | ffff | Z        | 1,2   |  |

| CLRF      | f        | Clear f                      | 1     | 00            | 0001 | lfff | ffff | Z        | 2     |  |

| CLRW      | -        | Clear W                      | 1     | 00            | 0001 | 0000 | 0011 | Z        |       |  |

| COMF      | f, d     | Complement f                 | 1     | 00            | 1001 | dfff | ffff | Z        | 1,2   |  |

| DECF      | f, d     | Decrement f                  | 1     | 00            | 0011 | dfff | ffff | Z        | 1,2   |  |

| DECFSZ    | f, d     | Decrement f, Skip if 0       | 1(2)  | 00            | 1011 | dfff | ffff |          | 1,2,3 |  |

| INCF      | f, d     | Increment f                  | 1     | 00            | 1010 | dfff | ffff | Z        | 1,2   |  |

| INCFSZ    | f, d     | Increment f, Skip if 0       | 1(2)  | 00            | 1111 | dfff | ffff |          | 1,2,3 |  |

| IORWF     | f, d     | Inclusive OR W with f        | 1     | 00            | 0100 | dfff | ffff | Z        | 1,2   |  |

| MOVF      | f, d     | Move f                       | 1     | 00            | 1000 | dfff | ffff | Z        | 1,2   |  |

| MOVWF     | f        | Move W to f                  | 1     | 00            | 0000 | lfff | ffff |          |       |  |

| NOP       | -        | No Operation                 | 1     | 00            | 0000 | 0xx0 | 0000 |          |       |  |

| RLF       | f, d     | Rotate Left f through Carry  | 1     | 00            | 1101 | dfff | ffff | С        | 1,2   |  |

| RRF       | f, d     | Rotate Right f through Carry | 1     | 00            | 1100 | dfff | ffff | С        | 1,2   |  |

| SUBWF     | f, d     | Subtract W from f            | 1     | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |  |

| SWAPF     | f, d     | Swap nibbles in f            | 1     | 00            | 1110 | dfff | ffff |          | 1,2   |  |

| XORWF     | f, d     | Exclusive OR W with f        | 1     | 00            | 0110 | dfff | ffff | Z        | 1,2   |  |

| BIT-ORIEN | NTED FIL | E REGISTER OPERATIONS        |       |               |      |      |      |          |       |  |

| BCF       | f, b     | Bit Clear f                  | 1     | 01            | 00bb | bfff | ffff |          | 1,2   |  |

| BSF       | f, b     | Bit Set f                    | 1     | 01            | 01bb | bfff | ffff |          | 1,2   |  |

| BTFSC     | f, b     | Bit Test f, Skip if Clear    | 1 (2) | 01            | 10bb | bfff | ffff |          | 3     |  |

| BTFSS     | f, b     | Bit Test f, Skip if Set      | 1 (2) | 01            | 11bb | bfff | ffff |          | 3     |  |

| LITERAL / | AND COI  | NTROL OPERATIONS             |       |               |      |      |      |          |       |  |

| ADDLW     | k        | Add literal and W            | 1     | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |  |

| ANDLW     | k        | AND literal with W           | 1     | 11            | 1001 | kkkk | kkkk | Z        |       |  |

| CALL      | k        | Call subroutine              | 2     | 10            | 0kkk | kkkk | kkkk |          |       |  |

| CLRWDT    | -        | Clear Watchdog Timer         | 1     | 00            | 0000 | 0110 | 0100 | TO,PD    |       |  |

| GOTO      | k        | Go to address                | 2     | 10            | 1kkk | kkkk | kkkk |          |       |  |

| IORLW     | k        | Inclusive OR literal with W  | 1     | 11            | 1000 | kkkk | kkkk | Z        |       |  |

| MOVLW     | k        | Move literal to W            | 1     | 11            | 00xx | kkkk | kkkk |          |       |  |

| RETFIE    | -        | Return from interrupt        | 2     | 00            | 0000 | 0000 | 1001 |          |       |  |

| RETLW     | k        | Return with literal in W     | 2     | 11            | 01xx | kkkk | kkkk |          |       |  |

| RETURN    | -        | Return from Subroutine       | 2     | 00            | 0000 | 0000 | 1000 |          |       |  |

| SLEEP     | -        | Go into Standby mode         | 1     | 00            | 0000 | 0110 | 0011 | TO,PD    |       |  |

| SUBLW     | k        | Subtract W from literal      | 1     | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |  |

| XORLW     | k        | Exclusive OR literal with W  | 1     | 11            | 1010 | kkkk | kkkk | Z        |       |  |

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**2:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BTFSS            | Bit Test f, Skip if Set                                                     | CALL             | Call Subroutine                                                         |

|------------------|-----------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BTFSS f,b                                                   | Syntax:          | [ <i>label</i> ] CALL k                                                 |

| Operands:        | $0 \leq f \leq 127$                                                         | Operands:        | $0 \leq k \leq 2047$                                                    |

|                  | 0 ≤ b < 7                                                                   | Operation:       | $(PC)$ + 1 $\rightarrow$ TOS,                                           |

| Operation:       | skip if (f <b>) = 1</b>                                                     |                  | $k \rightarrow PC < 10:0>$ ,<br>(PCLATH<4:3>) $\rightarrow PC < 12:11>$ |

| Status Affected: | None                                                                        | Status Affected: | None                                                                    |

| Encoding:        | 01 11bb bfff ffff                                                           | Encoding:        | 10 0kkk kkkk kkkk                                                       |

| Description:     | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped. | Description:     | Call Subroutine. First, return                                          |

|                  | If bit 'b' is '1', then the next instruc-                                   | Decomption       | address (PC+1) is pushed onto                                           |

|                  | tion fetched during the current                                             |                  | the stack. The eleven bit immedi-                                       |

|                  | instruction execution, is discarded and a NOP is executed instead.          |                  | ate address is loaded into PC bits <10:0>. The upper bits of the PC     |

|                  | making this a two-cycle instruction.                                        |                  | are loaded from PCLATH. CALL is                                         |

| Words:           | 1                                                                           |                  | a two-cycle instruction.                                                |

| Cycles:          | 1(2)                                                                        | Words:           | 1                                                                       |

| Example          | here bifss FLAG,1                                                           | Cycles:          | 2                                                                       |

|                  | FALSE GOTO PROCESS_CO<br>TRUE • DE                                          | Example          | HERE CALL<br>THER                                                       |

|                  | ·                                                                           |                  | E                                                                       |

|                  | •<br>Defens lastruction                                                     |                  | Before Instruction                                                      |

|                  | Before Instruction<br>PC = address HERE                                     |                  | PC = Address HERE<br>After Instruction                                  |

|                  | After Instruction                                                           |                  | PC = Address THERE                                                      |

|                  | if FLAG<1> = 0,<br>PC = address FALSE                                       |                  | TOS = Address HERE+1                                                    |

|                  | if FLAG<1> = 1,                                                             |                  |                                                                         |

|                  | PC = address TRUE                                                           | CLRF             | Clear f                                                                 |

|                  |                                                                             | Syntax:          | [label] CLRF f                                                          |

|                  |                                                                             | Operands:        | $0 \leq f \leq 127$                                                     |

|                  |                                                                             | Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$   |

|                  |                                                                             | Status Affected: | Z                                                                       |

|                  |                                                                             | Encoding:        | 00 0001 1fff ffff                                                       |

|                  |                                                                             | Description:     | The contents of register 'f' are cleared and the Z bit is set.          |

|                  |                                                                             | Words:           | 1                                                                       |

|                  |                                                                             | Cycles:          | 1                                                                       |

|                  |                                                                             | Example          | CLRF FLAG_REG                                                           |

|                  |                                                                             | •                | Before Instruction                                                      |

|                  |                                                                             |                  | FLAG_REG = 0x5A                                                         |

|                  |                                                                             |                  | After Instruction<br>FLAG REG = 0x00                                    |

|                  |                                                                             |                  | Z = 1                                                                   |

# 12.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                 | 40° to +125°C                  |

|----------------------------------------------------------------------------------------------------------------|--------------------------------|

| Storage Temperature                                                                                            | 65° to +150°C                  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | 0.6V to VDD +0.6V              |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.5V                     |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                      |

| Voltage on RA4 with respect to Vss                                                                             |                                |

| Total power Dissipation (Note 1)                                                                               | 1.0W                           |

| Maximum Current out of Vss pin                                                                                 | 300 mA                         |

| Maximum Current into VDD pin                                                                                   | 250 mA                         |

| Input Clamp Current, Iк (Vi <0 or Vi> VDD)                                                                     | ±20 mA                         |

| Output Clamp Current, Iок (Vo <0 or Vo>VoD)                                                                    | ±20 mA                         |

| Maximum Output Current sunk by any I/O pin                                                                     | 25 mA                          |

| Maximum Output Current sourced by any I/O pin                                                                  | 25 mA                          |

| Maximum Current sunk by PORTA and PORTB                                                                        | 200 mA                         |

| Maximum Current sourced by PORTA and PORTB                                                                     | 200 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | x IOH} + $\Sigma$ (VOI x IOL). |

2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended) (CONT.)

| PIC16C62XA<br>PIC16LC62XA |     |                                   |     | ating te<br>dard O<br>ating te | perati                  | ature -4<br>-4<br>ng Con<br>ature -4<br>-4 | ditions (unless otherwise stated)<br>$40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and<br>$0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and<br>$40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extended<br>ditions (unless otherwise stated)<br>$40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and<br>$0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and<br>$0^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extended |

|---------------------------|-----|-----------------------------------|-----|--------------------------------|-------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|