Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 18-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc620a-04e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16C62X devices are 18 and 20-Pin ROM/ EPROM-based members of the versatile PICmicro<sup>®</sup> family of low cost, high performance, CMOS, fullystatic, 8-bit microcontrollers.

All PICmicro microcontrollers employ an advanced RISC architecture. The PIC16C62X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16C62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16C620A, PIC16C621A and PIC16CR620A have 96 bytes of RAM. The PIC16C622(A) has 128 bytes of RAM. Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16C62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16C62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and RESET.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost effective One-Time-Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16C62X midrange microcontroller families.

A simplified block diagram of the PIC16C62X is shown in Figure 3-1.

The PIC16C62X series fits perfectly in applications ranging from battery chargers to low power remote sensors. The EPROM technology makes

customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C62X very versatile.

## 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to PIC16C62X family of devices (Appendix B). The PIC16C62X family fills the niche for users wanting to migrate up from the PIC16C5X family and not needing various peripheral features of other members of the PIC16XX mid-range microcontroller family.

## 1.2 Development Support

The PIC16C62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. Third Party "C" compilers are also available.

NOTES:

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin # | I/O/P Type             | Buffer<br>Type        | Description                                                                                                                                                                                                         |

|--------------|-------------------|---------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18            | I                      | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                               |

| OSC2/CLKOUT  | 15                | 17            | 0                      | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin out-<br>puts CLKOUT, which has 1/4 the frequency of OSC1<br>and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4             | I/P                    | ST                    | Master Clear (Reset) input/programming voltage input.<br>This pin is an Active Low Reset to the device.                                                                                                             |

|              |                   |               |                        |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |

| RA0/AN0      | 17                | 19            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA1/AN1      | 18                | 20            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA2/AN2/VREF | 1                 | 1             | I/O                    | ST                    | Analog comparator input or VREF output                                                                                                                                                                              |

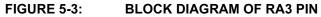

| RA3/AN3      | 2                 | 2             | I/O                    | ST                    | Analog comparator input /output                                                                                                                                                                                     |

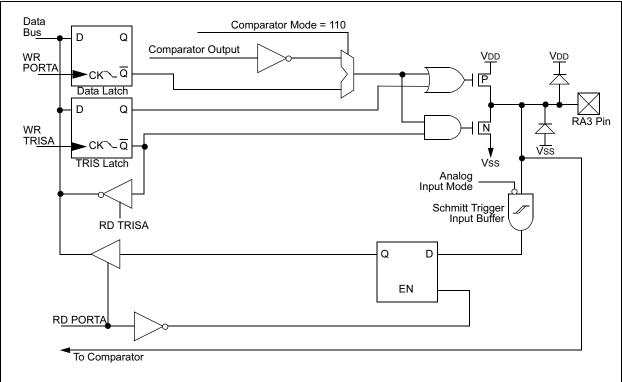

| RA4/T0CKI    | 3                 | 3             | I/O                    | ST                    | Can be selected to be the clock input to the Timer<br>timer/counter or a comparator output. Output is<br>open drain type.                                                                                           |

|              |                   |               |                        |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                                 |

| RB0/INT      | 6                 | 7             | I/O                    | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an externa interrupt pin.                                                                                                                                                           |

| RB1          | 7                 | 8             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB2          | 8                 | 9             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB3          | 9                 | 10            | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB4          | 10                | 11            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB5          | 11                | 12            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB6          | 12                | 13            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock                                                                                                                                                                   |

| RB7          | 13                | 14            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                   |

| Vss          | 5                 | 5,6           | Р                      |                       | Ground reference for logic and I/O pins.                                                                                                                                                                            |

| Vdd          | 14                | 15,16         | Р                      | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                             |

| Legend:      | O = out<br>— = No | •             | I/O = inp<br>I = Input | ut/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                             |

TTL = TTL input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

## 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

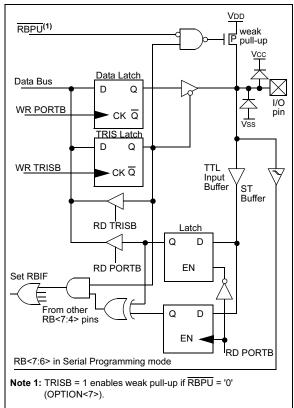

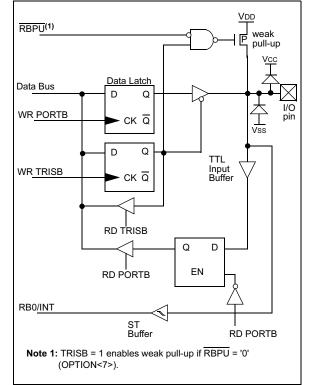

## 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a High Impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A \ typical$ ). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (e.g., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

#### FIGURE 5-5: BLOCK DIAGRAM OF RB<7:4> PINS

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes.)

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

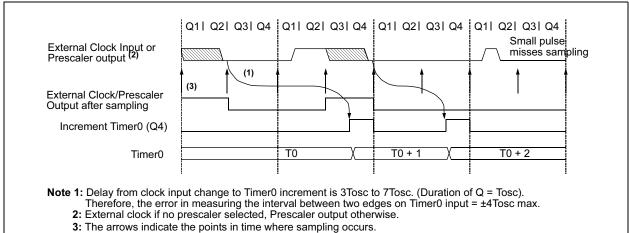

## 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

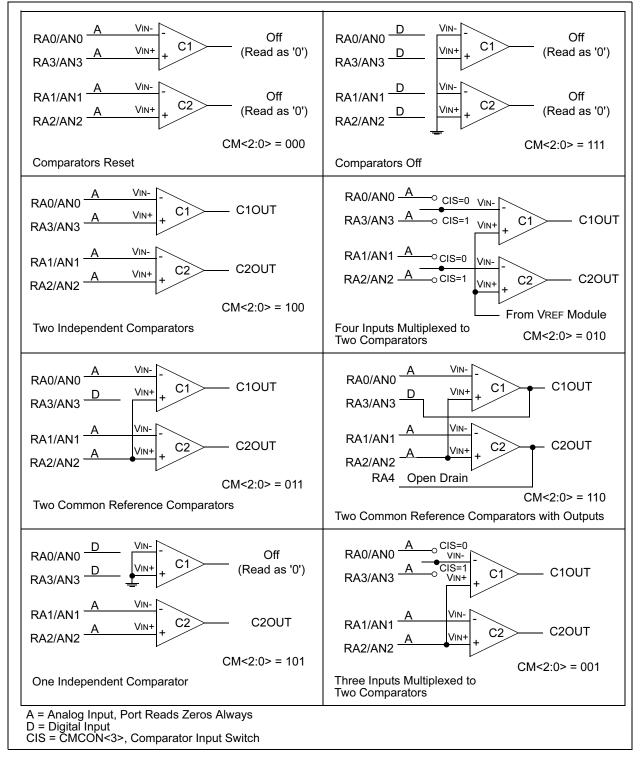

### 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

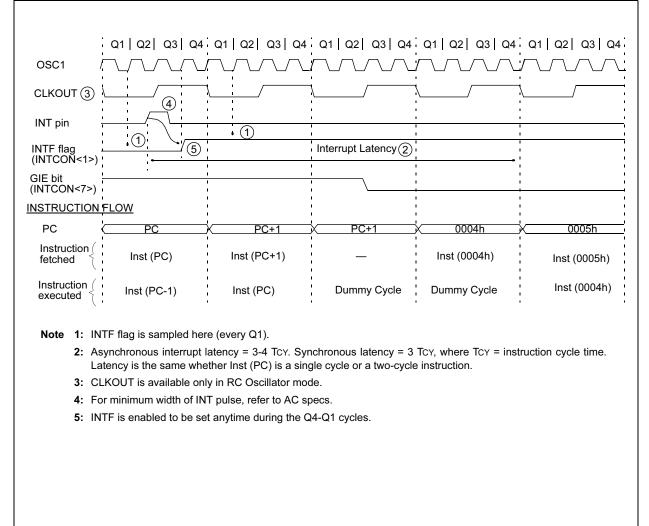

#### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

#### 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

#### FIGURE 9-16: INT PIN INTERRUPT TIMING

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test, Skip if Clear                                                   |

|------------------|---------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      | Syntax:          | [label]BTFSC f,b                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$       |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                   |

| Status Affected: | None                                                                | Status Affected: | None                                                                      |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                         |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0', then the                               |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0', then the next instruc- |

| Cycles:          | 1                                                                   |                  | tion fetched during the current                                           |

| Example          | BCF FLAG_REG, 7                                                     |                  | instruction execution is discarded,                                       |

|                  | Before Instruction<br>FLAG_REG = 0xC7                               |                  | and a NOP is executed instead,<br>making this a two-cycle instruction.    |

|                  | After Instruction                                                   | Words:           | 1                                                                         |

|                  | FLAG_REG = 0x47                                                     | Cycles:          | 1(2)                                                                      |

|                  |                                                                     | Example          | here btfsc <b>FLAG,1</b><br>false goto <b>process co</b>                  |

| BSF              | Bit Set f                                                           |                  | TRUE DE                                                                   |

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |                  | •                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                  | Before Instruction<br>PC = address HERE                                   |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |                  | After Instruction<br>if FLAG<1> = 0.                                      |

| Status Affected: | None                                                                |                  | PC = address TRUE                                                         |

| Encoding:        | 01 01bb bfff ffff                                                   |                  | if FLAG<1>=1,<br>PC = address FALSE                                       |

| Description:     | Bit 'b' in register 'f' is set.                                     |                  | PC = address FALSE                                                        |

| Words:           | 1                                                                   |                  |                                                                           |

| Cycles:          | 1                                                                   |                  |                                                                           |

| Example          | BSF FLAG_REG, 7                                                     |                  |                                                                           |

Before Instruction FLAG\_REG = 0x0A After Instruction

FLAG\_REG = 0x8A

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$<br>d $\in$ [0,1]                                                                                                                                                                                                                                                                                                     |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                                      |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                                   |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                     |

|                  | $\begin{array}{rcl} PC &=& address \ {\tt HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \ {\tt CONTINUE} \\ \mbox{if CNT} \neq& 0, \\ PC &=& address \ {\tt HERE} + 1 \\ \end{array}$                                                                                                 |

| GOTO             | Unconditional Branch                                                                                                                                                                                                                                                                                                                   |

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                                |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                                                                                                                     |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |

| Encoding:        | 10 1kkk kkkk kkkk                                                                                                                                                                                                                                                                                                                      |

| Description:     | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction.                                                                                                                                      |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |

| Cycles:          | 2                                                                                                                                                                                                                                                                                                                                      |

| Example          | GOTO THERE                                                                                                                                                                                                                                                                                                                             |

|                  | After Instruction<br>PC = Address THERE                                                                                                                                                                                                                                                                                                |

| INCF             | Increment f                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |

| Status Affected: | Z                                                                                                                                                                      |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                      |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |

| Words:           | 1                                                                                                                                                                      |

| Cycles:          | 1                                                                                                                                                                      |

| Example          | INCF CNT, 1                                                                                                                                                            |

|                  | Before Instruction $CNT$ =0xFFZ=0After Instruction $CNT$ =0x00Z=1                                                                                                      |

NOTES:

### 12.3 DC CHARACTERISTICS: PIC16CR62XA-04 (Commercial, Industrial, Extended) PIC16CR62XA-20 (Commercial, Industrial, Extended) PIC16LCR62XA-04 (Commercial, Industrial, Extended)

| PIC16CR62XA-04<br>PIC16CR62XA-20 |       |                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |            |                                                      |                                                                                                                   |  |  |  |

|----------------------------------|-------|-----------------------------------------------|------------------------------------------------------|------------|------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIC16L0                          | CR62X | <b>Q-04</b>                                   |                                                      |            |            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                   |  |  |  |

| Param.<br>No.                    | Sym   | Characteristic                                | Min                                                  | Тур†       | Мах        | Units                                                | Conditions                                                                                                        |  |  |  |

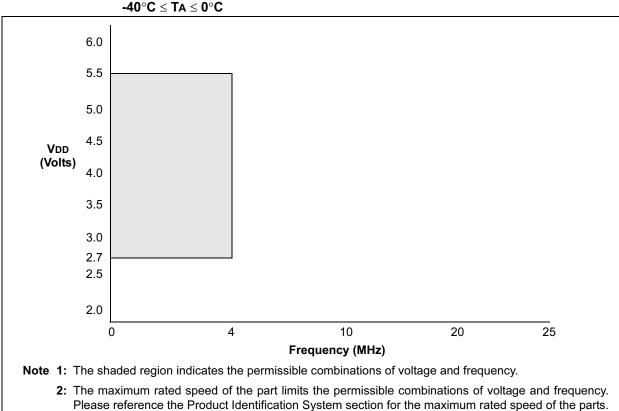

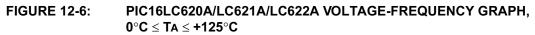

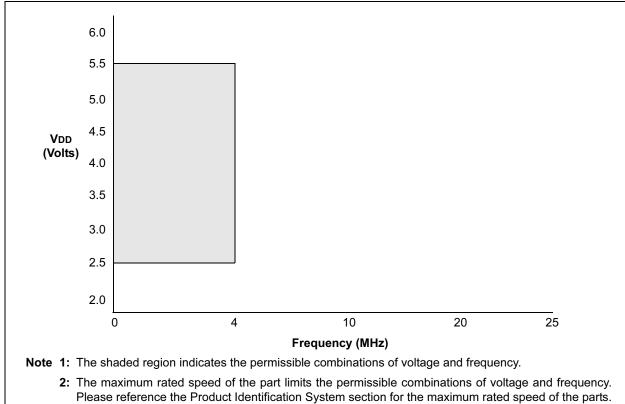

| D001                             | Vdd   | Supply Voltage                                | 3.0                                                  | —          | 5.5        | V                                                    | See Figures 12-7, 12-8, 12-9                                                                                      |  |  |  |

| D001                             | Vdd   | Supply Voltage                                | 2.5                                                  | —          | 5.5        | V                                                    | See Figures 12-7, 12-8, 12-9                                                                                      |  |  |  |

| D002                             | Vdr   | RAM Data Retention<br>Voltage <sup>(1)</sup>  |                                                      | 1.5*       |            | V                                                    | Device in SLEEP mode                                                                                              |  |  |  |

| D002                             | Vdr   | RAM Data Retention<br>Voltage <sup>(1)</sup>  | _                                                    | 1.5*       | —          | V                                                    | Device in SLEEP mode                                                                                              |  |  |  |

| D003                             | VPOR  | VDD start voltage to<br>ensure Power-on Reset |                                                      | Vss        | _          | V                                                    | See section on Power-on Reset for details                                                                         |  |  |  |

| D003                             | VPOR  | VDD start voltage to<br>ensure Power-on Reset | —                                                    | Vss        | —          | V                                                    | See section on Power-on Reset for details                                                                         |  |  |  |

| D004                             | SVDD  | VDD rise rate to ensure<br>Power-on Reset     | 0.05*                                                | —          | —          | V/ms                                                 | See section on Power-on Reset for details                                                                         |  |  |  |

| D004                             | SVDD  | VDD rise rate to ensure<br>Power-on Reset     | 0.05*                                                | —          | —          | V/ms                                                 | See section on Power-on Reset for details                                                                         |  |  |  |

| D005                             | VBOR  | Brown-out Detect Voltage                      | 3.7                                                  | 4.0        | 4.35       | V                                                    | BOREN configuration bit is cleared                                                                                |  |  |  |

| D005                             | VBOR  | Brown-out Detect Voltage                      | 3.7                                                  | 4.0        | 4.35       | V                                                    | BOREN configuration bit is cleared                                                                                |  |  |  |

| D010                             | Idd   | Supply Current <sup>(2)</sup>                 | _                                                    | 1.2<br>500 | 1.7<br>900 | mA<br>μA                                             | Fosc = 4 MHz, VDD = 5.5V, WDT disabled, XT mode,<br>(Note 4)*<br>Fosc = 4 MHz, VDD = 3.0V, WDT disabled, XT mode, |  |  |  |

|                                  |       |                                               | _                                                    | 1.0        | 2.0        | mA                                                   | (Note 4)<br>Fosc = 10 MHz, VDD = 3.0V, WDT disabled, HS mode,<br>(Note 6)                                         |  |  |  |

|                                  |       |                                               | —                                                    | 4.0        | 7.0        | mA                                                   | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*, HS                                                                      |  |  |  |

|                                  |       |                                               | —                                                    | 3.0        | 6.0        | mA                                                   | mode                                                                                                              |  |  |  |

|                                  |       |                                               |                                                      | 35         | 70         | μA                                                   | Fosc = 20 MHz, VDD = 4.5V, WDT disabled, HS mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled, LP mode              |  |  |  |

| D010                             | IDD   | Supply Current <sup>(2)</sup>                 | —                                                    | 1.2        | 1.7        | mA                                                   | Fosc = 4.0 MHz, VDD = 5.5V, WDT disabled, XT<br>mode, ( <b>Note 4</b> )*                                          |  |  |  |

|                                  |       |                                               | —                                                    | 400        | 800        | μA                                                   | Fosc = 4.0 MHz, VDD = 2.5V, WDT disabled, XT mode (Note 4)                                                        |  |  |  |

|                                  |       |                                               | —                                                    | 35         | 70         | μA                                                   | Fosc = 32 kHz, VDD = 2.5V, WDT disabled, LP mode                                                                  |  |  |  |

## 12.5 DC CHARACTERISTICS: PIC16C620A/C621A/C622A-40<sup>(7)</sup> (Commercial) PIC16CR620A-40<sup>(7)</sup> (Commercial)

| DC CH            | IARAC | TERISTICS                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |      |                 |      |                                                                |  |  |

|------------------|-------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|------|----------------------------------------------------------------|--|--|

| Param<br>No. Sym |       | Characteristic                             | Min                                                                                                                                | Тур† | Мах             | Unit | Conditions                                                     |  |  |

|                  | VIL   | Input Low Voltage                          |                                                                                                                                    |      |                 |      |                                                                |  |  |

|                  |       | I/O ports                                  |                                                                                                                                    |      |                 |      |                                                                |  |  |

| D030             |       | with TTL buffer                            | Vss                                                                                                                                | _    | 0.8V<br>0.15Vdd | V    | VDD = 4.5V to 5.5V, otherwise                                  |  |  |

| D031             |       | with Schmitt Trigger input                 | Vss                                                                                                                                |      | 0.2VDD          | V    |                                                                |  |  |

| D032             |       | MCLR, RA4/T0CKI, OSC1<br>(in RC mode)      | Vss                                                                                                                                | —    | 0.2Vdd          | V    | (Note 1)                                                       |  |  |

| D033             |       | OSC1 (in XT and HS)                        | Vss                                                                                                                                | _    | 0.3VDD          | V    |                                                                |  |  |

|                  |       | OSC1 (in LP)                               | Vss                                                                                                                                | _    | 0.6Vdd - 1.0    | V    |                                                                |  |  |

|                  | Vih   | Input High Voltage                         |                                                                                                                                    |      |                 |      |                                                                |  |  |

|                  |       | I/O ports                                  |                                                                                                                                    |      |                 |      |                                                                |  |  |

| D040             |       | with TTL buffer                            | 2.0V                                                                                                                               | —    | Vdd             | V    | VDD = 4.5V to 5.5V, otherwise                                  |  |  |

|                  |       |                                            | 0.25 VDD + 0.8                                                                                                                     |      | Vdd             |      |                                                                |  |  |

| D041             |       | with Schmitt Trigger input                 | 0.8 VDD                                                                                                                            |      | Vdd             |      |                                                                |  |  |

| D042             |       | MCLR RA4/T0CKI                             | 0.8 VDD                                                                                                                            | —    | Vdd             | V    |                                                                |  |  |

| D043             |       | OSC1 (XT, HS and LP)                       | 0.7 Vdd                                                                                                                            | —    | Vdd             | V    |                                                                |  |  |

| D043A            |       | OSC1 (in RC mode)                          | 0.9 VDD                                                                                                                            |      |                 |      | (Note 1)                                                       |  |  |

| D070             | IPURB | PORTB Weak Pull-up Current                 | 50                                                                                                                                 | 200  | 400             | μA   | VDD = 5.0V, VPIN = VSS                                         |  |  |

|                  | lı∟   | Input Leakage Current <sup>(2, 3)</sup>    |                                                                                                                                    |      |                 |      |                                                                |  |  |

|                  |       | I/O ports (except PORTA)                   |                                                                                                                                    |      | ±1.0            | μA   | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                |  |  |

| D060             |       | PORTA                                      | —                                                                                                                                  | —    | ±0.5            | μA   | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                |  |  |

| D061             |       | RA4/T0CKI                                  | —                                                                                                                                  | _    | ±1.0            | μA   | $Vss \le VPIN \le VDD$                                         |  |  |

| D063             |       | OSC1, MCLR                                 | _                                                                                                                                  | _    | ±5.0            | μA   | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration    |  |  |

|                  | Vol   | Output Low Voltage                         |                                                                                                                                    |      |                 |      |                                                                |  |  |

| D080             |       | I/O ports                                  | _                                                                                                                                  | _    | 0.6             | V    | IOL = 8.5 mA, VDD = 4.5V, -40° to +85°C                        |  |  |

|                  |       |                                            | _                                                                                                                                  | —    | 0.6             | V    | IOL = 7.0 mA, VDD = 4.5V, +125°C                               |  |  |

| D083             |       | OSC2/CLKOUT (RC only)                      | _                                                                                                                                  | —    | 0.6             | V    | IOL = 1.6 mA, VDD = 4.5V, -40° to +85°C                        |  |  |

|                  |       |                                            |                                                                                                                                    |      | 0.6             | V    | IOL = 1.2 mA, VDD = 4.5V, +125°C                               |  |  |

|                  | Vон   | Output High Voltage <sup>(3)</sup>         |                                                                                                                                    |      |                 |      |                                                                |  |  |

| D090             |       | I/O ports (except RA4)                     | VDD-0.7                                                                                                                            | —    | —               | V    | IOH = -3.0 mA, VDD = 4.5V, -40° to +85°C                       |  |  |

|                  |       |                                            | VDD-0.7                                                                                                                            | _    | —               | V    | ІОН = -2.5 mA, VDD = 4.5V, +125°C                              |  |  |

| D092             |       | OSC2/CLKOUT (RC only)                      | VDD-0.7                                                                                                                            | _    | —               | V    | IOH = -1.3 mA, VDD = 4.5V, -40° to +85°C                       |  |  |

|                  |       |                                            | VDD-0.7                                                                                                                            | -    | —               | V    | Іон = -1.0 mA, Vdd = 4.5V, +125°С                              |  |  |

| *D150            | Vod   | Open Drain High Voltage                    |                                                                                                                                    |      | 8.5             | V    | RA4 pin                                                        |  |  |

|                  |       | Capacitive Loading Specs on<br>Output Pins |                                                                                                                                    |      |                 |      |                                                                |  |  |

| D100             | Cosc2 | OSC2 pin                                   |                                                                                                                                    |      | 15              | pF   | In XT, HS and LP modes when external clock used to drive OSC1. |  |  |

| D101             | Cio   | All I/O pins/OSC2 (in RC mode)             |                                                                                                                                    |      | 50              | pF   |                                                                |  |  |

|                  |       | parameters are characterized but not       | <u> </u>                                                                                                                           | 1    | ~~              | ۳.   |                                                                |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in bi-impedance state and tied to VDD or VSS.

mode, with all I/O pins in hi-impedance state and tied to VDD or VSs.

For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/ 2REXT (mA) with REXT in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

7: See Section 12.1 and Section 12.3 for 16C62X and 16CR62X devices for operation between 20 MHz and 40 MHz for valid modified characteristics.

| Parameter<br>No. | Sym          | Characteristic                                               | Min                                | Тур†    | Max        | Units    | Conditions                                                   |

|------------------|--------------|--------------------------------------------------------------|------------------------------------|---------|------------|----------|--------------------------------------------------------------|

| 10*              | TosH2ckL     | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                              |                                    | 75<br>— | 200<br>400 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 11*              | TosH2ck<br>H | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                              |                                    | 75<br>— | 200<br>400 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 12*              | TckR         | CLKOUT rise time <sup>(1)</sup>                              |                                    | 35<br>— | 100<br>200 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 13*              | TckF         | CLKOUT fall time <sup>(1)</sup>                              |                                    | 35<br>— | 100<br>200 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 14*              | TckL2ioV     | CLKOUT ↓ to Port out valid <sup>(1)</sup>                    | _                                  | —       | 20         | ns       |                                                              |

| 15*              | TioV2ckH     | Port in valid before CLKOUT ↑ <sup>(1)</sup>                 | Tosc +200<br>ns<br>Tosc +400<br>ns | —       | _          | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 16*              | TckH2iol     | Port in hold after CLKOUT ↑ <sup>(1)</sup>                   | 0                                  | —       |            | ns       |                                                              |

| 17*              | TosH2ioV     | OSC1↑ (Q1 cycle) to Port out valid                           |                                    | 50      | 150<br>300 | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 18*              | TosH2iol     | OSC1↑ (Q2 cycle) to Port input<br>invalid (I/O in hold time) | 100<br>200                         | _       |            | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 19*              | TioV2osH     | Port input valid to OSC1↑ (I/O in setup time)                | 0                                  | —       | _          | ns       |                                                              |

| 20*              | TioR         | Port output rise time                                        | _                                  | 10<br>— | 40<br>80   | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 21*              | TioF         | Port output fall time                                        | _                                  | 10<br>— | 40<br>80   | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 22*              | Tinp         | RB0/INT pin high or low time                                 | 25<br>40                           | _       | _          | ns<br>ns | PIC16C62X(A)<br>PIC16LC62X(A)<br>PIC16CR62XA<br>PIC16LCR62XA |

| 23               | Trbp         | RB<7:4> change interrupt high or<br>low time                 | Тсү                                |         |            | ns       |                                                              |

## TABLE 12-4: CLKOUT AND I/O TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

## 13.0 DEVICE CHARACTERIZATION INFORMATION

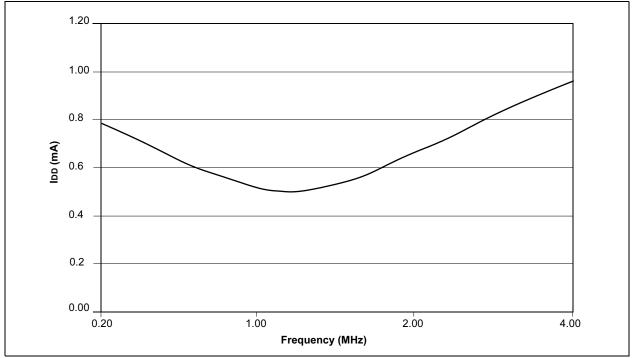

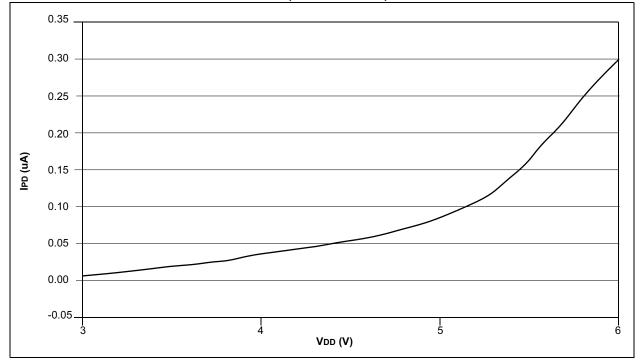

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables, the data presented is outside specified operating range (e.g., outside specified VDD range). This is for information only and devices will operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution, while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

FIGURE 13-1: IDD VS. FREQUENCY (XT MODE, VDD = 5.5V)

FIGURE 13-2: PIC16C622A IPD VS. VDD (WDT DISABLE)

© 2003 Microchip Technology Inc.

| N                                          |

|--------------------------------------------|

| NOP Instruction                            |

| 0                                          |

| One-Time-Programmable (OTP) Devices7       |

| OPTION Instruction                         |

| OPTION Register                            |

| Oscillator Configurations                  |

| Oscillator Start-up Timer (OST)            |

| Р                                          |

| Package Marking Information117             |

| Packaging Information113                   |

| PCL and PCLATH                             |

| PCON Register                              |

| PICkit 1 FLASH Starter Kit                 |

| PICSTART Plus Development Programmer77     |

| PIE1 Register                              |

| PIR1 Register21                            |

| Port RB Interrupt                          |

| PORTA25                                    |

| PORTB                                      |

| Power Control/Status Register (PCON)51     |

| Power-Down Mode (SLEEP)                    |

| Power-On Reset (POR)                       |

| Power-up Timer (PWRT)50                    |

| Prescaler                                  |

| PRO MATE II Universal Device Programmer    |

| Program Memory Organization                |

| Q                                          |

| Quick-Turnaround-Production (QTP) Devices7 |

| R                                          |

| RC Oscillator                              |

| Reset                                      |

| RETFIE Instruction70                       |

| RETLW Instruction70                        |

| RETURN Instruction70                       |

| RLF Instruction71                          |

| RRF Instruction71                          |

| S                                          |

#### S

| Serialized Quick-Turnaround-Production (SQTP) Devices 7 | 7 |

|---------------------------------------------------------|---|

| SLEEP Instruction71                                     | 1 |

| Software Simulator (MPLAB SIM)76                        |   |

| Software Simulator (MPLAB SIM30)76                      | 6 |

| Special Features of the CPU45                           | 5 |

| Special Function Registers17                            | 7 |

| Stack                                                   | 3 |

| Status Register18                                       | 3 |

| SUBLW Instruction72                                     | 2 |

| SUBWF Instruction72                                     | 2 |

| SWAPF Instruction                                       | 3 |

## Т

| Timer0                             |     |

|------------------------------------|-----|

| TIMER0                             |     |

| TIMER0 (TMR0) Interrupt            |     |

| TIMER0 (TMR0) Module               |     |

| TMR0 with External Clock           |     |

| Timer1                             |     |

| Switching Prescaler Assignment     |     |

| Timing Diagrams and Specifications | 104 |

| TMR0 Interrupt                     | 56  |

| TRIS Instruction                   | 73  |

| TRISA                              | 25  |

| TRISB                              |     |

## V

| Voltage Reference Module<br>VRCON Register |      |

|--------------------------------------------|------|

| W                                          |      |

| Watchdog Timer (WDT)                       | . 58 |

| WWW, On-Line Support                       | 3    |

| X                                          |      |

| XORLW Instruction                          | . 73 |

| XORWF Instruction                          | . 73 |