Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

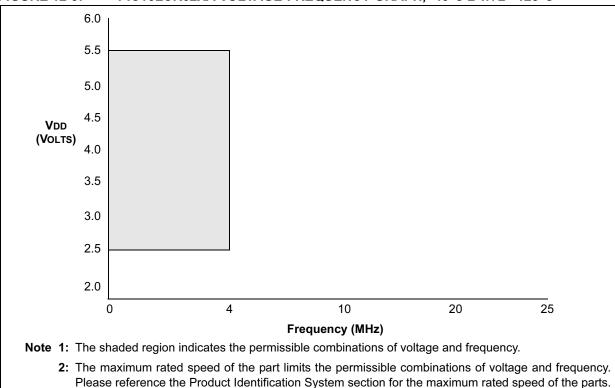

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 896B (512 x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 96 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            |                                                                              |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc620a-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Device Differences**

| Device                     | Voltage Range | Oscillator | Process Technology<br>(Microns) |

|----------------------------|---------------|------------|---------------------------------|

| PIC16C620 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C621 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C622 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C620A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16CR620A <sup>(2)</sup> | 2.5 - 5.5     | See Note 1 | 0.7                             |

| PIC16C621A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16C622A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.5V - 3.0V will require the PIC16LCR62X parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X parts.

4: For OTP parts, operations from 2.7V - 3.0V will require the PIC16LC62XA parts.

### 2.0 PIC16C62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the Oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16C62X.

Note: Microchip does not recommend code protecting windowed devices.

#### 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

#### 2.4 Serialized Quick-Turnaround-Production<sup>sm</sup> (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

### 4.0 MEMORY ORGANIZATION

#### 4.1 Program Memory Organization

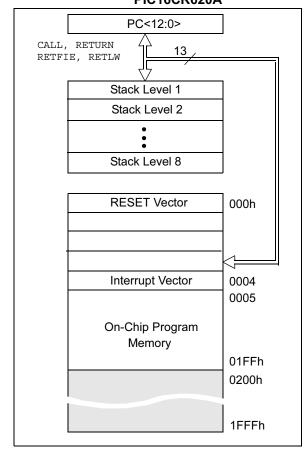

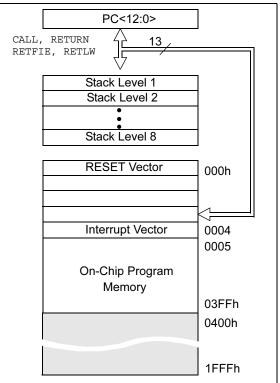

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

#### FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

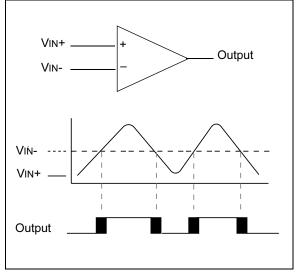

### 7.2 Comparator Operation

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

#### 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

#### 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

#### 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

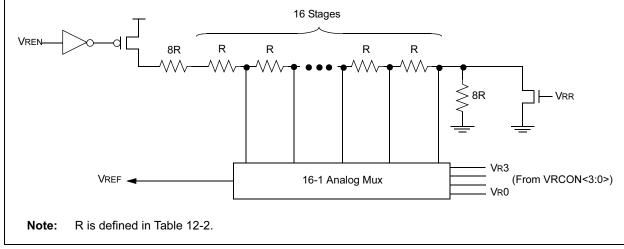

#### 8.0 **VOLTAGE REFERENCE** MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 8-1. The block diagram is given in Figure 8-1.

#### 8.1 **Configuring the Voltage Reference**

The Voltage Reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 12-1). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

|                                                                             | R/W-0       | R/W-0                   | R/W-0                      | U-0                     | R/W-0       | R/W-0      | R/W-0        | R/W-0  |

|-----------------------------------------------------------------------------|-------------|-------------------------|----------------------------|-------------------------|-------------|------------|--------------|--------|

|                                                                             | VREN        | VROE                    | Vrr                        | —                       | VR3         | VR2        | VR1          | VR0    |

|                                                                             | bit 7       |                         |                            |                         |             |            |              | bit 0  |

|                                                                             |             |                         |                            |                         |             |            |              |        |

| bit 7                                                                       |             | Enable<br>ircuit powere | od on                      |                         |             |            |              |        |

|                                                                             |             | -                       | ed down, no                | IDD drain               |             |            |              |        |

| bit 6                                                                       |             | F Output En             |                            |                         |             |            |              |        |

|                                                                             |             | s output on F           | RA2 pin<br>ed from RA2     | 2 nin                   |             |            |              |        |

| bit 5                                                                       |             | Range sele              |                            | 2 pm                    |             |            |              |        |

| bit o                                                                       | 1 = Low Ra  |                         |                            |                         |             |            |              |        |

|                                                                             | 0 = High R  | ange                    |                            |                         |             |            |              |        |

| bit 4                                                                       | Unimplem    | ented: Rea              | d as '0'                   |                         |             |            |              |        |

| bit 3-0                                                                     |             |                         |                            | VR [3:0] ≤ 1            | 5           |            |              |        |

|                                                                             |             |                         | (VR<3:0>/ 2<br>1/4 * Voo + | 4) * VDD<br>(VR<3:0>/ 3 | 2) * \/חח   |            |              |        |

|                                                                             |             | - 0. VILLI -            |                            | (111-0.0-7-0            | 2) 100      |            |              |        |

|                                                                             | Legend:     |                         |                            |                         |             |            |              |        |

|                                                                             | R = Reada   | ble bit                 | W = W                      | /ritable bit            | U = Unim    | nplemented | bit, read as | '0'    |

|                                                                             | - n = Value | at POR                  | '1' = B                    | it is set               | '0' = Bit i | s cleared  | x = Bit is u | nknown |

| 8-1:                                                                        | VOLTAGE     | REFERE                  |                            | K DIAGRA                | M           |            |              |        |

|                                                                             |             |                         | 16 \$                      | Stages                  |             |            |              |        |

| $\sim$                                                                      |             | _                       |                            |                         | _           | _          |              |        |

| $-\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 에드 8R       | R                       | R                          | R                       | R           |            |              |        |

|                                                                             |             | <u>\</u>                |                            |                         |             | • •        |              |        |

#### **REGISTER 8-1:** VRCON REGISTER(ADDRESS 9Fh)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **FIGURE 8-**

# 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CP0 <sup>(2)</sup> | CP1                                 | CP0 <sup>(2)</sup> | CP1     | CP0 <sup>(2)</sup>    |        | BODEN                     | CP1     | CP0 <sup>(2)</sup> | PWRTE       | WDTE      | F0SC1     | F0SC0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------|--------------------|---------|-----------------------|--------|---------------------------|---------|--------------------|-------------|-----------|-----------|-------|

| bit 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ļ                  | <u> </u>                            | ļļ                 |         | ļ                     |        | <u> </u>                  | <u></u> | <u>I</u>           | <u></u>     | <u> </u>  | ļ         | bit 0 |

| bit 13-8, <b>CP&lt;1:0&gt;:</b> Code protection bit pairs <sup>(2)</sup><br>5-4: Code protection for 2K program memory<br>11 = Program memory code protection off<br>10 = 0400h-07FFh code protected<br>01 = 0200h-07FFh code protected<br>00 = 0000h-07FFh code protected<br>Code protection for 1K program memory<br>11 = Program memory code protection off<br>10 = Program memory code protection off<br>01 = 0200h-03FFh code protected<br>00 = 0000h-03FFh code protected<br>Code protection for 0.5K program memory<br>11 = Program memory code protection off<br>10 = Program memory code protection off |                    |                                     |                    |         |                       |        |                           |         |                    |             |           |           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    | 0                                   | m memo<br>-01FFh c |         |                       | on off |                           |         |                    |             |           |           |       |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                                     | nted: Re           | -       |                       |        |                           |         |                    |             |           |           |       |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BOI                | DEN: Br                             | own-out l          | Reset E | nable bit             | (1)    |                           |         |                    |             |           |           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    | BOR en<br>BOR dis                   |                    |         |                       |        |                           |         |                    |             |           |           |       |

| bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 =                | <b>RTE</b> : Po<br>PWRT o<br>PWRT e |                    | īmer Er | able bit <sup>(</sup> | 1, 3)  |                           |         |                    |             |           |           |       |

| bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 =                | TE: Wat<br>WDT en<br>WDT dis        |                    | mer Ena | able bit              |        |                           |         |                    |             |           |           |       |

| bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |                                     |                    |         |                       |        |                           |         |                    |             |           |           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    | 2: Al<br>lis                        | l of the C<br>ted. |         | -                     |        | e given the<br>Power-up T |         |                    | nable the c | code prot | tection s | cheme |

| Legend<br>R = Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | l:<br>adable b     | it                                  |                    | W =     | Writable              | bit    | U =                       | Unimple | emented            | bit, read a | s '0'     |           |       |

#### 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

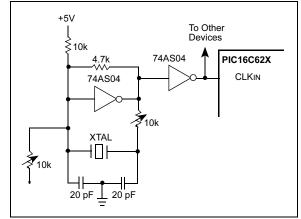

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

Figure 9-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 9-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

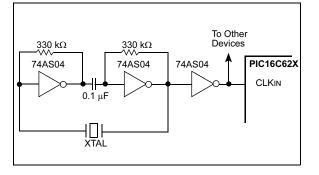

Figure 9-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 9-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

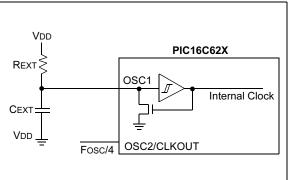

#### 9.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-5 shows how the R/C combination is connected to the PIC16C62X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 13.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 13.0 for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

#### FIGURE 9-5: RC OSCILLATOR MODE

#### 9.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (<u>PWRT</u> disabled), there will be no time-out at all. Figure 9-8, Figure 9-9 and Figure 9-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC16C62X device operating in parallel.

Table 9-4 shows the RESET conditions for some special registers, while Table 9-5 shows the RESET conditions for all the registers.

#### 9.4.6 POWER CONTROL (PCON)/ STATUS REGISTER

The power control/STATUS register, PCON (address 8Eh), has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{\text{BOR}} = 0$ , indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET, if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-------------------|-----------|-------------------|-----------------------|--|

|                          | PWRTE = 0         | PWRTE = 1 | Brown-out Reset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             | _         | 72 ms             | _                     |  |

#### TABLE 9-1: TIME-OUT IN VARIOUS SITUATIONS

| <b>TABLE 9-2</b> : | STATUS/PCON BITS AND THEIR SIGNIFICANCE |

|--------------------|-----------------------------------------|

|--------------------|-----------------------------------------|

| POR | BOR | то | PD |                                    |

|-----|-----|----|----|------------------------------------|

| 0   | Х   | 1  | 1  | Power-on Reset                     |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |

| 1   | 1   | 0  | u  | WDT Reset                          |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP            |

Legend: u = unchanged, x = unknown

#### TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 83h     | STATUS |       |       |       | TO    | PD    |       |       |       | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     |       | _     | _     | _     | POR   | BOR   | 0x                    | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

| MOVF             | Move f                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                    |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |

| MOVWF            | Move W to f                                                                                                                                                                                                                                                                          |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                    |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                                                                 |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |

| Description:     | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example          | MOVWF OPTION                                                                                                                                                                                                                                                                         |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F                                                                                                                                                                                                |

|                  | $\begin{array}{rcl} \text{OPTION} &= & 0x4F \\ \text{W} &= & 0x4F \end{array}$                                                                                                                                                                                                       |

| NOP              | No Operation |        |      |      |  |  |  |

|------------------|--------------|--------|------|------|--|--|--|

| Syntax:          | [ label ]    | NOP    |      |      |  |  |  |

| Operands:        | None         |        |      |      |  |  |  |

| Operation:       | No operation |        |      |      |  |  |  |

| Status Affected: | None         |        |      |      |  |  |  |

| Encoding:        | 00           | 0000   | 0xx0 | 0000 |  |  |  |

| Description:     | No opera     | ition. |      |      |  |  |  |

| Words:           | 1            |        |      |      |  |  |  |

| Cycles:          | 1            |        |      |      |  |  |  |

| Example          | NOP          |        |      |      |  |  |  |

| OPTION           | Load Op                                                                                                                                                                                                                                            | tion Reg             | gister                                          |      |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                          | OPTION               | N                                               |      |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                               |                      |                                                 |      |  |  |  |

| Operation:       | $(W) \rightarrow O$                                                                                                                                                                                                                                | PTION                |                                                 |      |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                               |                      |                                                 |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                 | 0000                 | 0110                                            | 0010 |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a read-<br>able/writable register, the user can<br>directly address it. |                      |                                                 |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                  |                      |                                                 |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |                      |                                                 |      |  |  |  |

| Example          |                                                                                                                                                                                                                                                    |                      |                                                 |      |  |  |  |

|                  | ity with                                                                                                                                                                                                                                           | future P<br>s, do no | vard com<br>PICmicro <sup>©</sup><br>ot use thi | B    |  |  |  |

|                  |                                                                                                                                                                                                                                                    |                      |                                                 |      |  |  |  |

| SWAPF            | Swap Ni                                                                                                                                                                    | bbles in  | f          |              |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|--------------|--|--|--|

| Syntax:          | [label]                                                                                                                                                                    | SWAPF     | f,d        |              |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 12\\ d\in \left[0,1\right] \end{array}$                                                                                                      | 27        |            |              |  |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                                                                                                                                   |           | <i>,</i> . |              |  |  |  |

| Status Affected: | None                                                                                                                                                                       |           |            |              |  |  |  |

| Encoding:        | 00                                                                                                                                                                         | 1110      | dfff       | ffff         |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |           |            |              |  |  |  |

| Words:           | 1                                                                                                                                                                          |           |            |              |  |  |  |

| Cycles:          | 1                                                                                                                                                                          |           |            |              |  |  |  |

| Example          | SWAPF                                                                                                                                                                      | REG,      | 0          |              |  |  |  |

|                  | Before In                                                                                                                                                                  | struction |            |              |  |  |  |

|                  |                                                                                                                                                                            | REG1      | = (        | DxA5         |  |  |  |

|                  | After Inst                                                                                                                                                                 | ruction   |            |              |  |  |  |

|                  |                                                                                                                                                                            | REG1<br>W |            | 0xA5<br>0x5A |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                            |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                  |

| Operation:       | $(W) \rightarrow TRIS$ register f;                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                               |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |

| Words:           | 1                                                                                                                                                                                  |

| Cycles:          | 1                                                                                                                                                                                  |

| Example          |                                                                                                                                                                                    |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |

| XORLW                                                                                                    | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                                                                  | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:                                                                                                | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Operation:                                                                                               | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Encoding:                                                                                                | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:                                                                                             | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Example:                                                                                                 | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                                                                                          | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                                                                                                          | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                          | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| XORWF                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|                                                                                                          | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Syntax:                                                                                                  | [label] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Syntax:                                                                                                  | [ <i>label</i> ] XORWF f,d $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                     | $ \begin{array}{ll} \textit{[label]} & XORWF & f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \end{array} $                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                                       | $ \begin{array}{ll} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) & \text{XOR.} & (\textit{f}) \rightarrow (\textit{dest}) \end{array} $                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{c c} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) . \text{XOR.} (\textit{f}) \rightarrow (\text{dest}) \\ \hline Z \\ \hline \hline 00 & 0110 & \text{dfff} & \text{ffff} \\ \hline \text{Exclusive OR the contents of the} \\ W \text{ register with register 'f'. If 'd' is} \\ 0, \text{ the result is stored in the W} \\ \text{register. If 'd' is 1, the result is} \end{array}$                       |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ $(W) . \text{XOR. } (f) \rightarrow (\text{dest})$ Z $\boxed{00 \qquad 0110  \text{dfff}  \text{ffff}}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'.                                                                                                      |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $[label] XORWF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00 \qquad 0110 \qquad dfff \qquad ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1                                                                                                                                                           |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z<br>00 0110 dfff ffff<br>Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is<br>0, the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'.<br>1<br>1                                                                                                                                             |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF REG 1 \\ \end{bmatrix}$                                                                                    |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ REG & = 0xAF \\ \end{bmatrix}$                      |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ \hline REG &= 0xAF \\ W &= 0xB5 \\ \end{bmatrix}$ |  |  |  |  |  |  |  |

#### 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.