Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 4MHz                                                                          |

| Connectivity               | -                                                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                              |

| Number of I/O              | 13                                                                            |

| Program Memory Size        | 896B (512 x 14)                                                               |

| Program Memory Type        | OTP                                                                           |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 96 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | -                                                                             |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc620at-04e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 MEMORY ORGANIZATION

### 4.1 Program Memory Organization

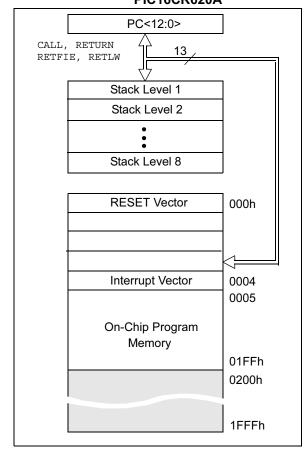

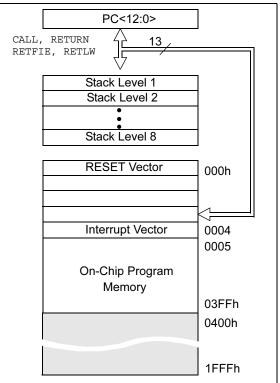

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

### FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

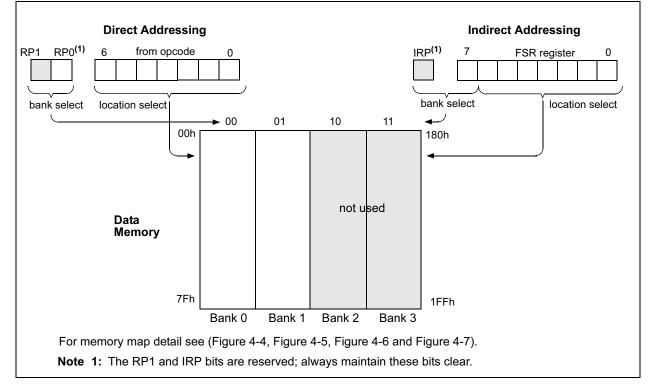

### 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

# FIGURE 4-6: DATA MEMORY MAP FOR THE PIC16C620A/CR620A/621A

|                                                   | 11010002                       |                     | - 17 (          |  |  |

|---------------------------------------------------|--------------------------------|---------------------|-----------------|--|--|

| File<br>Address                                   | 3                              |                     | File<br>Address |  |  |

| 00h                                               | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup> | 80h             |  |  |

| 01h                                               | TMR0                           | OPTION              | 81h             |  |  |

| 02h                                               | PCL                            | PCL                 | 82h             |  |  |

| 03h                                               | STATUS                         | STATUS              | 83h             |  |  |

| 04h                                               | FSR                            | FSR                 | 84h             |  |  |

| 05h                                               | PORTA                          | TRISA               | 85h             |  |  |

| 06h                                               | PORTB                          | TRISB               | 86h             |  |  |

| 07h                                               |                                |                     | 87h             |  |  |

| 08h                                               |                                |                     | 88h             |  |  |

| 09h                                               |                                |                     | 89h             |  |  |

| 0Ah                                               | PCLATH                         | PCLATH              | 8Ah             |  |  |

| 0Bh                                               | INTCON                         | INTCON              | 8Bh             |  |  |

| 0Ch                                               | PIR1                           | PIE1                | 8Ch             |  |  |

| 0Dh                                               |                                |                     | 8Dh             |  |  |

| 0Eh                                               |                                | PCON                | 8Eh             |  |  |

| 0Fh                                               |                                |                     | 8Fh             |  |  |

| 10h                                               |                                |                     | 90h             |  |  |

| 11h                                               |                                |                     | 91h             |  |  |

| 12h                                               |                                |                     | 92h             |  |  |

| 13h                                               |                                |                     | 93h             |  |  |

| 14h                                               |                                |                     | 94h             |  |  |

| 15h                                               |                                |                     | 95h             |  |  |

| 16h                                               |                                |                     | 96h             |  |  |

| 17h                                               |                                |                     | 97h             |  |  |

| 18h                                               |                                |                     | 98h             |  |  |

| 19h                                               |                                |                     | 99h             |  |  |

| 1Ah                                               |                                |                     | 9Ah             |  |  |

| 1Bh                                               |                                |                     | 9Bh             |  |  |

| 1Ch                                               |                                |                     | 9Ch             |  |  |

| 1Dh                                               |                                |                     | 9Dh             |  |  |

| 1Eh                                               |                                |                     | 9Eh             |  |  |

| 1Fh                                               | CMCON                          | VRCON               | 9Fh             |  |  |

| 20h                                               | General<br>Purpose<br>Register |                     | A0h             |  |  |

| 6Fh                                               |                                |                     |                 |  |  |

| 70h                                               | General                        |                     | F0h             |  |  |

|                                                   | Purpose<br>Register            | Accesses<br>70h-7Fh |                 |  |  |

| 7Fh                                               | Bank 0                         | Bank 1              | 」 FFh           |  |  |

| Unimplemented data memory locations, read as '0'. |                                |                     |                 |  |  |

| Note 1:                                           | Not a physical re              | gister.             |                 |  |  |

|                                                   |                                |                     |                 |  |  |

#### FIGURE 4-7: DATA MEMORY MAP FOR THE PIC16C622A

|                                         |                     | C10C022A            |                 |  |  |

|-----------------------------------------|---------------------|---------------------|-----------------|--|--|

| File<br>Address                         | 3                   |                     | File<br>Address |  |  |

| 00h                                     | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |

| 01h                                     | TMR0                | OPTION              | 81h             |  |  |

| 02h                                     | PCL                 | PCL                 | 82h             |  |  |

| 03h                                     | STATUS              | STATUS              | 83h             |  |  |

| 04h                                     | FSR                 | FSR                 | 84h             |  |  |

| 05h                                     | PORTA               | TRISA               | 85h             |  |  |

| 06h                                     | PORTB               | TRISB               | 86h             |  |  |

| 07h                                     |                     |                     | 87h             |  |  |

| 08h                                     |                     |                     | 88h             |  |  |

| 09h                                     |                     |                     | 89h             |  |  |

| 0Ah                                     | PCLATH              | PCLATH              | 8Ah             |  |  |

| 0Bh                                     | INTCON              | INTCON              | 8Bh             |  |  |

| 0Ch                                     | PIR1                | PIE1                | 8Ch             |  |  |

| 0Dh                                     |                     |                     | 8Dh             |  |  |

| 0Eh                                     |                     | PCON                | 8Eh             |  |  |

| 0Fh                                     |                     |                     | 8Fh             |  |  |

| 10h                                     |                     |                     | 90h             |  |  |

| 11h                                     |                     |                     | 91h             |  |  |

| 12h                                     |                     |                     | 92h             |  |  |

| 13h                                     |                     |                     | 93h             |  |  |

| 14h                                     |                     |                     | 94h             |  |  |

| 15h                                     |                     |                     | 95h             |  |  |

| 16h                                     |                     |                     | 96h             |  |  |

| 17h                                     |                     |                     | 97h             |  |  |

| 18h                                     |                     |                     | 98h             |  |  |

| 19h                                     |                     |                     | 99h             |  |  |

| 1Ah                                     |                     |                     | 9Ah             |  |  |

| 1Bh                                     |                     |                     | 9Bh             |  |  |

| 1Ch                                     |                     |                     | 9Ch             |  |  |

| 1Dh                                     |                     |                     | 9Dh             |  |  |

| 1Eh                                     |                     |                     | 9Eh             |  |  |

| 1Fh                                     | CMCON               | VRCON               | 9Fh             |  |  |

| 20h                                     |                     |                     | A0h             |  |  |

|                                         | General             | General             | Aon             |  |  |

|                                         | Purpose<br>Register | Purpose<br>Register |                 |  |  |

|                                         | rtegister           | rtegister           | BFh             |  |  |

|                                         |                     |                     | C0h             |  |  |

| 0.51                                    |                     |                     |                 |  |  |

| 6Fh                                     | 0                   |                     | F0h             |  |  |

| 70h                                     | General<br>Purpose  | Accesses            |                 |  |  |

| 754                                     | Register            | 70h-7Fh             | FFh             |  |  |

| 7Fh                                     | Bank 0              | Bank 1              | → FF11          |  |  |

|                                         |                     |                     |                 |  |  |

| Unimp                                   | plemented data me   | mory locations, re  | ad as '0'.      |  |  |

| <b>Note 1:</b> Not a physical register. |                     |                     |                 |  |  |

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-9. However, IRP is not used in the PIC16C62X.

A simple program to clear RAM location 20h-7Fh using indirect addressing is shown in Example 4-1.

| EXAN  | IPLE 4- | 1: INC | DIRECT ADDRESSING    |

|-------|---------|--------|----------------------|

|       | movlw   | 0x20   | ;initialize pointer  |

|       | movwf   | FSR    | ;to RAM              |

| NEXT  | clrf    | INDF   | ;clear INDF register |

|       | incf    | FSR    | ;inc pointer         |

|       | btfss   | FSR,7  | ;all done?           |

|       | goto    | NEXT   | ;no clear next       |

|       |         |        | ;yes continue        |

| CONTI | NUE:    |        |                      |

|       |         |        |                      |

### FIGURE 4-9: DIRECT/INDIRECT ADDRESSING PIC16C62X

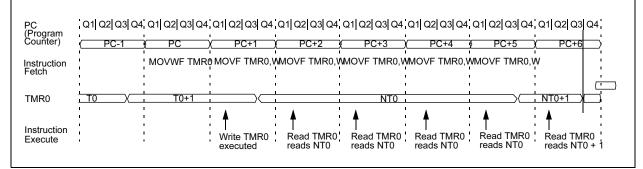

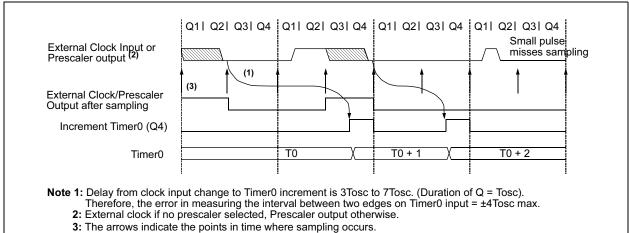

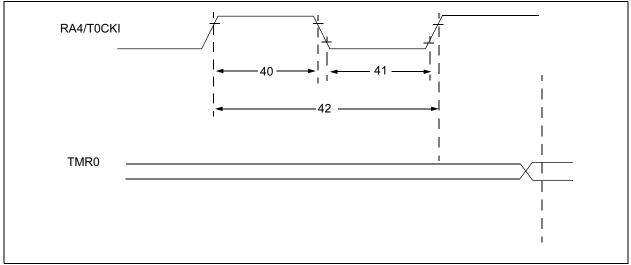

### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

# 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                   |                                 | <b>(</b> | ,   |       |       |       |       |  |

|---------|-------------------|---------------------------------|----------|-----|-------|-------|-------|-------|--|

|         | R-0               | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|         | C2OUT             | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |  |

|         | bit 7             |                                 |          |     |       |       |       | bit 0 |  |

|         |                   |                                 |          |     |       |       |       |       |  |

| bit 7   | <b>C2OUT</b> : Co | omparator 2                     | output   |     |       |       |       |       |  |

|         | 1 = C2 VIN        | + > C2 VIN-                     |          |     |       |       |       |       |  |

|         | 0 = C2 VIN        | + < C2 VIN-                     |          |     |       |       |       |       |  |

| bit 6   | C10UT: Co         | omparator 1                     | output   |     |       |       |       |       |  |

|         | 1 = C1 VIN        | + > C1 VIN-                     |          |     |       |       |       |       |  |

|         | 0 = C1 VIN        | + < C1 VIN-                     |          |     |       |       |       |       |  |

| bit 5-4 | Unimplem          | ented: Read                     | d as '0' |     |       |       |       |       |  |

| bit 3   | CIS: Comp         | arator Input                    | Switch   |     |       |       |       |       |  |

|         | When CM<          | <2:0>: = 001                    | :        |     |       |       |       |       |  |

|         | 1 = C1 VIN-       | - connects to                   | o RA3    |     |       |       |       |       |  |

|         | 0 = C1 VIN        | - connects to                   | o RA0    |     |       |       |       |       |  |

|         | When CM<          | <2:0> = 010:                    |          |     |       |       |       |       |  |

|         |                   | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |  |

|         |                   | I- connects t                   |          |     |       |       |       |       |  |

|         |                   | - connects to                   |          |     |       |       |       |       |  |

|         | C2 VIN            | I- connects t                   | 0 RA1    |     |       |       |       |       |  |

| bit 2-0 | CM<2:0>:          | Comparator                      | mode.    |     |       |       |       |       |  |

|         |                   |                                 |          |     |       |       |       |       |  |

|         | Legend:           |                                 |          |     |       |       |       |       |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |

|       | interrupt flag may not get set.            |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

# 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will

Vdd ∆Vt = 0.6V RIC Rs < 10K Δικ **I**LEAKAGE CPIN VT = 0.6V ±500 nA 5 pF Vss Input Capacitance Legend CPIN = Threshold Voltage Vт = Leakage Current at the pin due to various junctions ILEAKAGE = = Interconnect Resistance RIC Rs = Source Impedance Analog Voltage VA =

FIGURE 7-4: ANALOG INPUT MODEL

wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

### 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

### 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A maximum source impedance of  $10 \ k\Omega$ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

### 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

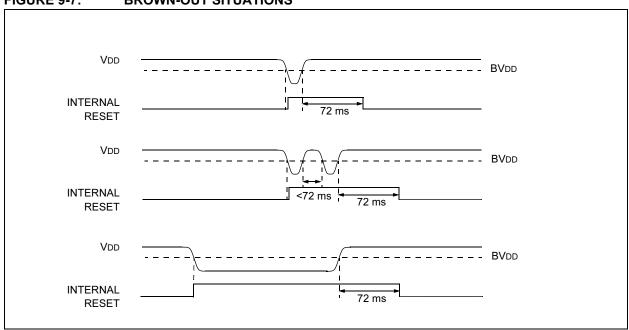

#### 9.4.4 BROWN-OUT RESET (BOR)

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

#### FIGURE 9-7: BROWN-OUT SITUATIONS

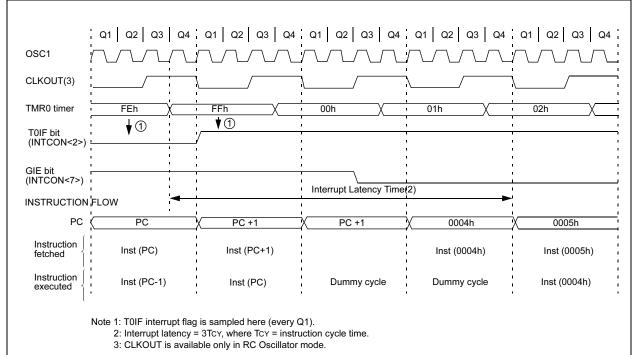

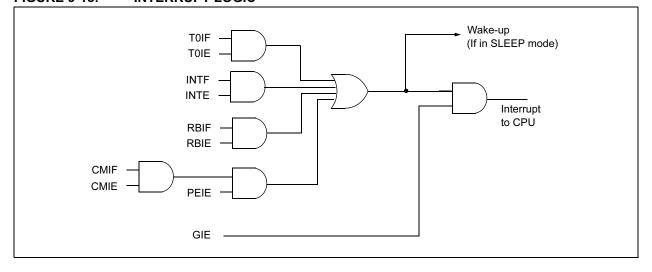

### 9.5 Interrupts

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test, Skip if Clear                                                   |

|------------------|---------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      | Syntax:          | [label]BTFSC f,b                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$       |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                   |

| Status Affected: | None                                                                | Status Affected: | None                                                                      |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                         |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0', then the                               |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0', then the next instruc- |

| Cycles:          | 1                                                                   |                  | tion fetched during the current                                           |

| Example          | BCF FLAG_REG, 7                                                     |                  | instruction execution is discarded,                                       |

|                  | Before Instruction<br>FLAG_REG = 0xC7                               |                  | and a NOP is executed instead,<br>making this a two-cycle instruction.    |

|                  | After Instruction                                                   | Words:           | 1                                                                         |

|                  | FLAG_REG = 0x47                                                     | Cycles:          | 1(2)                                                                      |

|                  |                                                                     | Example          | here btfsc <b>FLAG,1</b><br>false goto <b>process co</b>                  |

| BSF              | Bit Set f                                                           |                  | TRUE DE                                                                   |

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |                  | •                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                  | Before Instruction<br>PC = address HERE                                   |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |                  | After Instruction<br>if FLAG<1> = 0.                                      |

| Status Affected: | None                                                                |                  | PC = address TRUE                                                         |

| Encoding:        | 01 01bb bfff ffff                                                   |                  | if FLAG<1>=1,<br>PC = address FALSE                                       |

| Description:     | Bit 'b' in register 'f' is set.                                     |                  | PC = address FALSE                                                        |

| Words:           | 1                                                                   |                  |                                                                           |

| Cycles:          | 1                                                                   |                  |                                                                           |

| Example          | BSF FLAG_REG, 7                                                     |                  |                                                                           |

Before Instruction FLAG\_REG = 0x0A After Instruction

FLAG\_REG = 0x8A

| CLRW                                                                               | Clear W                                                                                                                                                                                                                                                                                                                                                                                             | COMF                                                                                          | Complement f                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                            | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                        | Syntax:                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                           |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                | Operands:                                                                                     | $0 \leq f \leq 127$                                                                                                                                                                                                                                                                                 |

| Operation:                                                                         | $00h \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                               |                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                           |

|                                                                                    | $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                                                   | Operation:                                                                                    | $(\bar{f}) \rightarrow (dest)$                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                   | Z                                                                                                                                                                                                                                                                                                                                                                                                   | Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                          | 00 0001 0000 0011                                                                                                                                                                                                                                                                                                                                                                                   | Encoding:                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                   |

| Description:                                                                       | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                         | Description:                                                                                  | The contents of register 'f' are<br>complemented. If 'd' is 0, the                                                                                                                                                                                                                                  |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               | result is stored in W. If 'd' is 1, the result is stored back in register 'f'.                                                                                                                                                                                                                      |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                   | Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                   |

| Example                                                                            | CLRW                                                                                                                                                                                                                                                                                                                                                                                                | Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                   |

|                                                                                    | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                  | Example                                                                                       | COMF REG1,0                                                                                                                                                                                                                                                                                         |

|                                                                                    | W = 0x5A<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                       | Example                                                                                       | Before Instruction                                                                                                                                                                                                                                                                                  |

|                                                                                    | W = 0x00 $Z = 1$                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               | REG1 = 0x13<br>After Instruction<br>REG1 = 0x13<br>W = 0xEC                                                                                                                                                                                                                                         |

| CLRWDT                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Syntax:                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Cyntax.                                                                            | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                      | DECF                                                                                          | Decrement f                                                                                                                                                                                                                                                                                         |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                | DECF<br>Syntax:                                                                               | Decrement f                                                                                                                                                                                                                                                                                         |

|                                                                                    | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                                                                          | Syntax:                                                                                       | <b>Decrement f</b><br>[ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                      |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow \underline{WD}T$ prescaler,                                                                                                                                                                                                                                                                                                                         | -                                                                                             | [label] DECF f,d                                                                                                                                                                                                                                                                                    |

| Operands:                                                                          | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                                                                          | Syntax:                                                                                       | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                            |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$                                                                                                                                                                                                                                                                                                    | Syntax:<br>Operands:                                                                          | $ \begin{bmatrix} \textit{label} \end{bmatrix} \text{ DECF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] $                                                                                                                                                                                                |

| Operands:<br>Operation:                                                            | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                    | Syntax:<br>Operands:<br>Operation:                                                            | $\begin{bmatrix} label \end{bmatrix} DECF f,d$<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>$(f) - 1 \rightarrow (dest)$                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:                                        | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO, PD}$                                                                                                                                                                                                                                                | Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | [ <i>label</i> ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$ $\overline{TO, PD}$ $00  000  0110  0100$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>pres <u>caler</u> of the WDT. STATUS                                                                                                              | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                                    |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \hline \overline{TO}, \overline{PD} \\ \hline \hline 00 & 0000 & 0110 & 0100 \\ \hline \\ CLRWDT \text{ instruction resets the} \\ Watchdog Timer. It also resets the \\ prescaler of the WDT. STATUS \\ bits TO and PD are set. \\ \hline \end{array}$ | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011 \qquad dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \overline{PD} \\ \hline \hline 00 & 0000 & 0110 & 0100 \\ \hline \end{array}$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.<br>1      | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1     |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                 |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                 |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                    |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                    |

| Cycles:          | 2                                                                                                                                                                                                                    |

| Example          | RETFIE                                                                                                                                                                                                               |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |

| RETLW            | Return with Literal in W                                                                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                                                         |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                      |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                                                         |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction.                                       |

| Words:           | 1                                                                                                                                                                                                                         |

| Cycles:          | 2                                                                                                                                                                                                                         |

| Example          | CALL TABLE;W contains table                                                                                                                                                                                               |

| TABLE            | ;offset value<br>;W now has table value<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>RETLW k2 ;<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8 |

| RETURN           | Return from Subroutine                                                                                                                                                                                                    |

| Syntax:          | [label] RETURN                                                                                                                                                                                                            |

| Operands:        | None                                                                                                                                                                                                                      |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                      |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                                                         |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction.                                                                |

| Words:           | 1                                                                                                                                                                                                                         |

| Cycles:          | 2                                                                                                                                                                                                                         |

| Example          | RETURN                                                                                                                                                                                                                    |

|                  | After Interrupt<br>PC = TOS                                                                                                                                                                                               |

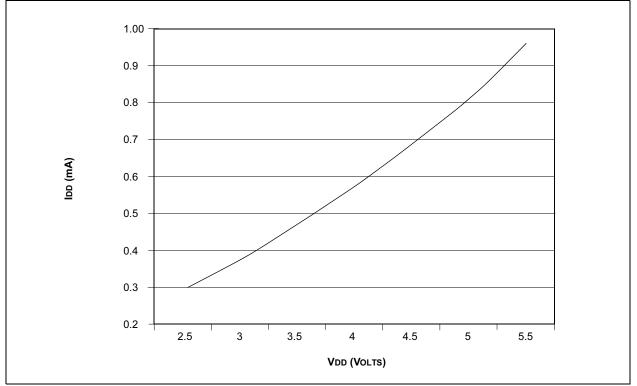

### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended) (CONT.)

|                                                                   |                                                                   |                                                                                                                                                                                                                                                                        | Stand                                                                                                                              | dard O                             | perati                                            | ng Con                                                                                                                                                                                                                                                                    | ditions (unless otherwise stated)                                                                                                                                                                                                      |

|-------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC16C                                                            | 62X                                                               |                                                                                                                                                                                                                                                                        | Opera                                                                                                                              | ating te                           | empera                                            |                                                                                                                                                                                                                                                                           | $\begin{array}{ll} 0^{\circ}C & \leq TA \leq +85^{\circ}C \text{ for industrial and} \\ 0^{\circ}C & \leq TA \leq +70^{\circ}C \text{ for commercial and} \\ 0^{\circ}C & \leq TA \leq +125^{\circ}C \text{ for extended} \end{array}$ |

| PIC16L                                                            |                                                                   |                                                                                                                                                                                                                                                                        | $-40^{\circ}C  \leq TA \leq +125^{\circ}C \mbox{ for extended} \label{eq:tau}$ Operating voltage VDD range is the PIC16C62X range. |                                    |                                                   | $\begin{array}{lll} 0^{\circ}C &\leq TA \leq +85^{\circ}C \text{ for industrial and} \\ 0^{\circ}C &\leq TA \leq +70^{\circ}C \text{ for commercial and} \\ 0^{\circ}C &\leq TA \leq +125^{\circ}C \text{ for extended} \\ \text{ge is the PIC16C62X range.} \end{array}$ |                                                                                                                                                                                                                                        |

| Param<br>. No.                                                    | Sym                                                               | Characteristic                                                                                                                                                                                                                                                         | Min                                                                                                                                | Тур†                               | Мах                                               | Units                                                                                                                                                                                                                                                                     | Conditions                                                                                                                                                                                                                             |

| D022<br>D022A<br>D023<br>D023A<br>D022A<br>D022A<br>D022A<br>D023 | ΔIWDT<br>ΔIBOR<br>ΔICOM<br>P<br>ΔIVREF<br>ΔIWDT<br>ΔIBOR<br>ΔICOM | WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each<br>Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup><br>WDT Current <sup>(5)</sup><br>Brown-out Reset Current <sup>(5)</sup><br>Comparator Current for each |                                                                                                                                    | 6.0<br>350<br>—<br>6.0<br>350<br>— | 20<br>25<br>425<br>100<br>300<br>15<br>425<br>100 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ                                                                                                                                                                                                                                    | VDD=4.0V $(125°C)$ $BOD enabled, VDD = 5.0V$ $VDD = 4.0V$ $VDD = 4.0V$ $VDD = 3.0V$ $BOD enabled, VDD = 5.0V$ $VDD = 3.0V$                                                                                                             |

| D023A                                                             | P<br>∆IVREF                                                       | Comparator <sup>(5)</sup><br>VREF Current <sup>(5)</sup>                                                                                                                                                                                                               | —                                                                                                                                  | —                                  | 300                                               | μA                                                                                                                                                                                                                                                                        | VDD = 3.0V                                                                                                                                                                                                                             |