Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E-XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 896B (512 x 14)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 80 × 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc620t-04i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin # | I/O/P Type             | Buffer<br>Type        | Description                                                                                                                                                                                                         |  |  |

|--------------|-------------------|---------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OSC1/CLKIN   | 16                | 18            | I                      | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                               |  |  |

| OSC2/CLKOUT  | 15                | 17            | 0                      | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin out-<br>puts CLKOUT, which has 1/4 the frequency of OSC1<br>and denotes the instruction cycle rate. |  |  |

| MCLR/VPP     | 4                 | 4             | I/P                    | ST                    | Master Clear (Reset) input/programming voltage input.<br>This pin is an Active Low Reset to the device.                                                                                                             |  |  |

|              |                   |               |                        |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |  |  |

| RA0/AN0      | 17                | 19            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |  |  |

| RA1/AN1      | 18                | 20            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |  |  |

| RA2/AN2/VREF | 1                 | 1             | I/O                    | ST                    | Analog comparator input or VREF output                                                                                                                                                                              |  |  |

| RA3/AN3      | 2                 | 2             | I/O                    | ST                    | Analog comparator input /output                                                                                                                                                                                     |  |  |

| RA4/T0CKI    | 3                 | 3             | I/O                    | ST                    | Can be selected to be the clock input to the Timer<br>timer/counter or a comparator output. Output is<br>open drain type.                                                                                           |  |  |

|              |                   |               |                        |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                                 |  |  |

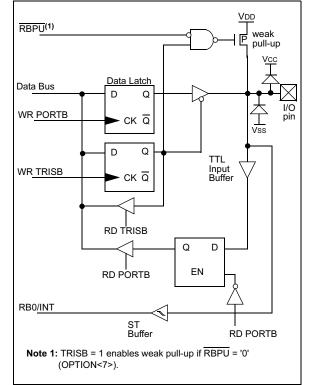

| RB0/INT      | 6                 | 7             | I/O                    | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an externa interrupt pin.                                                                                                                                                           |  |  |

| RB1          | 7                 | 8             | I/O                    | TTL                   |                                                                                                                                                                                                                     |  |  |

| RB2          | 8                 | 9             | I/O                    | TTL                   |                                                                                                                                                                                                                     |  |  |

| RB3          | 9                 | 10            | I/O                    | TTL                   |                                                                                                                                                                                                                     |  |  |

| RB4          | 10                | 11            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |  |  |

| RB5          | 11                | 12            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |  |  |

| RB6          | 12                | 13            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock                                                                                                                                                                   |  |  |

| RB7          | 13                | 14            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                   |  |  |

| Vss          | 5                 | 5,6           | Р                      |                       | Ground reference for logic and I/O pins.                                                                                                                                                                            |  |  |

| Vdd          | 14                | 15,16         | Р                      | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                             |  |  |

| Legend:      | O = out<br>— = No | •             | I/O = inp<br>I = Input | ut/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                             |  |  |

TTL = TTL input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

# 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the | N-0     R/W-0       EIE     TOIE       rrupt Enable bit       n-masked interrunts       Interrupts       Interrupt Enable       n-masked periphoreripheral interrupt       erflow Interrupt Entrupt       TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                        | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                      | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                          | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables all u<br>sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                         | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                            | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                         | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                              | pts                                                                                                                     | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| TMR0 Ove<br>nables the<br>sables the                                                                                         | rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                                                     |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables the<br>isables the                                                                                                    | TMR0 interrupt                                                                                                                                                                                                           | nable bit                                                                                                               |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables the                                                                                                                   |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | I MRU interrupt                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | External Interrupt                                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB0/INT externa<br>RB0/INT externa                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | hange Interrupt E                                                                                                                                                                                                        |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB port change i                                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB port change                                                                                                                                                                                                           | •                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| TMR0 Ove                                                                                                                     | rflow Interrupt Fl                                                                                                                                                                                                       | ag bit                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| MR0 registe                                                                                                                  | er has overflowed                                                                                                                                                                                                        | d (must be cle                                                                                                          | eared in soft                                                                                                                                                        | ware)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| MR0 registe                                                                                                                  | er did not overflov                                                                                                                                                                                                      | W                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| RB0/INT E                                                                                                                    | xternal Interrupt                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |

| RB Port Cl                                                                                                                   | hange Interrupt F                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| 'hen at leas                                                                                                                 |                                                                                                                                                                                                                          | •                                                                                                                       | -                                                                                                                                                                    | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |

|                                                                                                                              | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                                                                                                                     | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b>                                                                                                                              | PIE1 REGIS                                                                                                                     | PIE1 REGISTER (ADDRESS 8CH) |     |     |     |     |     |     |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

|                                                                                                                                                   | U-0                                                                                                                            | R/W-0                       | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |  |

|                                                                                                                                                   |                                                                                                                                | CMIE                        | _   |     |     | —   | _   | —   |  |  |  |

|                                                                                                                                                   | bit 7 bit 0                                                                                                                    |                             |     |     |     |     |     |     |  |  |  |

| bit 7                                                                                                                                             | Unimpleme                                                                                                                      | Unimplemented: Read as '0'  |     |     |     |     |     |     |  |  |  |

| bit 6                                                                                                                                             | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt |                             |     |     |     |     |     |     |  |  |  |

| bit 5-0                                                                                                                                           | Unimplemented: Read as '0'                                                                                                     |                             |     |     |     |     |     |     |  |  |  |

| Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |                                                                                                                                |                             |     |     |     |     |     |     |  |  |  |

# 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | its corresponding enable bit or the global<br>enable bit, GIE (INTCON<7>). User            |  |  |  |  |  |  |

|       | software should ensure the appropriate                                                     |  |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                            |  |  |  |  |  |  |

|       | an interrupt.                                                                              |  |  |  |  |  |  |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5:                              | PIRI REGISTER (ADDRESS UCH)         |         |         |              |              |           |                |        |  |  |

|--------------------------------------|-------------------------------------|---------|---------|--------------|--------------|-----------|----------------|--------|--|--|

|                                      | U-0                                 | R/W-0   | U-0     | U-0          | U-0          | U-0       | U-0            | U-0    |  |  |

|                                      |                                     | CMIF    |         | —            | _            |           |                |        |  |  |

|                                      | bit 7                               |         |         |              |              |           |                | bit 0  |  |  |

|                                      |                                     |         |         |              |              |           |                |        |  |  |

| bit 7                                | Unimplemented: Read as '0'          |         |         |              |              |           |                |        |  |  |

| bit 6                                | CMIF: Comparator Interrupt Flag bit |         |         |              |              |           |                |        |  |  |

|                                      | 1 = Comparator input has changed    |         |         |              |              |           |                |        |  |  |

| 0 = Comparator input has not changed |                                     |         |         |              |              |           |                |        |  |  |

| bit 5-0                              | Unimplemented: Read as '0'          |         |         |              |              |           |                |        |  |  |

|                                      |                                     |         |         |              |              |           |                |        |  |  |

| Legend:                              |                                     |         |         |              |              |           |                |        |  |  |

|                                      | R = Readab                          | ole bit | W = W   | /ritable bit | U = Unim     | plemented | bit, read as ' | 0'     |  |  |

|                                      | - n = Value                         | at POR  | '1' = B | it is set    | '0' = Bit is | s cleared | x = Bit is u   | nknown |  |  |

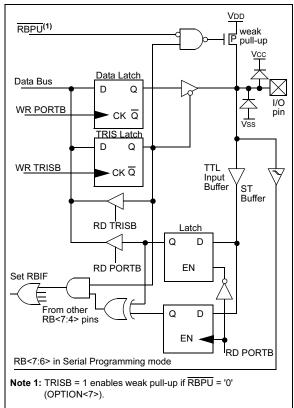

# 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a High Impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A \ typical$ ). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (e.g., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

# FIGURE 5-5: BLOCK DIAGRAM OF RB<7:4> PINS

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes.)

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

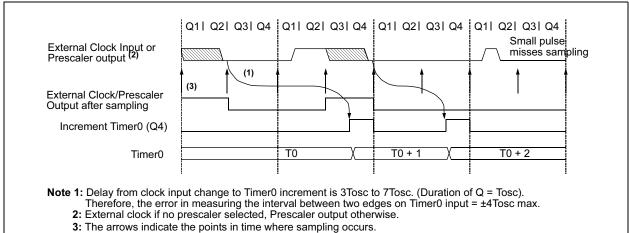

# 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

# 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

# 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

NOTES:

# 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

# REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                             |                                 | <b>(</b> | ,   |       |       |       |       |  |

|---------|-----------------------------|---------------------------------|----------|-----|-------|-------|-------|-------|--|

|         | R-0                         | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|         | C2OUT                       | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |  |

|         | bit 7                       |                                 |          |     |       |       |       | bit 0 |  |

|         |                             |                                 |          |     |       |       |       |       |  |

| bit 7   | <b>C2OUT</b> : Co           | omparator 2                     | output   |     |       |       |       |       |  |

|         | 1 = C2 VIN                  | + > C2 VIN-                     |          |     |       |       |       |       |  |

|         | 0 = C2 VIN                  | + < C2 VIN-                     |          |     |       |       |       |       |  |

| bit 6   | <b>C1OUT</b> : Co           | omparator 1                     | output   |     |       |       |       |       |  |

|         | 1 = C1 VIN                  | + > C1 VIN-                     |          |     |       |       |       |       |  |

|         | 0 = C1 VIN + < C1 VIN -     |                                 |          |     |       |       |       |       |  |

| bit 5-4 | Unimplemented: Read as '0'  |                                 |          |     |       |       |       |       |  |

| bit 3   | CIS: Comp                   | arator Input                    | Switch   |     |       |       |       |       |  |

|         | When CM<                    | <2:0>: = 001                    | :        |     |       |       |       |       |  |

|         | 1 = C1 VIN- connects to RA3 |                                 |          |     |       |       |       |       |  |

|         | 0 = C1 VIN                  | - connects to                   | o RA0    |     |       |       |       |       |  |

|         | When CM<                    | <2:0> = 010:                    |          |     |       |       |       |       |  |

|         |                             | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |  |

|         |                             | I- connects t                   |          |     |       |       |       |       |  |

|         |                             | - connects to                   |          |     |       |       |       |       |  |

|         | C2 VIN                      | I- connects t                   | 0 RA1    |     |       |       |       |       |  |

| bit 2-0 | CM<2:0>:                    | Comparator                      | mode.    |     |       |       |       |       |  |

|         |                             |                                 |          |     |       |       |       |       |  |

|         | Legend:                     |                                 |          |     |       |       |       |       |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

# EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

# 7.2 Comparator Operation

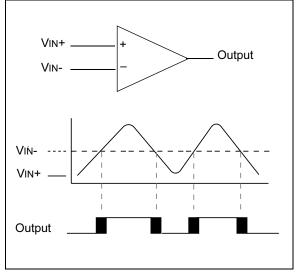

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

# 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

# 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

# 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

# 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |

|       | interrupt flag may not get set.            |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

# 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will

Vdd ∆Vt = 0.6V RIC Rs < 10K Δικ **I**LEAKAGE CPIN VT = 0.6V ±500 nA 5 pF Vss Input Capacitance Legend CPIN = Threshold Voltage Vт = Leakage Current at the pin due to various junctions ILEAKAGE = = Interconnect Resistance RIC Rs = Source Impedance Analog Voltage VA =

FIGURE 7-4: ANALOG INPUT MODEL

wake up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes up from SLEEP, the contents of the CMCON register are not affected.

# 7.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the comparator module to be in the comparator RESET mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

# 7.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A maximum source impedance of  $10 \ k\Omega$ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

### 8.0 **VOLTAGE REFERENCE** MODULE

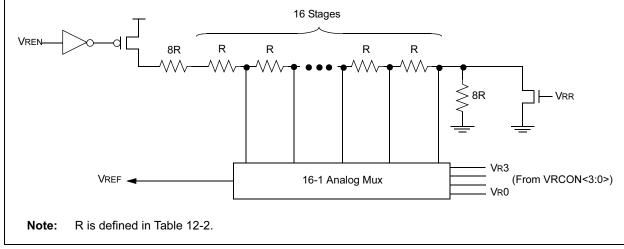

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 8-1. The block diagram is given in Figure 8-1.

### 8.1 **Configuring the Voltage Reference**

The Voltage Reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 12-1). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

|                                                                             | R/W-0                                                                      | R/W-0         | R/W-0                      | U-0                     | R/W-0       | R/W-0      | R/W-0        | R/W-0  |  |  |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------|----------------------------|-------------------------|-------------|------------|--------------|--------|--|--|

|                                                                             | VREN                                                                       | VROE          | Vrr                        | —                       | VR3         | VR2        | VR1          | VR0    |  |  |

|                                                                             | bit 7                                                                      |               |                            |                         |             |            |              | bit 0  |  |  |

|                                                                             |                                                                            |               |                            |                         |             |            |              |        |  |  |

| bit 7                                                                       |                                                                            |               | od on                      |                         |             |            |              |        |  |  |

|                                                                             | 1 = VREF circuit powered on<br>0 = VREF circuit powered down, no IDD drain |               |                            |                         |             |            |              |        |  |  |

| bit 6                                                                       |                                                                            | F Output En   |                            |                         |             |            |              |        |  |  |

|                                                                             |                                                                            | s output on F | RA2 pin<br>ed from RA2     | 2 nin                   |             |            |              |        |  |  |

| bit 5                                                                       |                                                                            | Range sele    |                            | 2 pm                    |             |            |              |        |  |  |

| bit o                                                                       | 1 = Low Ra                                                                 |               |                            |                         |             |            |              |        |  |  |

|                                                                             | 0 = High R                                                                 | ange          |                            |                         |             |            |              |        |  |  |

| bit 4                                                                       | Unimplem                                                                   | ented: Rea    | d as '0'                   |                         |             |            |              |        |  |  |

| bit 3-0                                                                     |                                                                            |               |                            | VR [3:0] ≤ 1            | 5           |            |              |        |  |  |

|                                                                             |                                                                            |               | (VR<3:0>/ 2<br>1/4 * Voo + | 4) * VDD<br>(VR<3:0>/ 3 | 2) * \/חח   |            |              |        |  |  |

|                                                                             |                                                                            | - 0. VILLI -  |                            | (111-0.0-7-0            | 2) 100      |            |              |        |  |  |

|                                                                             | Legend:                                                                    |               |                            |                         |             |            |              |        |  |  |

|                                                                             | R = Reada                                                                  | ble bit       | W = W                      | /ritable bit            | U = Unim    | nplemented | bit, read as | '0'    |  |  |

|                                                                             | - n = Value                                                                | at POR        | '1' = B                    | it is set               | '0' = Bit i | s cleared  | x = Bit is u | nknown |  |  |

| 8-1:                                                                        | VOLTAGE                                                                    | REFERE        |                            | K DIAGRA                | M           |            |              |        |  |  |