Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

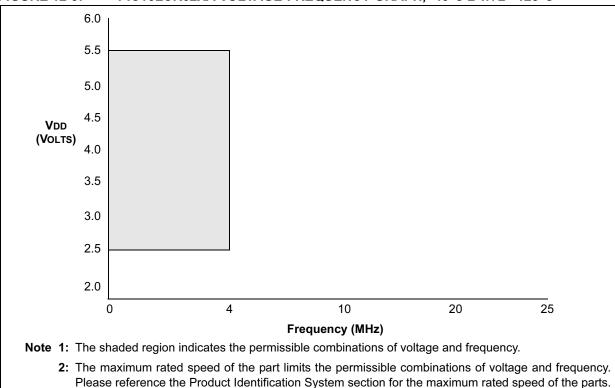

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

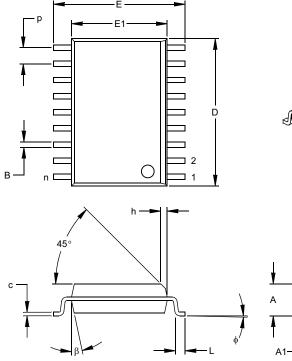

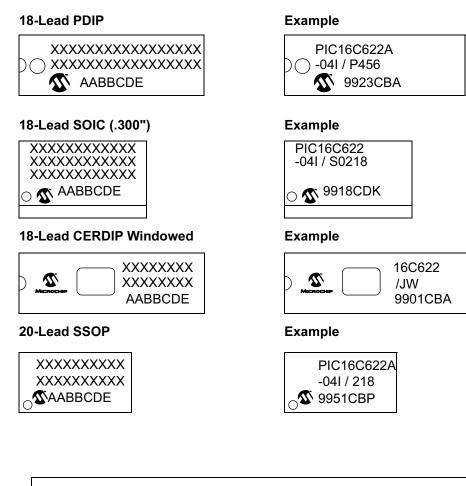

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc621-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

# 4.0 MEMORY ORGANIZATION

# 4.1 Program Memory Organization

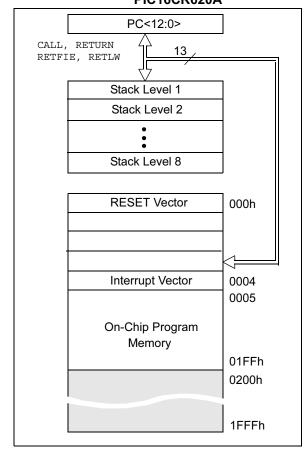

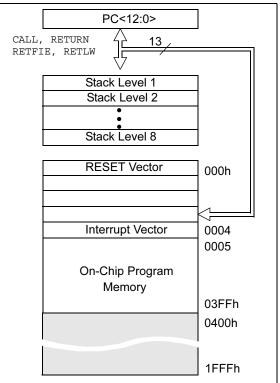

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

# FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

#### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| E PE<br>Global Internables all un<br>isables all in<br>Peripheral<br>nables all p<br>TMR0 Ove<br>nables the T<br>isables the | N-0     R/W-0       EIE     TOIE       Trupt Enable bit       n-masked interrunts       Interrupts       Interrupt Enable       n-masked periphoreripheral interrupt       erflow Interrupt Entrupt       TMR0 interrupt | e bit<br>heral interrupt<br>pts                                                                                         | R/W-0<br>RBIE                                                                                                                                                        | R/W-0<br>T0IF                                                                                                                                                                                                                                | R/W-0<br>INTF                                                                                                                                                                                                            | R/W-x<br>RBIF<br>bit 0                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | bit 0                                                                                                                                                                                                                                                                                      |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables all u<br>isables all in<br>Peripheral<br>nables all u<br>isables all p<br>TMR0 Ove<br>nables the<br>isables the       | n-masked interru<br>nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>rflow Interrupt En<br>TMR0 interrupt                                                                                       | e bit<br>heral interrupt<br>pts                                                                                         | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables all in<br>Peripheral<br>nables all un<br>sables all p<br>TMR0 Ove<br>nables the T<br>isables the                      | nterrupts<br>Interrupt Enable<br>n-masked periph<br>peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                          | e bit<br>heral interrupt<br>pts                                                                                         | s                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables all u<br>sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                         | n-masked periph<br>peripheral interru<br>rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                            | neral interrupt<br>pts                                                                                                  | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables all p<br>TMR0 Ove<br>nables the<br>sables the                                                                         | peripheral interru<br>erflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                              | pts                                                                                                                     | S                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| TMR0 Ove<br>nables the<br>sables the                                                                                         | rflow Interrupt Er<br>TMR0 interrupt                                                                                                                                                                                     |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| nables the<br>isables the                                                                                                    | TMR0 interrupt                                                                                                                                                                                                           | nable bit                                                                                                               |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| sables the                                                                                                                   |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | I MRU interrupt                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | External Interrupt                                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB0/INT externa<br>RB0/INT externa                                                                                                                                                                                       |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | hange Interrupt E                                                                                                                                                                                                        |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB port change i                                                                                                                                                                                                         |                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              | RB port change                                                                                                                                                                                                           | •                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| TMR0 Ove                                                                                                                     | rflow Interrupt Fl                                                                                                                                                                                                       | ag bit                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| MR0 registe                                                                                                                  | er has overflowed                                                                                                                                                                                                        | d (must be cle                                                                                                          | eared in soft                                                                                                                                                        | ware)                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| MR0 registe                                                                                                                  | er did not overflov                                                                                                                                                                                                      | W                                                                                                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| RB0/INT E                                                                                                                    | xternal Interrupt                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

|                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                         |                                                                                                                                                                      | red in softwa                                                                                                                                                                                                                                | are)                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                            |

| RB Port Cl                                                                                                                   | hange Interrupt F                                                                                                                                                                                                        | Flag bit                                                                                                                |                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                            |

| 'hen at leas                                                                                                                 |                                                                                                                                                                                                                          | •                                                                                                                       | -                                                                                                                                                                    | (must be cle                                                                                                                                                                                                                                 | ared in softw                                                                                                                                                                                                            | ware)                                                                                                                                                                                                                                                                                      |

|                                                                                                                              | ne RB0/INT<br>ne RB0/INT<br>RB Port C<br>hen at leas                                                                                                                                                                     | ne RB0/INT external interrune<br>RB0/INT external interrun<br>RB Port Change Interrupt I<br>hen at least one of the RB< | ne RB0/INT external interrupt did not occ<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins cha<br>one of the RB<7:4> pins have changed s | ne RB0/INT external interrupt occurred (must be clea<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state<br>one of the RB<7:4> pins have changed state | ne RB0/INT external interrupt occurred (must be cleared in softwa<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cle | ne RB0/INT external interrupt occurred (must be cleared in software)<br>ne RB0/INT external interrupt did not occur<br>RB Port Change Interrupt Flag bit<br>hen at least one of the RB<7:4> pins changed state (must be cleared in softwore)<br>one of the RB<7:4> pins have changed state |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH) |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 4.2.2.4 PIE1 Register

This register contains the individual enable bit for the comparator interrupt.

| <b>REGISTER 4-4:</b> | PIE1 REGISTER (ADDRESS 8CH)                                                                                                                       |            |          |     |     |     |     |       |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|-----|-----|-----|-----|-------|

|                      | U-0                                                                                                                                               | R/W-0      | U-0      | U-0 | U-0 | U-0 | U-0 | U-0   |

|                      |                                                                                                                                                   | CMIE       | _        |     |     | —   | _   | —     |

|                      | bit 7                                                                                                                                             |            |          |     |     |     |     | bit 0 |

| bit 7                | Unimpleme                                                                                                                                         | nted: Read | d as '0' |     |     |     |     |       |

| bit 6                | <b>CMIE</b> : Comparator Interrupt Enable bit<br>1 = Enables the Comparator interrupt<br>0 = Disables the Comparator interrupt                    |            |          |     |     |     |     |       |

| bit 5-0              | Unimpleme                                                                                                                                         | nted: Read | d as '0' |     |     |     |     |       |

|                      | Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |            |          |     |     |     |     |       |

## 4.2.2.5 PIR1 Register

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of |

|-------|--------------------------------------------------------------------------------------------|

|       | its corresponding enable bit or the global<br>enable bit, GIE (INTCON<7>). User            |

|       | software should ensure the appropriate                                                     |

|       | interrupt flag bits are clear prior to enabling                                            |

|       | an interrupt.                                                                              |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

| ER 4-5: | PIRT REGI                            | IRI REGISTER (ADDRESS UCH) |          |              |              |           |                |        |  |  |

|---------|--------------------------------------|----------------------------|----------|--------------|--------------|-----------|----------------|--------|--|--|

|         | U-0                                  | R/W-0                      | U-0      | U-0          | U-0          | U-0       | U-0            | U-0    |  |  |

|         |                                      | CMIF                       |          | —            | _            |           |                |        |  |  |

|         | bit 7                                |                            |          |              |              |           |                | bit 0  |  |  |

|         |                                      |                            |          |              |              |           |                |        |  |  |

| bit 7   | Unimpleme                            | ented: Rea                 | d as '0' |              |              |           |                |        |  |  |

| bit 6   | CMIF: Comparator Interrupt Flag bit  |                            |          |              |              |           |                |        |  |  |

|         | 1 = Comparator input has changed     |                            |          |              |              |           |                |        |  |  |

|         | 0 = Comparator input has not changed |                            |          |              |              |           |                |        |  |  |

| bit 5-0 | Unimplemented: Read as '0'           |                            |          |              |              |           |                |        |  |  |

|         |                                      |                            |          |              |              |           |                |        |  |  |

|         | Legend:                              |                            |          |              |              |           |                |        |  |  |

|         | R = Readab                           | ole bit                    | W = W    | /ritable bit | U = Unim     | plemented | bit, read as ' | 0'     |  |  |

|         | - n = Value                          | at POR                     | '1' = B  | it is set    | '0' = Bit is | s cleared | x = Bit is u   | nknown |  |  |

# 5.0 I/O PORTS

The PIC16C62X have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

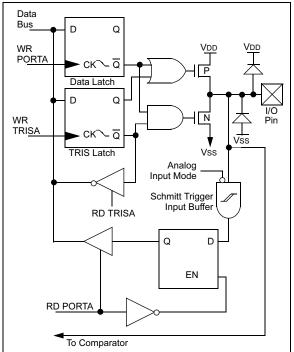

# 5.1 PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the T0CKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

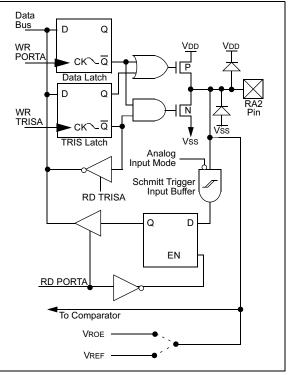

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (comparator control register) register and the VRCON (voltage reference control register) register. When selected as a comparator input, these pins will read as '0's.

#### FIGURE 5-1: BLOCK DIAGRAM OF RA1:RA0 PINS

| Note: | On RESET, the TRISA register is set to all  |

|-------|---------------------------------------------|

|       | inputs. The digital inputs are disabled and |

|       | the comparator inputs are forced to ground  |

|       | to reduce excess current consumption.       |

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output and must be buffered prior to any external load. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the Comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### EXAMPLE 5-1: INITIALIZING PORTA

| CLRF  | PORTA       | ;Initialize PORTA by setting<br>;output data latches |

|-------|-------------|------------------------------------------------------|

| MOVLW | 0X07        | ;Turn comparators off and                            |

| MOVWF | CMCON       | ;enable pins for I/O<br>;functions                   |

| BSF   | STATUS, RPO | ;Select Bank1                                        |

| MOVLW | 0x1F        | ;Value used to initialize                            |

|       |             | ;data direction                                      |

| MOVWF | TRISA       | ;Set RA<4:0> as inputs                               |

|       |             | ;TRISA<7:5> are always                               |

|       |             | ;read as '0'.                                        |

# FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

#### TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown

Note 1: Shaded bits are not used by PORTB.

NOTES:

# 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

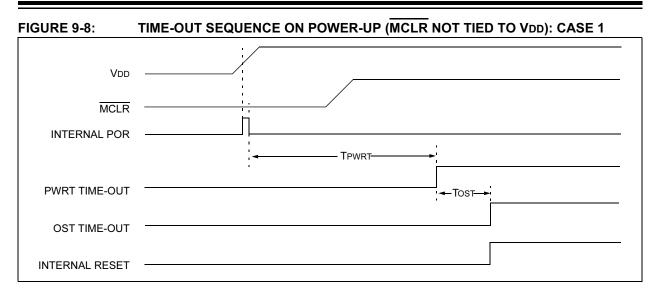

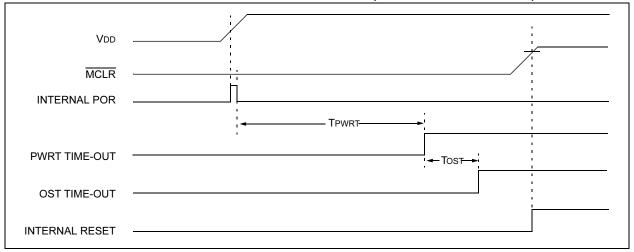

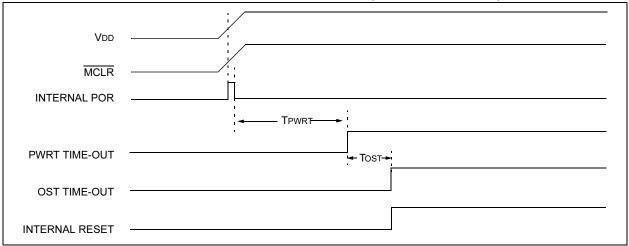

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

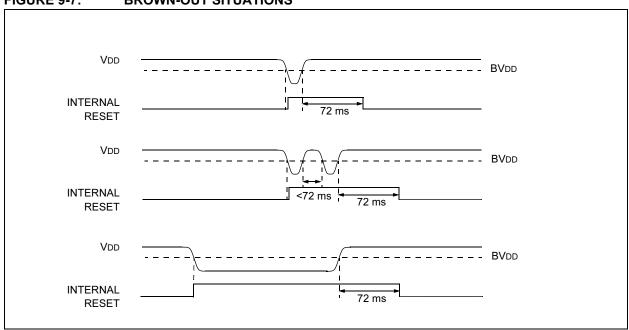

### 9.4.4 BROWN-OUT RESET (BOR)

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

### FIGURE 9-7: BROWN-OUT SITUATIONS

# PIC16C62X

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

# PIC16C62X

| INCFSZ                       | Increment f, Skip if 0                                                                                                                                                | IORWF            | Inclusive OR W with f                                                                                                                                                                                        |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                      | [ <i>label</i> ] INCFSZ f,d                                                                                                                                           | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                                                   |

| Operands:                    | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                    | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                           |

| Operation:                   | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                      | Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                                                            |

| Status Affected:             | None                                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                                                            |

| Encoding:                    | 00 1111 dfff ffff                                                                                                                                                     | Encoding:        | 00 0100 dfff ffff                                                                                                                                                                                            |

| Description:                 | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.                                        |

|                              | If the result is 0, the next instruc-<br>tion, which is already fetched, is                                                                                           | Words:           | 1                                                                                                                                                                                                            |

|                              | discarded. A NOP is executed                                                                                                                                          | Cycles:          | 1                                                                                                                                                                                                            |

|                              | instead making it a two-cycle                                                                                                                                         | Example          | IORWF RESULT, 0                                                                                                                                                                                              |

| Words:<br>Cycles:<br>Example | instruction.<br>1<br>1(2)<br>HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                       |                  | Before Instruction<br>$\begin{array}{rcl} \text{RESULT} &= & 0x13 \\ W &= & 0x91 \\ \end{array}$ After Instruction<br>$\begin{array}{rcl} \text{RESULT} &= & 0x13 \\ W &= & 0x93 \\ Z &= & 1 \\ \end{array}$ |

|                              | Before Instruction                                                                                                                                                    | MOVLW            | Move Literal to W                                                                                                                                                                                            |

|                              | PC = address HERE<br>After Instruction                                                                                                                                | Syntax:          | [ <i>label</i> ] MOVLW k                                                                                                                                                                                     |

|                              | CNT = CNT + 1                                                                                                                                                         | Operands:        | $0 \le k \le 255$                                                                                                                                                                                            |

|                              | if CNT= 0,<br>PC = address CONTINUE                                                                                                                                   | Operation:       | $k \rightarrow (W)$                                                                                                                                                                                          |

|                              | if CNT≠ 0,                                                                                                                                                            | Status Affected: | None                                                                                                                                                                                                         |

|                              | PC = address HERE +1                                                                                                                                                  | Encoding:        | 11 00xx kkkk kkkk                                                                                                                                                                                            |

| IORLW                        | Inclusive OR Literal with W                                                                                                                                           | Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's.                                                                                                             |

| Syntax:                      | [ <i>label</i> ] IORLW k                                                                                                                                              | Words:           | 1                                                                                                                                                                                                            |

| Operands:                    | $0 \le k \le 255$                                                                                                                                                     | Cycles:          | 1                                                                                                                                                                                                            |

| Operation:                   | (W) .OR. $k \rightarrow$ (W)                                                                                                                                          | Example          | MOVLW 0x5A                                                                                                                                                                                                   |

| Status Affected:             | Z                                                                                                                                                                     | Example          | After Instruction                                                                                                                                                                                            |

| Encoding:                    | 11 1000 kkkk kkkk                                                                                                                                                     |                  | W = 0x5A                                                                                                                                                                                                     |

| Description:                 | The contents of the W register is<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register.                                              |                  |                                                                                                                                                                                                              |

| Words:                       | 1                                                                                                                                                                     |                  |                                                                                                                                                                                                              |

| Cycles:                      | 1                                                                                                                                                                     |                  |                                                                                                                                                                                                              |

| Example                      | IORLW 0x35                                                                                                                                                            |                  |                                                                                                                                                                                                              |

|                              |                                                                                                                                                                       |                  |                                                                                                                                                                                                              |

|                              | Before Instruction<br>W = 0x9A<br>After Instruction                                                                                                                   |                  |                                                                                                                                                                                                              |

W = Z =

0xBF 1

| SUBLW        | Subtract W from Literal                                                       | SUBWF               | Subtract W from f                                                              |

|--------------|-------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------|

| Syntax:      | [ <i>label</i> ] SUBLW k                                                      | Syntax:             | [ <i>label</i> ] SUBWF f,d                                                     |

| Operands:    | $0 \le k \le 255$                                                             | Operands:           | $0 \le f \le 127$                                                              |

| Operation:   | $k - (W) \rightarrow (W)$                                                     |                     | d ∈ [0,1]                                                                      |

| Status       | C, DC, Z                                                                      | Operation:          | (f) - (W) $\rightarrow$ (dest)                                                 |

| Affected:    |                                                                               | Status<br>Affected: | C, DC, Z                                                                       |

| Encoding:    | 11 110x kkkk kkkk                                                             |                     |                                                                                |

| Description: | The W register is subtracted (2's                                             | Encoding:           | 00 0010 dfff ffff                                                              |

|              | complement method) from the eight<br>bit literal 'k'. The result is placed in | Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0, |

|              | the W register.                                                               |                     | the result is stored in the W register.                                        |

| Words:       | 1                                                                             |                     | If 'd' is 1, the result is stored back in                                      |

| Cycles:      | 1                                                                             |                     | register 'f'.                                                                  |

| Example 1:   | SUBLW 0x02                                                                    | Words:              | 1                                                                              |

| ·            | Before Instruction                                                            | Cycles:             | 1                                                                              |

|              | W = 1                                                                         | Example 1:          | SUBWF REG1,1                                                                   |

|              | C = ?                                                                         |                     | Before Instruction                                                             |

|              | After Instruction                                                             |                     | REG1= 3<br>W = 2                                                               |

|              | W = 1<br>C = 1; result is positive                                            |                     | C = ?                                                                          |

| Example 2:   | Before Instruction                                                            |                     | After Instruction                                                              |

| Example 2.   | W = 2                                                                         |                     | REG1= 1                                                                        |

|              | C = ?                                                                         |                     | W = 2<br>C = 1; result is positive                                             |

|              | After Instruction                                                             | Example 2:          | Before Instruction                                                             |

|              | W = 0                                                                         | ·                   | REG1= 2                                                                        |

|              | C = 1; result is zero                                                         |                     | W = 2                                                                          |

| Example 3:   | Before Instruction                                                            |                     | C = ?                                                                          |

|              | W = 3<br>C = ?                                                                |                     | After Instruction                                                              |

|              | After Instruction                                                             |                     | REG1= 0<br>W = 2                                                               |

|              | W = 0 x FF                                                                    |                     | C = 1; result is zero                                                          |

|              | C = 0; result is negative                                                     | Example 3:          | Before Instruction                                                             |

|              |                                                                               |                     | REG1= 1                                                                        |

|              |                                                                               |                     | W = 2<br>C = ?                                                                 |

|              |                                                                               |                     | After Instruction                                                              |

|              |                                                                               |                     | REG1= 0xFF                                                                     |

|              |                                                                               |                     | W = 2                                                                          |

|              |                                                                               |                     | C = 0; result is negative                                                      |

# PIC16C62X

## 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended)