Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

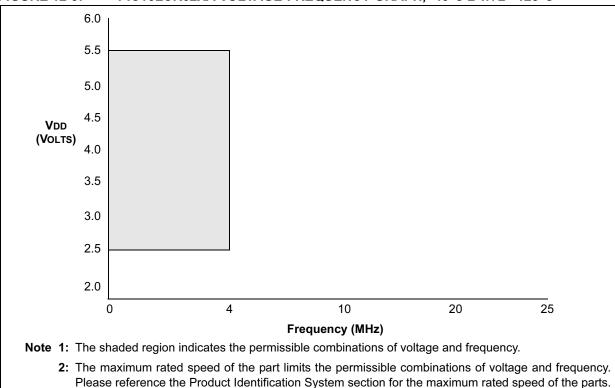

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 80 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc621-04i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16C62X devices are 18 and 20-Pin ROM/ EPROM-based members of the versatile PICmicro<sup>®</sup> family of low cost, high performance, CMOS, fullystatic, 8-bit microcontrollers.

All PICmicro microcontrollers employ an advanced RISC architecture. The PIC16C62X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16C62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16C620A, PIC16C621A and PIC16CR620A have 96 bytes of RAM. The PIC16C622(A) has 128 bytes of RAM. Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16C62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16C62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and RESET.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost effective One-Time-Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16C62X midrange microcontroller families.

A simplified block diagram of the PIC16C62X is shown in Figure 3-1.

The PIC16C62X series fits perfectly in applications ranging from battery chargers to low power remote sensors. The EPROM technology makes

customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C62X very versatile.

#### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to PIC16C62X family of devices (Appendix B). The PIC16C62X family fills the niche for users wanting to migrate up from the PIC16C5X family and not needing various peripheral features of other members of the PIC16XX mid-range microcontroller family.

#### 1.2 Development Support

The PIC16C62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. Third Party "C" compilers are also available.

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1).                                |

|         | R/W-1                    | R/W-1                          | R/W-1                         | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |  |  |

|---------|--------------------------|--------------------------------|-------------------------------|------------------------------|---------------|-------|-------|-------|--|--|

|         | RBPU                     | INTEDG                         | TOCS                          | TOSE                         | PSA           | PS2   | PS1   | PS0   |  |  |

|         | bit 7                    |                                |                               |                              |               | •     |       | bit 0 |  |  |

| bit 7   | RBPU: PO                 | RTB Pull-u                     | p Enable bi                   | it                           |               |       |       |       |  |  |

|         |                          | 3 pull-ups ai<br>3 pull-ups ai |                               | y individual                 | port latch va | alues |       |       |  |  |

| bit 6   | INTEDG: I                | nterrupt Edg                   | e Select bit                  | -                            |               |       |       |       |  |  |

|         |                          |                                | edge of RB0<br>edge of RB0    |                              |               |       |       |       |  |  |

| bit 5   | TOCS: TMI                | R0 Clock Sc                    | ource Select                  | bit                          |               |       |       |       |  |  |

|         |                          | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock      | (CLKOUT)                     |               |       |       |       |  |  |

| bit 4   | TOSE: TM                 | R0 Source E                    | Edge Select                   | bit                          |               |       |       |       |  |  |

|         |                          |                                |                               | ition on RA4<br>ition on RA4 |               |       |       |       |  |  |

| bit 3   | PSA: Pres                | caler Assigr                   | iment bit                     |                              | -             |       |       |       |  |  |

|         |                          |                                | ned to the W<br>ned to the Ti | DT<br>mer0 module            | Э             |       |       |       |  |  |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : [ | Prescaler Ra                   | ate Select bi                 | ts                           |               |       |       |       |  |  |

|         | E                        | Bit Value T                    | MR0 Rate                      | WDT Rate                     |               |       |       |       |  |  |

|         | -                        | 000<br>001                     | 1:2<br>1:4                    | 1:1<br>1:2                   |               |       |       |       |  |  |

|         |                          | 010<br>011                     | 1 : 8<br>1 : 16               | 1:4<br>1:8                   |               |       |       |       |  |  |

|         |                          | 100                            | 1:32                          | 1:16                         |               |       |       |       |  |  |

|         |                          | 101                            | 1:64                          | 1:32                         |               |       |       |       |  |  |

|         | 110 1:128 1:64           |                                |                               |                              |               |       |       |       |  |  |

|         |                          | 111                            | 1:256                         | 1 : 128                      |               |       |       |       |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

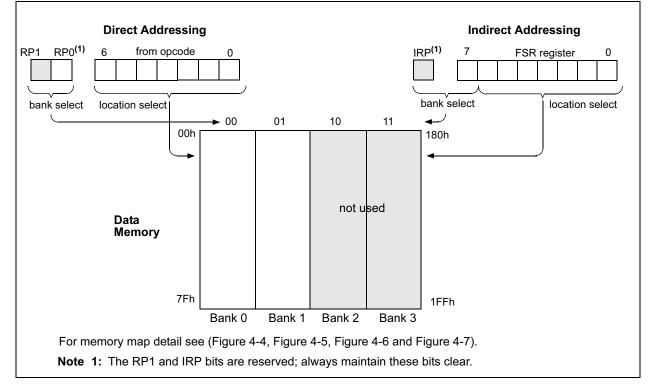

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-9. However, IRP is not used in the PIC16C62X.

A simple program to clear RAM location 20h-7Fh using indirect addressing is shown in Example 4-1.

| EXAN      | IPLE 4- | 1: INC | DIRECT ADDRESSING    |  |  |  |  |

|-----------|---------|--------|----------------------|--|--|--|--|

|           | movlw   | 0x20   | ;initialize pointer  |  |  |  |  |

|           | movwf   | FSR    | ;to RAM              |  |  |  |  |

| NEXT      | clrf    | INDF   | ;clear INDF register |  |  |  |  |

|           | incf    | FSR    | ;inc pointer         |  |  |  |  |

|           | btfss   | FSR,7  | ;all done?           |  |  |  |  |

|           | goto    | NEXT   | ;no clear next       |  |  |  |  |

|           |         |        | ;yes continue        |  |  |  |  |

| CONTINUE: |         |        |                      |  |  |  |  |

|           |         |        |                      |  |  |  |  |

#### FIGURE 4-9: DIRECT/INDIRECT ADDRESSING PIC16C62X

#### TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

## 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

#### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                             |               | <b>(</b> | ,   |       |       |       |       |  |

|---------|-----------------------------|---------------|----------|-----|-------|-------|-------|-------|--|

|         | R-0                         | R-0           | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|         | C2OUT                       | C10UT         | —        | —   | CIS   | CM2   | CM1   | CM0   |  |

|         | bit 7                       |               |          |     |       |       |       | bit 0 |  |

|         |                             |               |          |     |       |       |       |       |  |

| bit 7   | <b>C2OUT</b> : Co           | omparator 2   | output   |     |       |       |       |       |  |

|         | 1 = C2 VIN                  | + > C2 VIN-   |          |     |       |       |       |       |  |

|         | 0 = C2 VIN                  | + < C2 VIN-   |          |     |       |       |       |       |  |

| bit 6   | C10UT: Co                   | omparator 1   | output   |     |       |       |       |       |  |

|         | 1 = C1 VIN                  | + > C1 VIN-   |          |     |       |       |       |       |  |

|         | 0 = C1 VIN                  | + < C1 VIN-   |          |     |       |       |       |       |  |

| bit 5-4 | Unimplem                    | ented: Read   | d as '0' |     |       |       |       |       |  |

| bit 3   | CIS: Comp                   | arator Input  | Switch   |     |       |       |       |       |  |

|         | When CM<                    | <2:0>: = 001  | :        |     |       |       |       |       |  |

|         | 1 = C1 VIN-                 | - connects to | o RA3    |     |       |       |       |       |  |

|         | 0 = C1 VIN                  | - connects to | o RA0    |     |       |       |       |       |  |

|         | When CM<                    | <2:0> = 010:  |          |     |       |       |       |       |  |

|         | 1 = C1 VIN- connects to RA3 |               |          |     |       |       |       |       |  |

|         | C2 VIN- connects to RA2     |               |          |     |       |       |       |       |  |

|         | 0 = C1 VIN- connects to RA0 |               |          |     |       |       |       |       |  |

|         | C2 VIN                      | I- connects t | 0 RA1    |     |       |       |       |       |  |

| bit 2-0 | CM<2:0>: Comparator mode.   |               |          |     |       |       |       |       |  |

|         |                             |               |          |     |       |       |       |       |  |

|         | Legend:                     |               |          |     |       |       |       |       |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1              | CP0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CP1                                                                                                                                                                                                                      | CP0 <sup>(2)</sup> | CP1     | CP0 <sup>(2)</sup>    |        | BODEN    | CP1     | CP0 <sup>(2)</sup> | PWRTE       | WDTE     | F0SC1 | F0SC0 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-----------------------|--------|----------|---------|--------------------|-------------|----------|-------|-------|

| bit 13           | ļ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u> </u>                                                                                                                                                                                                                 | ļļ                 |         | ļ                     |        | <u> </u> | <u></u> | <u>I</u>           | <u></u>     | <u> </u> | ļ     | bit 0 |

| bit 13-8<br>5-4: | bit 13-8, <b>CP&lt;1:0&gt;:</b> Code protection bit pairs <sup>(2)</sup><br>5-4: Code protection for 2K program memory<br>11 = Program memory code protection off<br>10 = 0400h-07FFh code protected<br>01 = 0200h-07FFh code protected<br>00 = 0000h-07FFh code protected<br>Code protection for 1K program memory<br>11 = Program memory code protection off<br>10 = Program memory code protection off<br>01 = 0200h-03FFh code protected<br>00 = 0000h-03FFh code protected<br>Code protection for 0.5K program memory<br>11 = Program memory code protection off<br>10 = Program memory code protected |                                                                                                                                                                                                                          |                    |         |                       |        |          |         |                    |             |          |       |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                        | m memo<br>-01FFh c |         |                       | on off |          |         |                    |             |          |       |       |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                          | nted: Re           | -       |                       |        |          |         |                    |             |          |       |       |

| bit 6            | BOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DEN: Br                                                                                                                                                                                                                  | own-out l          | Reset E | nable bit             | (1)    |          |         |                    |             |          |       |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BOR en<br>BOR dis                                                                                                                                                                                                        |                    |         |                       |        |          |         |                    |             |          |       |       |

| bit 3            | 1 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>RTE</b> : Po<br>PWRT o<br>PWRT e                                                                                                                                                                                      |                    | īmer Er | able bit <sup>(</sup> | 1, 3)  |          |         |                    |             |          |       |       |

| bit 2            | 1 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                   |                    |         |                       |        |          |         |                    |             |          |       |       |

| bit 1-0          | <ul> <li>FOSC1:FOSC0: Oscillator Selection bits</li> <li>11 = RC oscillator</li> <li>10 = HS oscillator</li> <li>01 = XT oscillator</li> <li>00 = LP oscillator</li> <li>Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Detect Reset is</li> </ul>                                                                                                                                                                                                                               |                                                                                                                                                                                                                          |                    |         |                       |        |          |         |                    |             |          |       |       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>enabled.</li> <li>2: All of the CP&lt;1:0&gt; pairs have to be given the same value to enable the code protection scheme listed.</li> <li>3: Unprogrammed parts default the Power-up Timer disabled.</li> </ul> |                    |         |                       |        |          |         | cheme              |             |          |       |       |

| Legend<br>R = Re | l:<br>adable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | it                                                                                                                                                                                                                       |                    | W =     | Writable              | bit    | U =      | Unimple | emented            | bit, read a | s '0'    |       |       |

#### 9.5 Interrupts

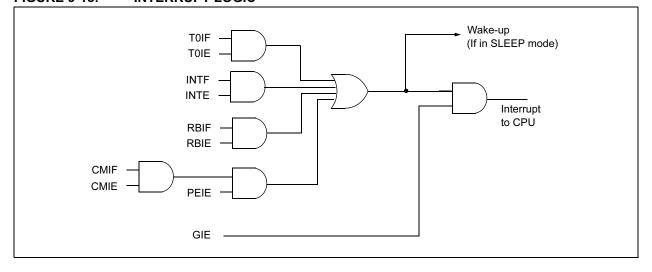

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

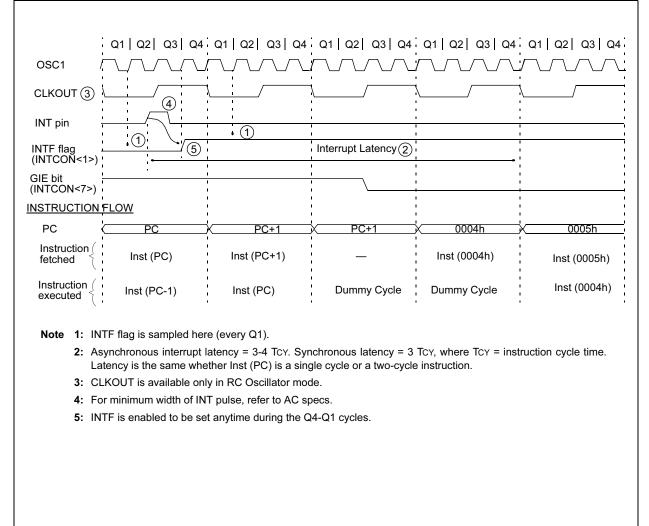

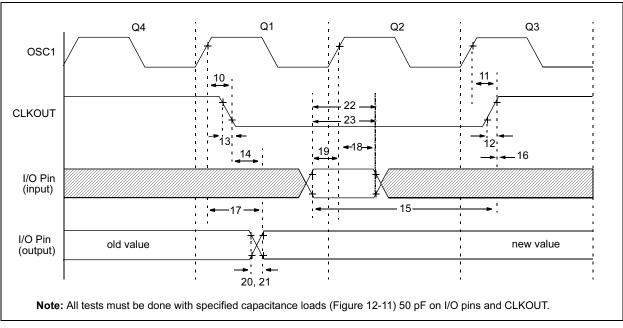

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

#### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

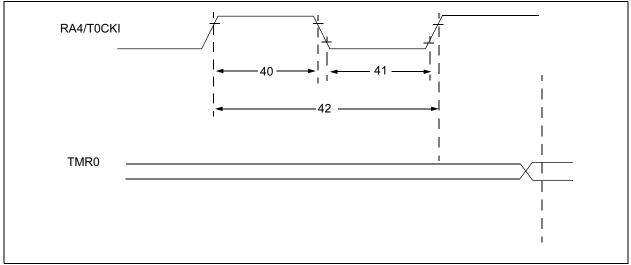

#### 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

#### FIGURE 9-16: INT PIN INTERRUPT TIMING

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in$ [0,1]                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two-cycle<br>instruction. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                  | $\begin{array}{rcl} PC &=& address \ {\tt HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \ {\tt CONTINUE} \\ \mbox{if CNT} \neq& 0, \\ PC &=& address \ {\tt HERE} + 1 \\ \end{array}$                                                                                                 |  |  |  |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Encoding:        | 10 1kkk kkkk kkkk                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction.                                                                                                                                      |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Example          | GOTO THERE                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|                  | After Instruction<br>PC = Address THERE                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                            |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                              |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                     |  |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                                  |  |  |  |  |  |  |  |  |

| SWAPF            | Swap Ni                                                                                                                                                                    | bbles in  | f     |              |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|--------------|--|--|--|--|--|

| Syntax:          | [label]                                                                                                                                                                    | SWAPF     | f,d   |              |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                         |           |       |              |  |  |  |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                                                                                                                                   |           | · · · |              |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                       |           |       |              |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                         | 1110      | dfff  | ffff         |  |  |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |           |       |              |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                          |           |       |              |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                          |           |       |              |  |  |  |  |  |

| Example          | SWAPF                                                                                                                                                                      | REG,      | 0     |              |  |  |  |  |  |

|                  | Before In                                                                                                                                                                  | struction |       |              |  |  |  |  |  |

|                  |                                                                                                                                                                            | REG1      | = (   | DxA5         |  |  |  |  |  |

|                  | After Inst                                                                                                                                                                 | ruction   |       |              |  |  |  |  |  |

|                  |                                                                                                                                                                            | REG1<br>W |       | 0xA5<br>0x5A |  |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |  |  |  |  |

| XORLW                                                                                                    | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Syntax:                                                                                                  | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| Operands:                                                                                                | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| Operation:                                                                                               | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| Encoding:                                                                                                | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| Description:                                                                                             | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| Example:                                                                                                 | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

|                                                                                                          | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

|                                                                                                          | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|                                                                                                          | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| XORWF                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

|                                                                                                          | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

| Syntax:                                                                                                  | [label] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| Syntax:                                                                                                  | [ <i>label</i> ] XORWF f,d $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                     | $ \begin{array}{ll} \textit{[label]} & XORWF & f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \end{array} $                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                                       | $ \begin{array}{ll} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) & \text{XOR.} & (\textit{f}) \rightarrow (\textit{dest}) \end{array} $                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{c c} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) . \text{XOR.} (\textit{f}) \rightarrow (\text{dest}) \\ \hline Z \\ \hline \hline 00 & 0110 & \text{dfff} & \text{ffff} \\ \hline \text{Exclusive OR the contents of the} \\ W \text{ register with register 'f'. If 'd' is} \\ 0, \text{ the result is stored in the W} \\ \text{register. If 'd' is 1, the result is} \end{array}$                       |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00 \qquad 0110 \qquad dfff \qquad ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'.                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $[label] XORWF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00  0110  dfff  ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z<br>00 0110 dfff ffff<br>Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is<br>0, the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'.<br>1<br>1                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF REG 1 \\ \end{bmatrix}$                                                                                    |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ REG & = 0xAF \\ \end{bmatrix}$                      |  |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ \hline REG &= 0xAF \\ W &= 0xB5 \\ \end{bmatrix}$ |  |  |  |  |  |  |  |  |  |  |

#### 11.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

### 11.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PICmicro microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature on-board LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three micro-controllers are programmed with firmware to provide LIN bus communication.

## 11.22 PICkit<sup>™</sup> 1 FLASH Starter Kit

A complete "development system in a box", the PICkit FLASH Starter Kit includes a convenient multi-section board for programming, evaluation, and development of 8/14-pin FLASH PIC<sup>®</sup> microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB<sup>®</sup> IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin FLASH PIC<sup>®</sup> Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin FLASH PIC microcontrollers, as well as many future planned devices.

### 11.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

### 11.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

## 12.0 ELECTRICAL SPECIFICATIONS

#### Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                 | 40° to +125°C                  |

|----------------------------------------------------------------------------------------------------------------|--------------------------------|

| Storage Temperature                                                                                            | 65° to +150°C                  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | 0.6V to VDD +0.6V              |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.5V                     |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                      |