Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                             |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 96 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc621a-04e-so |

TABLE 1-1: PIC16C62X FAMILY OF DEVICES

|             |                                        | PIC16C620 <sup>(3)</sup>            | PIC16C620A <sup>(1)(4)</sup>        | PIC16CR620A <sup>(2)</sup>          | PIC16C621 <sup>(3)</sup>            | PIC16C621A <sup>(1)(4)</sup>        | PIC16C622 <sup>(3)</sup>            | PIC16C622A <sup>(1)(4)</sup>        |

|-------------|----------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)   | 20                                  | 40                                  | 20                                  | 20                                  | 40                                  | 20                                  | 40                                  |

| Memory      | EPROM Program<br>Memory<br>(x14 words) | 512                                 | 512                                 | 512                                 | 1K                                  | 1K                                  | 2K                                  | 2K                                  |

|             | Data Memory (bytes)                    | 80                                  | 96                                  | 96                                  | 80                                  | 96                                  | 128                                 | 128                                 |

| Peripherals | Timer Module(s)                        | TMR0                                | TMR0                                | TMRO                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

|             | Comparators(s)                         | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   | 2                                   |

|             | Internal Reference<br>Voltage          | Yes                                 |

| Features    | Interrupt Sources                      | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   | 4                                   |

|             | I/O Pins                               | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  | 13                                  |

|             | Voltage Range (Volts)                  | 2.5-6.0                             | 2.7-5.5                             | 2.5-5.5                             | 2.5-6.0                             | 2.7-5.5                             | 2.5-6.0                             | 2.7-5.5                             |

|             | Brown-out Reset                        | Yes                                 |

|             | Packages                               | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

All PICmicro® Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C62X Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

- 2: For ROM parts, operation from 2.0V 2.5V will require the PIC16LCR62XA parts.

- **3:** For OTP parts, operation from 2.5V 3.0V will require the PIC16LC62X part.

- 4: For OTP parts, operation from 2.7V 3.0V will require the PIC16LC62XA part.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The Special Function Registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C62X

| Address | Name          | Bit 7               | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0    | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|---------------|---------------------|--------------------|-------------|--------------|--------------|--------------|-------------|----------|-----------------------|------------------------------------------------|

| Bank 0  |               |                     |                    |             |              |              |              |             |          |                       |                                                |

| 00h     | INDF          | Addressin register) | g this locati      | physical    | xxxx xxxx    | xxxx xxxx    |              |             |          |                       |                                                |

| 01h     | TMR0          | Timer0 Mo           | odule's Reg        | ister       |              |              |              |             |          | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program C           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |          | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С        | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da         | ata memory         | address po  | ointer       |              |              |             |          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         | _                   | _                  | _           | RA4          | RA3          | RA2          | RA1         | RA0      | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                 | RB6                | RB5         | RB4          | RB3          | RB2          | RB1         | RB0      | xxxx xxxx             | uuuu uuuu                                      |

| 07h-09h | Unimplemented |                     |                    |             |              |              |              |             |          | _                     | _                                              |

| 0Ah     | PCLATH        | _                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram cour  | nter     | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                 | PEIE               | TOIE        | INTE         | RBIE         | TOIF         | INTF        | RBIF     | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | _                   | CMIF               | _           | _            | _            | _            | _           | _        | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                     |                    |             |              |              |              |             |          | _                     | _                                              |

| 1Fh     | CMCON         | C2OUT               | C10UT              | _           | _            | CIS          | CM2          | CM1         | CM0      | 00 0000               | 00 0000                                        |

| Bank 1  |               |                     |                    |             |              |              |              |             |          |                       |                                                |

| 80h     | INDF          | Addressin register) | g this locati      | on uses co  | ntents of FS | SR to addre  | ss data me   | mory (not a | physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                | INTEDG             | T0CS        | T0SE         | PSA          | PS2          | PS1         | PS0      | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program C           | Counter's (F       | PC) Least S | ignificant B | yte          |              |             |          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP <sup>(2)</sup>  | RP1 <sup>(2)</sup> | RP0         | TO           | PD           | Z            | DC          | С        | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da         | ata memory         | address po  | ointer       | •            | •            | •           |          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                   | _                  | _           | TRISA4       | TRISA3       | TRISA2       | TRISA1      | TRISA0   | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7              | TRISB6             | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1      | TRISB0   | 1111 1111             | 1111 1111                                      |

| 87h-89h | Unimplemented |                     |                    |             |              |              |              |             |          | _                     | _                                              |

| 8Ah     | PCLATH        | _                   | _                  | _           | Write buffe  | er for upper | 5 bits of pr | ogram cour  | nter     | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                 | PEIE               | TOIE        | INTE         | RBIE         | T0IF         | INTF        | RBIF     | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                   | CMIE               | _           | _            | _            | _            | _           | _        | -0                    | -0                                             |

| 8Dh     | Unimplemented |                     |                    |             |              |              |              |             |          | _                     | _                                              |

| 8Eh     | PCON          | _                   | _                  | _           | _            | _            | _            | POR         | BOR      | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                     |                    |             |              |              |              |             |          | _                     |                                                |

| 9Fh     | VRCON         | VREN                | VROE               | VRR         | _            | VR3          | VR2          | VR1         | VR0      | 000- 0000             | 000- 0000                                      |

Legend: — = Unimplemented locations read as '0',  ${\tt u}$  = unchanged,  ${\tt x}$  = unknown,

q = value depends on condition, shaded = unimplemented

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

<sup>2:</sup> IRP & RP1 bits are reserved; always maintain these bits clear.

### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex., BCF, BSF, etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

# EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

```

; Initial PORT settings:

PORTB<7:4> Inputs

PORTB<3:0> Outputs

; PORTB<7:6> have external pull-up and are not

; connected to other circuitry

PORT latch PORT pins

BCF PORTB, 7

; 01pp pppp

11pp pppp

11pp

PORTB, 6

; 10pp

pppp

qqqq

BSF STATUS, RPO

TRISB, 7

; 10pp pppp

11pp pppp

BCF TRISB, 6

; 10pp pppp

10pp pppp

; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused

; RB7 to be latched as the pin value (High).

```

### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

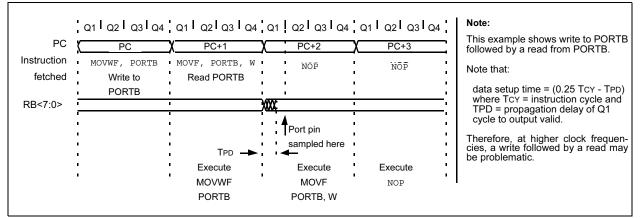

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

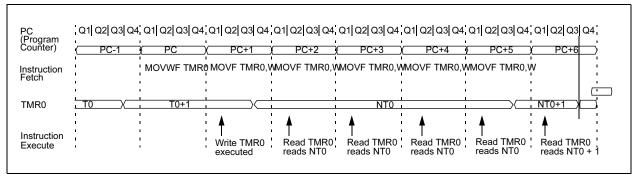

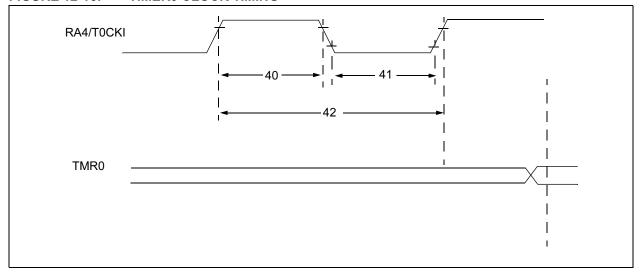

#### FIGURE 6-3: TIMERO TIMING: INTERNAL CLOCK/PRESCALE 1:2

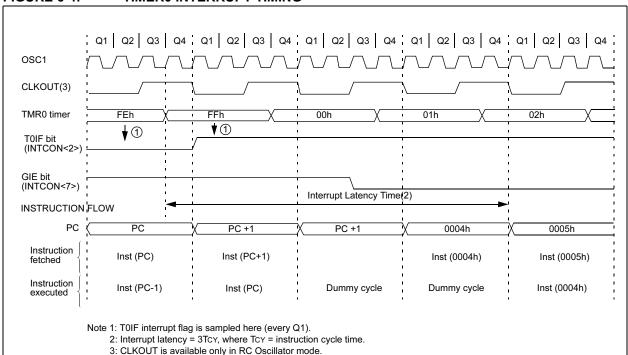

#### FIGURE 6-4: TIMERO INTERRUPT TIMING

### 8.0 VOLTAGE REFERENCE MODULE

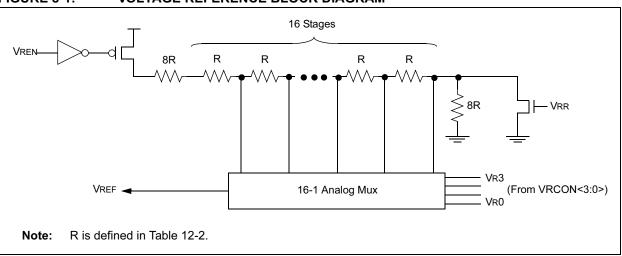

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 8-1. The block diagram is given in Figure 8-1.

### 8.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the Voltage Reference are as follows:

if

$$VRR = 0$$

:  $VREF = (VDD x 1/4) + (VR < 3:0 > /32) x VDD$

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 12-1). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

### REGISTER 8-1: VRCON REGISTER(ADDRESS 9Fh)

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-------|-------|-------|-------|

| VREN  | VROE  | VRR   | _   | VR3   | VR2   | VR1   | VR0   |

| bit 7 |       |       |     |       |       |       | bit 0 |

bit 7 VREN: VREF Enable

1 = VREF circuit powered on

0 = VREF circuit powered down, no IDD drain

bit 6 **VROE:** VREF Output Enable

1 = VREF is output on RA2 pin

0 = VREF is disconnected from RA2 pin

bit 5 VRR: VREF Range selection

1 = Low Range

0 = High Range

bit 4 Unimplemented: Read as '0'

bit 3-0 **VR<3:0>**: VREF value selection  $0 \le VR$  [3:0]  $\le 15$

when VRR = 1: VREF = (VR<3:0>/ 24) \* VDD

when VRR = 0: VREF = 1/4 \* VDD + (VR<3:0>/ 32) \* VDD

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### FIGURE 8-1: VOLTAGE REFERENCE BLOCK DIAGRAM

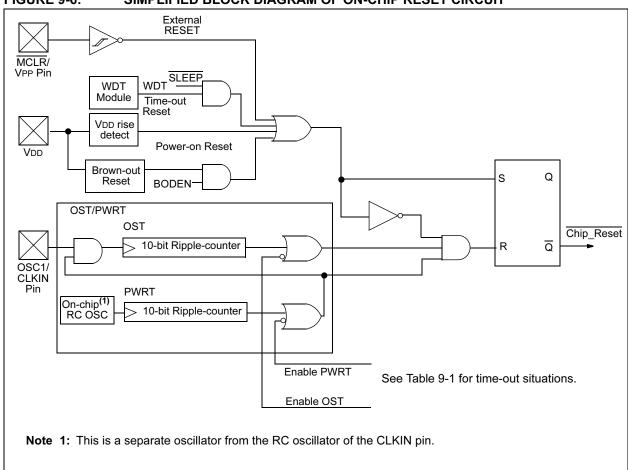

#### 9.3 RESET

The PIC16C62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOR)

Some registers are not affected in any RESET condition Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset,

MCLR Reset, WDT Reset and MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 9-2. These bits are used in software to determine the nature of the RESET. See Table 9-5 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 9-6.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 12-5 for pulse width specification.

#### FIGURE 9-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| MOVF             | Move f                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | The contents of register f is moved to a destination dependent upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Example          | MOVF FSR, 0                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                  | After Instruction  W = value in FSR  register  Z = 1                                                                                                                                                                                                    |  |  |  |  |  |  |

| Move W to f           |                                                                                        |       |                                              |                                                                                                                                                                                                                         |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------|-------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [label] MOVWF f       |                                                                                        |       |                                              |                                                                                                                                                                                                                         |  |  |  |

| $0 \le f \le 12$      | 27                                                                                     |       |                                              |                                                                                                                                                                                                                         |  |  |  |

| $(W) \rightarrow (f)$ | )                                                                                      |       |                                              |                                                                                                                                                                                                                         |  |  |  |

| None                  |                                                                                        |       |                                              |                                                                                                                                                                                                                         |  |  |  |

| 00                    | 0000                                                                                   | 1ff   | f                                            | ffff                                                                                                                                                                                                                    |  |  |  |

| Move dat ister 'f'.   | ta from V                                                                              | V reg | ister                                        | to reg-                                                                                                                                                                                                                 |  |  |  |

| 1                     |                                                                                        |       |                                              |                                                                                                                                                                                                                         |  |  |  |

| 1                     |                                                                                        |       |                                              |                                                                                                                                                                                                                         |  |  |  |

| MOVWF                 | OPTION                                                                                 | 1     |                                              |                                                                                                                                                                                                                         |  |  |  |

| After Inst            | OPTION<br>W<br>ruction<br>OPTION                                                       | =     | 0xFF<br>0x4F<br>0x4F                         | :                                                                                                                                                                                                                       |  |  |  |

|                       | [ label ] $0 \le f \le 12$ (W) → (f) None $00$ Move datister 'f'.  1  MOVWF  Before In |       | [label] MOVWF f f 0 ≤ f ≤ 127 (W) → (f) None | $ [label] MOVWF f $ $0 \le f \le 127 $ $(W) → (f) $ None $00 0000 1fff $ Move data from W register ister 'f'. $1$ $1$ $MOVWF OPTION$ Before Instruction $OPTION = 0xFF $ $W = 0x4F $ After Instruction $OPTION = 0x4F $ |  |  |  |

| NOP              | No Operation |        |      |      |  |  |  |  |

|------------------|--------------|--------|------|------|--|--|--|--|

| Syntax:          | [ label ]    | NOP    |      |      |  |  |  |  |

| Operands:        | None         |        |      |      |  |  |  |  |

| Operation:       | No operation |        |      |      |  |  |  |  |

| Status Affected: | None         |        |      |      |  |  |  |  |

| Encoding:        | 00           | 0000   | 0xx0 | 0000 |  |  |  |  |

| Description:     | No opera     | ation. |      |      |  |  |  |  |

| Words:           | 1            |        |      |      |  |  |  |  |

| Cycles:          | 1            |        |      |      |  |  |  |  |

| Example          | NOP          |        |      |      |  |  |  |  |

| OPTION               | Load Option Register                                                                          |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|

| Syntax:              | [ label ]                                                                                     | OPTION                                                    | ٧                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |  |  |  |  |

| Operands:            | None                                                                                          |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |

| Operation:           | $(W) \rightarrow O$                                                                           | PTION                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |

| Status Affected:     | None                                                                                          |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |

| Encoding:            | 00                                                                                            | 0000                                                      | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0010                                  |  |  |  |  |

| Description:  Words: | The contelloaded in This instructed comproducts able/writed directly a                        | the OPT<br>ruction is<br>apatibility<br>Since Cable regis | FION reging supported with PICO PTION is ster, the uncorrected to the properties of | ster.<br>ed for<br>16C5X<br>s a read- |  |  |  |  |

| Cycles:              | 1                                                                                             |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |

| Example              |                                                                                               |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 411.11                                |  |  |  |  |

|                      | To maintain upward compatibility with future PICmicro® products, do not use this instruction. |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |

|                      |                                                                                               |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |

| SUBLW               | Subtract W from Literal                                                                                                      | SUBWF                | Subtract W from f                                                                                                   |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ label ] SUBLW k                                                                                                            | Syntax:              | [ label ] SUBWF f,d                                                                                                 |

| Operands:           | $0 \leq k \leq 255$                                                                                                          | Operands:            | $0 \leq f \leq 127$                                                                                                 |

| Operation:          | $k - (W) \rightarrow (W)$                                                                                                    |                      | d ∈ [0,1]                                                                                                           |

| Status<br>Affected: | C, DC, Z                                                                                                                     | Operation:<br>Status | (f) - (W) $\rightarrow$ (dest)<br>C, DC, Z                                                                          |

| Encoding:           |                                                                                                                              | Affected:            | 0, 00, 2                                                                                                            |

| · ·                 | 11   110x   kkkk   kkkk                                                                                                      | Encoding:            | 00 0010 dfff ffff                                                                                                   |

| Description:        | The W register is subtracted (2's complement method) from the eight bit literal 'k'. The result is placed in the W register. | Description:         | Subtract (2's complement method) W register from register 'f'. If 'd' is 0, the result is stored in the W register. |

| Words:              | 1                                                                                                                            |                      | If 'd' is 1, the result is stored back in register 'f'.                                                             |

| Cycles:             | 1                                                                                                                            | Words:               | 1                                                                                                                   |

| Example 1:          | SUBLW 0x02                                                                                                                   | Cycles:              | 1                                                                                                                   |

|                     | Before Instruction                                                                                                           | Example 1:           |                                                                                                                     |

|                     | W = 1                                                                                                                        | Liample 1.           | SUBWF REG1, 1  Before Instruction                                                                                   |

|                     | C = ?                                                                                                                        |                      | REG1= 3                                                                                                             |

|                     | After Instruction                                                                                                            |                      | W = 2                                                                                                               |

|                     | W = 1<br>C = 1; result is positive                                                                                           |                      | C = ?                                                                                                               |

| Example 2:          | Before Instruction                                                                                                           |                      | After Instruction                                                                                                   |

| ·                   | W = 2<br>C = ?                                                                                                               |                      | REG1= 1<br>W = 2<br>C = 1; result is positive                                                                       |

|                     | After Instruction                                                                                                            | Example 2:           | Before Instruction                                                                                                  |

|                     | W = 0                                                                                                                        |                      | REG1= 2                                                                                                             |

| Example 3:          | C = 1; result is zero  Before Instruction                                                                                    |                      | W = 2<br>C = ?                                                                                                      |

| Zxampio o.          | W = 3                                                                                                                        |                      | After Instruction                                                                                                   |

|                     | C = ?                                                                                                                        |                      | REG1= 0                                                                                                             |

|                     | After Instruction                                                                                                            |                      | W = 2<br>C = 1; result is zero                                                                                      |

|                     | W = 0xFF<br>C = 0; result is negative                                                                                        | Example 3:           | Before Instruction                                                                                                  |

|                     | 5, 100an 10 nogamo                                                                                                           | ·                    | REG1= 1<br>W = 2                                                                                                    |

|                     |                                                                                                                              |                      | VV - 2<br>C = ?                                                                                                     |

|                     |                                                                                                                              |                      | After Instruction                                                                                                   |

|                     |                                                                                                                              |                      | REG1= 0xFF<br>W = 2<br>C = 0; result is negative                                                                    |

NOTES:

### 11.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

### 11.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PICmicro microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature on-board LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three microcontrollers are programmed with firmware to provide LIN bus communication.

#### 11.22 PICkit<sup>™</sup> 1 FLASH Starter Kit

A complete "development system in a box", the PICkit FLASH Starter Kit includes a convenient multi-section board for programming, evaluation, and development of 8/14-pin FLASH PIC® microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB® IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin FLASH PIC® Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin FLASH PIC microcontrollers, as well as many future planned devices.

### 11.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

### 11.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- · Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

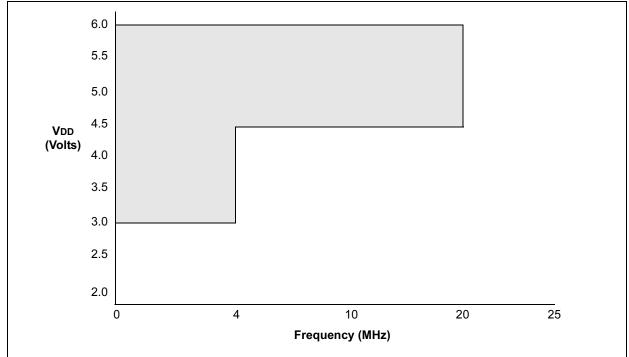

FIGURE 12-1: PIC16C62X VOLTAGE-FREQUENCY GRAPH, -40°C ≤ TA ≤ +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

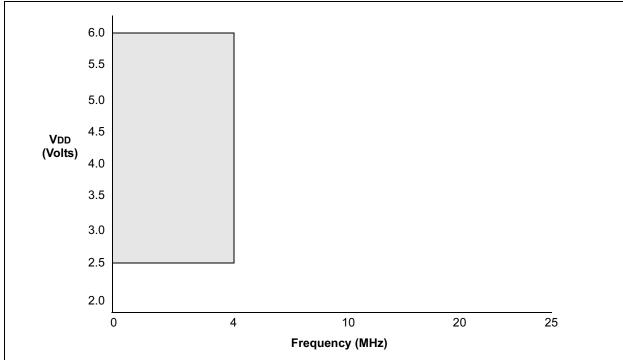

FIGURE 12-2: PIC16LC62X VOLTAGE-FREQUENCY GRAPH, -40°C ≤ TA ≤ +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

# 12.3 DC CHARACTERISTICS: PIC16CR62XA-04 (Commercial, Industrial, Extended) PIC16CR62XA-20 (Commercial, Industrial, Extended) PIC16LCR62XA-04 (Commercial, Industrial, Extended)

| PIC16CR62XA-04<br>PIC16CR62XA-20 |      |                                              | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for industrial and $0^{\circ}\text{C} \leq \text{Ta} \leq +70^{\circ}\text{C}$ for commercial and $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ for extended |            |      |            |                                                                                                                                                                                                                                                                        |  |  |  |

|----------------------------------|------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIC16LCR62XA-04                  |      |                                              |                                                                                                                                                                                                                                                                                                                            |            |      | ature -    | nditions (unless otherwise stated) $40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial and $0^{\circ}\text{C} \le \text{TA} \le +70^{\circ}\text{C}$ for commercial and $40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |  |  |  |

| Param.<br>No.                    | Sym  | Characteristic                               | Min                                                                                                                                                                                                                                                                                                                        | Тур†       | Max  | Units      | Conditions                                                                                                                                                                                                                                                             |  |  |  |

| D001                             | VDD  | Supply Voltage                               | 3.0                                                                                                                                                                                                                                                                                                                        | _          | 5.5  | V          | See Figures 12-7, 12-8, 12-9                                                                                                                                                                                                                                           |  |  |  |

| D001                             | VDD  | Supply Voltage                               | 2.5                                                                                                                                                                                                                                                                                                                        | _          | 5.5  | V          | See Figures 12-7, 12-8, 12-9                                                                                                                                                                                                                                           |  |  |  |

| D002                             | VDR  | RAM Data Retention<br>Voltage <sup>(1)</sup> | _                                                                                                                                                                                                                                                                                                                          | 1.5*       | _    | V          | Device in SLEEP mode                                                                                                                                                                                                                                                   |  |  |  |

| D002                             | VDR  | RAM Data Retention<br>Voltage <sup>(1)</sup> | _                                                                                                                                                                                                                                                                                                                          | 1.5*       | _    | V          | Device in SLEEP mode                                                                                                                                                                                                                                                   |  |  |  |

| D003                             | VPOR | VDD start voltage to ensure Power-on Reset   | _                                                                                                                                                                                                                                                                                                                          | Vss        | _    | V          | See section on Power-on Reset for details                                                                                                                                                                                                                              |  |  |  |

| D003                             | VPOR | VDD start voltage to ensure Power-on Reset   | _                                                                                                                                                                                                                                                                                                                          | Vss        | _    | V          | See section on Power-on Reset for details                                                                                                                                                                                                                              |  |  |  |

| D004                             | SVDD | VDD rise rate to ensure Power-on Reset       | 0.05*                                                                                                                                                                                                                                                                                                                      | _          | _    | V/ms       | See section on Power-on Reset for details                                                                                                                                                                                                                              |  |  |  |

| D004                             | SVDD | VDD rise rate to ensure<br>Power-on Reset    | 0.05*                                                                                                                                                                                                                                                                                                                      | _          | _    | V/ms       | See section on Power-on Reset for details                                                                                                                                                                                                                              |  |  |  |

| D005                             | VBOR | Brown-out Detect Voltage                     | 3.7                                                                                                                                                                                                                                                                                                                        | 4.0        | 4.35 | V          | BOREN configuration bit is cleared                                                                                                                                                                                                                                     |  |  |  |