Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | <u>.</u>                                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                |                                                                             |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | <u>.</u>                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc622-04e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0     | General Description                 | . 5 |

|---------|-------------------------------------|-----|

| 2.0     | PIC16C62X Device Varieties          | . 7 |

|         | Architectural Overview              |     |

|         | Memory Organization                 |     |

| 5.0     | I/O Ports                           | 25  |

| 6.0     | Timer0 Module                       | 31  |

| 7.0     | Comparator Module                   | 37  |

| 8.0     | Voltage Reference Module            | 43  |

| 9.0     | Special Features of the CPU         | 45  |

| 10.0    | Instruction Set Summary             | 61  |

|         | Development Support                 |     |

| 12.0    | Electrical Specifications           | 81  |

| 13.0    | Device Characterization Information | 09  |

| 14.0    | Packaging Information 1             | 13  |

|         | Jix A: Enhancements 1               |     |

| Append  | Jix B: Compatibility                | 19  |

| Index   |                                     | 21  |

| On-Line | e Support 1                         | 23  |

| System  | Is Information and Upgrade Hot Line | 23  |

|         | Response 1                          |     |

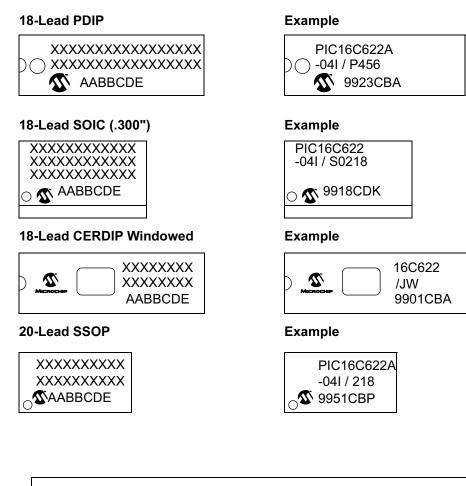

| Product | t Identification System 1           | 25  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

# 4.0 MEMORY ORGANIZATION

# 4.1 Program Memory Organization

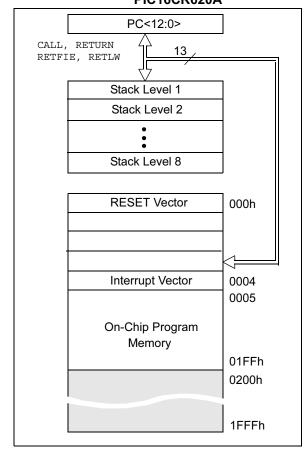

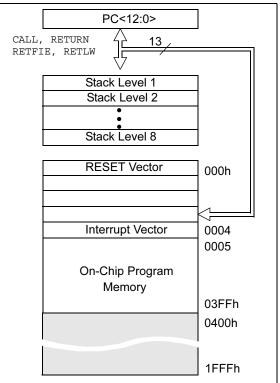

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

# FIGURE 4-2:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

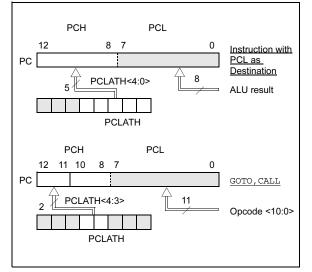

# 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any RESET, the PC is cleared. Figure 4-8 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

### FIGURE 4-8: LOADING OF PC IN DIFFERENT SITUATIONS

# 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

# 4.3.2 STACK

The PIC16C62X family has an 8-level deep x 13-bit wide hardware stack (Figure 4-2 and Figure 4-3). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

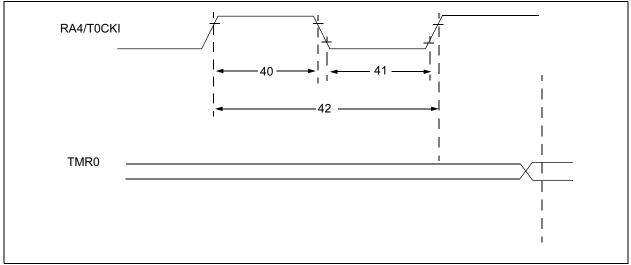

# 6.2 Using Timer0 with External Clock

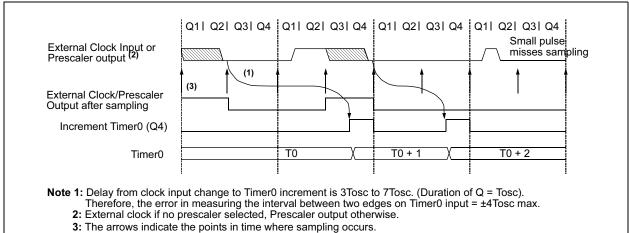

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

# 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

# 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

# REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                   |                                 | <b>(</b> | ,   |       |       |       |       |

|---------|-------------------|---------------------------------|----------|-----|-------|-------|-------|-------|

|         | R-0               | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT             | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |

|         | bit 7             |                                 |          |     |       |       |       | bit 0 |

|         |                   |                                 |          |     |       |       |       |       |

| bit 7   | <b>C2OUT</b> : Co | omparator 2                     | output   |     |       |       |       |       |

|         | 1 = C2 VIN        | + > C2 VIN-                     |          |     |       |       |       |       |

|         | 0 = C2 VIN        | + < C2 VIN-                     |          |     |       |       |       |       |

| bit 6   | <b>C1OUT</b> : Co | omparator 1                     | output   |     |       |       |       |       |

|         | 1 = C1 VIN        | + > C1 VIN-                     |          |     |       |       |       |       |

|         | 0 = C1 VIN        | + < C1 VIN-                     |          |     |       |       |       |       |

| bit 5-4 | Unimplem          | ented: Read                     | d as '0' |     |       |       |       |       |

| bit 3   | CIS: Comp         | arator Input                    | Switch   |     |       |       |       |       |

|         | When CM<          | <2:0>: = 001                    | :        |     |       |       |       |       |

|         | 1 = C1 VIN-       | - connects to                   | o RA3    |     |       |       |       |       |

|         | 0 = C1 VIN        | - connects to                   | o RA0    |     |       |       |       |       |

|         | When CM<          | <2:0> = 010:                    |          |     |       |       |       |       |

|         |                   | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |

|         |                   | I- connects t                   |          |     |       |       |       |       |

|         |                   | - connects to                   |          |     |       |       |       |       |

|         | C2 VIN            | I- connects t                   | 0 RA1    |     |       |       |       |       |

| bit 2-0 | CM<2:0>:          | Comparator                      | mode.    |     |       |       |       |       |

|         |                   |                                 |          |     |       |       |       |       |

|         | Legend:           |                                 |          |     |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.0 **VOLTAGE REFERENCE** MODULE

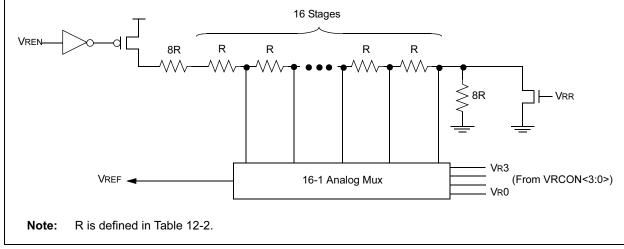

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 8-1. The block diagram is given in Figure 8-1.

#### 8.1 **Configuring the Voltage Reference**

The Voltage Reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 12-1). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

|                                                                             | R/W-0                                            | R/W-0         | R/W-0                      | U-0                     | R/W-0       | R/W-0      | R/W-0        | R/W-0  |  |  |

|-----------------------------------------------------------------------------|--------------------------------------------------|---------------|----------------------------|-------------------------|-------------|------------|--------------|--------|--|--|

|                                                                             | VREN                                             | VROE          | Vrr                        | —                       | VR3         | VR2        | VR1          | VR0    |  |  |

|                                                                             | bit 7                                            |               |                            |                         |             |            |              | bit 0  |  |  |

|                                                                             |                                                  |               |                            |                         |             |            |              |        |  |  |

| bit 7                                                                       | Vren: Vref Enable<br>1 = Vref circuit powered on |               |                            |                         |             |            |              |        |  |  |

|                                                                             |                                                  | -             | ed down, no                | IDD drain               |             |            |              |        |  |  |

| bit 6                                                                       |                                                  | F Output En   |                            |                         |             |            |              |        |  |  |

|                                                                             |                                                  | s output on F | RA2 pin<br>ed from RA2     | 2 nin                   |             |            |              |        |  |  |

| bit 5                                                                       |                                                  | Range sele    |                            | 2 pm                    |             |            |              |        |  |  |

| bit o                                                                       | 1 = Low Ra                                       |               |                            |                         |             |            |              |        |  |  |

|                                                                             | 0 = High R                                       | ange          |                            |                         |             |            |              |        |  |  |

| bit 4                                                                       | Unimplem                                         | ented: Rea    | d as '0'                   |                         |             |            |              |        |  |  |

| bit 3-0                                                                     |                                                  |               |                            | VR [3:0] ≤ 1            | 5           |            |              |        |  |  |

|                                                                             |                                                  |               | (VR<3:0>/ 2<br>1/4 * Voo + | 4) * VDD<br>(VR<3:0>/ 3 | 2) * \/חח   |            |              |        |  |  |

|                                                                             |                                                  | - 0. VILLI -  |                            | (111-0.0-7-0            | 2) 100      |            |              |        |  |  |

|                                                                             | Legend:                                          |               |                            |                         |             |            |              |        |  |  |

|                                                                             | R = Reada                                        | ble bit       | W = W                      | /ritable bit            | U = Unim    | nplemented | bit, read as | '0'    |  |  |

|                                                                             | - n = Value                                      | at POR        | '1' = B                    | it is set               | '0' = Bit i | s cleared  | x = Bit is u | nknown |  |  |

| 8-1:                                                                        | VOLTAGE                                          | REFERE        |                            | K DIAGRA                | M           |            |              |        |  |  |

|                                                                             |                                                  |               | 16 \$                      | Stages                  |             |            |              |        |  |  |

| $\sim$                                                                      |                                                  | _             |                            |                         | _           | _          |              |        |  |  |

| $-\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 에드 8R                                            | R             | R                          | R                       | R           |            |              |        |  |  |

|                                                                             |                                                  | <u>\</u>      |                            |                         |             | • •        |              |        |  |  |

#### **REGISTER 8-1:** VRCON REGISTER(ADDRESS 9Fh)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### **FIGURE 8-**

# 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

## 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

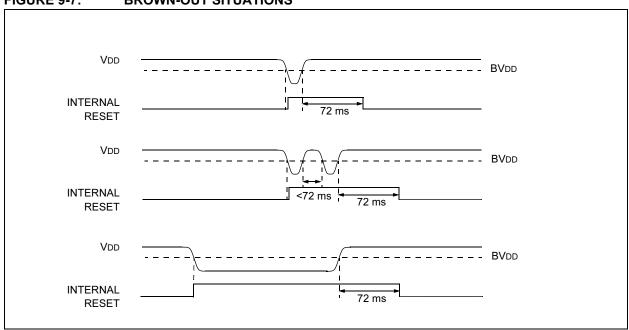

## 9.4.4 BROWN-OUT RESET (BOR)

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

## FIGURE 9-7: BROWN-OUT SITUATIONS

## TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | <u>uuuu</u> uuuu                                                                                                                                           | <u></u>                                                                                                           |

| INDF     | 00h     |                | _                                                                                                                                                          | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

## TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

| RLF              | Rotate                                       | Left f thr                                                                                                                                                                                                       | oua              | h Car                     | rv   |  |

|------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|------|--|

| Syntax:          | [ label ]                                    | RLF                                                                                                                                                                                                              | f,d              |                           |      |  |

| Operands:        | 0 ≤ f ≤ 1<br>d ∈ [0,1                        |                                                                                                                                                                                                                  |                  |                           |      |  |

| Operation:       | See des                                      | scription I                                                                                                                                                                                                      | pelov            | N                         |      |  |

| Status Affected: | С                                            |                                                                                                                                                                                                                  |                  |                           |      |  |

| Encoding:        | 00                                           | 1101                                                                                                                                                                                                             | df               | ff                        | ffff |  |

| escription:      | rotated<br>the Carr<br>is place<br>1, the re | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |                  |                           |      |  |

| Vords:           | 1                                            |                                                                                                                                                                                                                  |                  |                           |      |  |

| Cycles:          | 1                                            |                                                                                                                                                                                                                  |                  |                           |      |  |

| xample           | RLF                                          | REG1,                                                                                                                                                                                                            | 0                |                           |      |  |

|                  | Before I<br>After Ins                        | nstructio<br>REG1<br>C<br>struction<br>REG1<br>W                                                                                                                                                                 | n<br>=<br>=<br>= | 1110<br>0<br>1110<br>1100 |      |  |

|                  |                                              | С                                                                                                                                                                                                                | =                | 1                         |      |  |

| RRF              | Rotate R                                                                                                                                                                                                          | ight f th      | nroug       | gh Ca             | arry     |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|----------|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                         | RRF f          | ,d          |                   |          |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                 |                |             |                   |          |  |  |

| Operation:       | See desc                                                                                                                                                                                                          | ription b      | elow        | '                 |          |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |                |             |                   |          |  |  |

| Encoding:        | 00                                                                                                                                                                                                                | 1100           | df          | ff                | ffff     |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                |             |                   |          |  |  |

|                  |                                                                                                                                                                                                                   |                | Regis       | ter f             | <b>}</b> |  |  |

| Words:           | 1                                                                                                                                                                                                                 |                |             |                   |          |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |                |             |                   |          |  |  |

| Example          | RRF                                                                                                                                                                                                               |                | REG<br>0    | 61,               |          |  |  |

|                  | Before In                                                                                                                                                                                                         | structior      | ı           |                   |          |  |  |

|                  |                                                                                                                                                                                                                   | REG1<br>C      | =<br>=      | 1110<br>0         | 0110     |  |  |

|                  | After Inst                                                                                                                                                                                                        |                |             |                   |          |  |  |

|                  | 1                                                                                                                                                                                                                 | REG1<br>W<br>C | =<br>=<br>= | 1110<br>0111<br>0 |          |  |  |

SLEEP

| <b>VIII</b>      |                                                                                                                                                                                                                                                       |       |      |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|--|

| Syntax:          | [ label<br>]                                                                                                                                                                                                                                          | SLEEF | D    |      |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                  |       |      |      |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                            |       |      |      |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                |       |      |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                    | 0000  | 0110 | 0011 |  |  |  |

| Description:     | The power-down STATUS bit,<br>PD is cleared. Time-out<br>STATUS bit, TO is set. Watch-<br>dog Timer and its prescaler are<br>cleared.<br>The processor is put into SLEEP<br>mode with the oscillator<br>stopped. See Section 9.8 for<br>more details. |       |      |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                     |       |      |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                     |       |      |      |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                 |       |      |      |  |  |  |

NOTES:

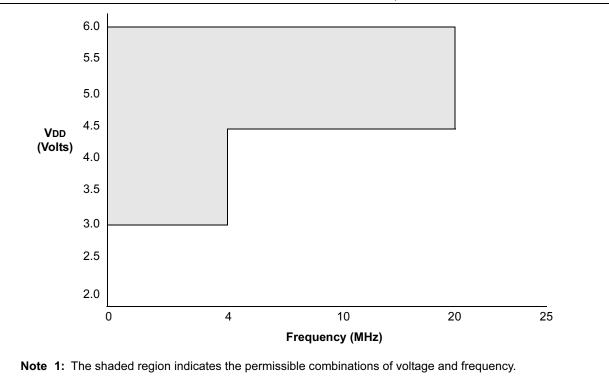

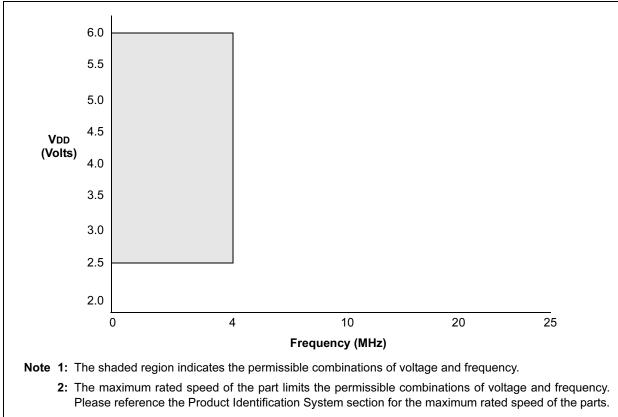

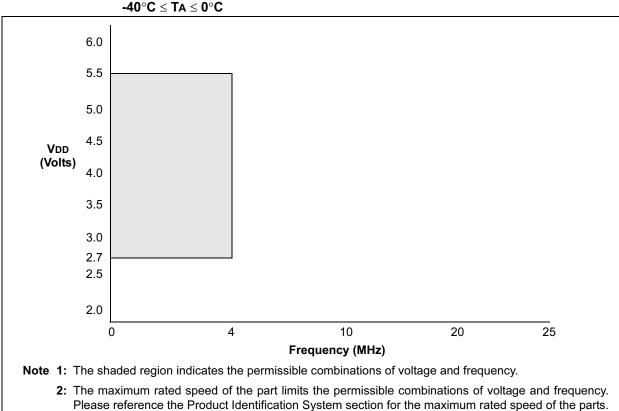

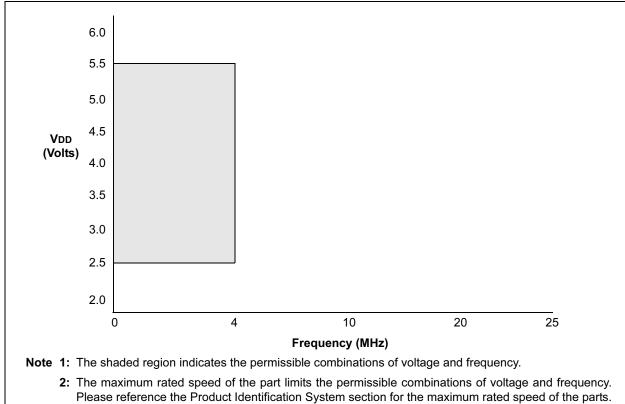

**2**: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

# 12.2 DC Characteristics: PIC16C62XA-04 (Commercial, Industrial, Extended) PIC16C62XA-20 (Commercial, Industrial, Extended) PIC16LC62XA-04 (Commercial, Industrial, Extended) (CONT.)

| PIC16C62XA<br>PIC16LC62XA |     |                                   |     | $\begin{array}{ c c c c c c } \hline \textbf{Standard Operating Conditions (unless otherwise stated)} \\ \hline \textbf{Operating temperature} & -40^{\circ}\text{C} & \leq \text{TA} \leq +85^{\circ}\text{C} \text{ for industrial and} \\ & 0^{\circ}\text{C} & \leq \text{TA} \leq +70^{\circ}\text{C} \text{ for commercial and} \\ & -40^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{Standard Operating Conditions (unless otherwise stated)} \\ \hline \textbf{Operating temperature} & -40^{\circ}\text{C} & \leq \text{TA} \leq +85^{\circ}\text{C} \text{ for industrial and} \\ & 0^{\circ}\text{C} & \leq \text{TA} \leq +70^{\circ}\text{C} \text{ for commercial and} \\ & 0^{\circ}\text{C} & \leq \text{TA} \leq +70^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA}0^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq \text{TA}0^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq 10^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq 10^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq 10^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq 10^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq 10^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq 10^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^{\circ}\text{C} & \leq 10^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{A}0^$ |                         |                      |                                                                                                                                                                       |  |

|---------------------------|-----|-----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.             | Sym | Characteristic                    | Min | Тур†                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Мах                     | Units                | Conditions                                                                                                                                                            |  |

| D010                      | IDD | Supply Current <sup>(2, 4)</sup>  | _   | 1.2<br>0.4<br>1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.0<br>1.2<br>2.0       | mA<br>mA<br>mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 10 MHz, VDD = 3.0V, WDT dis- |  |

|                           |     |                                   | _   | 4.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.0<br>7.0              | mA<br>mA             | abled, HS mode, (Note 6)<br>Fosc = 20 MHz, VDD = 4.5V, WDT dis-<br>abled, HS mode<br>Fosc = 20 MHz, VDD = 5.5V, WDT dis-                                              |  |

|                           |     |                                   | _   | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70                      | μA                   | abled*, HS mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT dis-<br>abled, LP mode                                                                                              |  |

| D010                      | IDD | Supply Current <sup>(2)</sup>     | _   | 1.2<br>—<br>35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.0<br>1.1<br>70        | mA<br>mA<br>μA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT mode, (Note 4)*<br>Fosc = 4 MHz, VDD = 2.5V, WDT disabled,<br>XT mode, (Note 4)<br>Fosc = 32 kHz, VDD = 2.5V, WDT dis-  |  |

| D020                      | IPD | Power-down Current <sup>(3)</sup> |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.2<br>5.0<br>9.0<br>15 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0V           VDD = 4.5V*           VDD = 5.5V           VDD = 5.5V Extended Temp.                                                                             |  |