Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc622-04e-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Device Differences**

| Device                     | Device Voltage Range Oscillator |            | Process Technology<br>(Microns) |

|----------------------------|---------------------------------|------------|---------------------------------|

| PIC16C620 <sup>(3)</sup>   | 2.5 - 6.0                       | See Note 1 | 0.9                             |

| PIC16C621 <sup>(3)</sup>   | 2.5 - 6.0                       | See Note 1 | 0.9                             |

| PIC16C622 <sup>(3)</sup>   | 2.5 - 6.0                       | See Note 1 | 0.9                             |

| PIC16C620A <sup>(4)</sup>  | 2.7 - 5.5                       | See Note 1 | 0.7                             |

| PIC16CR620A <sup>(2)</sup> | 2.5 - 5.5                       | See Note 1 | 0.7                             |

| PIC16C621A <sup>(4)</sup>  | 2.7 - 5.5                       | See Note 1 | 0.7                             |

| PIC16C622A <sup>(4)</sup>  | 2.7 - 5.5                       | See Note 1 | 0.7                             |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.5V - 3.0V will require the PIC16LCR62X parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X parts.

4: For OTP parts, operations from 2.7V - 3.0V will require the PIC16LC62XA parts.

NOTES:

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin # | I/O/P Type             | Buffer<br>Type        | Description                                                                                                                                                                                                         |

|--------------|-------------------|---------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18            | I                      | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                               |

| OSC2/CLKOUT  | 15                | 17            | 0                      | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin out-<br>puts CLKOUT, which has 1/4 the frequency of OSC1<br>and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4             | I/P                    | ST                    | Master Clear (Reset) input/programming voltage input.<br>This pin is an Active Low Reset to the device.                                                                                                             |

|              |                   |               |                        |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |

| RA0/AN0      | 17                | 19            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA1/AN1      | 18                | 20            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA2/AN2/VREF | 1                 | 1             | I/O                    | ST                    | Analog comparator input or VREF output                                                                                                                                                                              |

| RA3/AN3      | 2                 | 2             | I/O                    | ST                    | Analog comparator input /output                                                                                                                                                                                     |

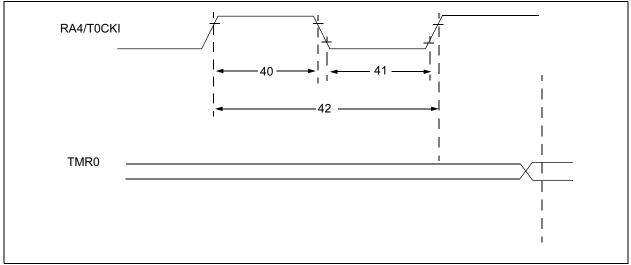

| RA4/T0CKI    | 3                 | 3             | I/O                    | ST                    | Can be selected to be the clock input to the Timer<br>timer/counter or a comparator output. Output is<br>open drain type.                                                                                           |

|              |                   |               |                        |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                                 |

| RB0/INT      | 6                 | 7             | I/O                    | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an externa interrupt pin.                                                                                                                                                           |

| RB1          | 7                 | 8             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB2          | 8                 | 9             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB3          | 9                 | 10            | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB4          | 10                | 11            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB5          | 11                | 12            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB6          | 12                | 13            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock                                                                                                                                                                   |

| RB7          | 13                | 14            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                   |

| Vss          | 5                 | 5,6           | Р                      |                       | Ground reference for logic and I/O pins.                                                                                                                                                                            |

| Vdd          | 14                | 15,16         | Р                      | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                             |

| Legend:      | O = out<br>— = No | •             | I/O = inp<br>I = Input | ut/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                             |

TTL = TTL input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

#### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                   |                                 | <b>(</b> | ,   |       |       |       |       |

|---------|-------------------|---------------------------------|----------|-----|-------|-------|-------|-------|

|         | R-0               | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT             | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |

|         | bit 7             |                                 |          |     |       |       |       | bit 0 |

|         |                   |                                 |          |     |       |       |       |       |

| bit 7   | <b>C2OUT</b> : Co | omparator 2                     | output   |     |       |       |       |       |

|         | 1 = C2 VIN        | + > C2 VIN-                     |          |     |       |       |       |       |

|         | 0 = C2 VIN        | + < C2 VIN-                     |          |     |       |       |       |       |

| bit 6   | <b>C1OUT</b> : Co | omparator 1                     | output   |     |       |       |       |       |

|         | 1 = C1 VIN        | + > C1 VIN-                     |          |     |       |       |       |       |

|         | 0 = C1 VIN        | + < C1 VIN-                     |          |     |       |       |       |       |

| bit 5-4 | Unimplem          | ented: Read                     | d as '0' |     |       |       |       |       |

| bit 3   | CIS: Comp         | arator Input                    | Switch   |     |       |       |       |       |

|         | When CM<          | <2:0>: = 001                    | :        |     |       |       |       |       |

|         | 1 = C1 VIN-       | - connects to                   | o RA3    |     |       |       |       |       |

|         | 0 = C1 VIN        | - connects to                   | o RA0    |     |       |       |       |       |

|         | When CM<          | <2:0> = 010:                    |          |     |       |       |       |       |

|         |                   | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |

|         |                   | I- connects t                   |          |     |       |       |       |       |

|         |                   | - connects to                   |          |     |       |       |       |       |

|         | C2 VIN            | I- connects t                   | 0 RA1    |     |       |       |       |       |

| bit 2-0 | CM<2:0>:          | Comparator                      | mode.    |     |       |       |       |       |

|         |                   |                                 |          |     |       |       |       |       |

|         | Legend:           |                                 |          |     |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16C62X devices can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

### 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 9-1). The PIC16C62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 9-2).

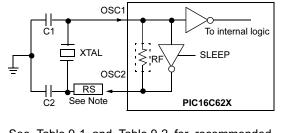

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

See Table 9-1 and Table 9-2 for recommended values of C1 and C2.

**Note:** A series resistor may be required for AT strip cut crystals.

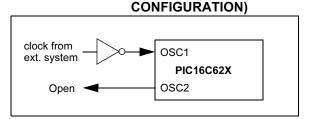

#### FIGURE 9-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

### TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| R                                                                                                                                                                                                                                                                                                                  | anges Charao                  | 21                                      |                                         |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| Mode                                                                                                                                                                                                                                                                                                               | Freq                          | <b>0562(C2)</b>                         |                                         |  |  |  |

| ХТ                                                                                                                                                                                                                                                                                                                 | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 82 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |

| HS                                                                                                                                                                                                                                                                                                                 | 8.0 MHz<br>16.0 MHz 🔨         | 10-68 pF<br>10-22 pF                    | 10 - 68 pF<br>10 - 22 pF                |  |  |  |

| Higher capacitance increases the stability of the oscil-<br>lator but also increases the start-up time. These<br>walkes are for design guidance only. Since each<br>resonator has its own characteristics, the user<br>should consult the resonator manufacturer for<br>appropriate values of external components. |                               |                                         |                                         |  |  |  |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                                                                                                                                                                                                                                                                                                                                                                                                                      | Freq     | OSC1(C1)    | OSC2(C2)                |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------------------------|--|--|

| LP                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32 kHz   | 68 - 100 pF | 68 - 100 pF             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | 200 kHz  | 15 - 30 pF  | 15 - 30 pF              |  |  |

| хт                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 kHz  | 68 - 150 pF | 150-300 pF              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2 MHz    | 15 - 30 pF  | 15-30 pF                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4 MHz    | 15 - 30 pF  | 15-30 pF                |  |  |

| HS                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8 MHz    | 15-30 pF    | <sup>V</sup> 15 - 30 pF |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 MHz   | 15-30 pF    | 15 - 30 pF              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 MHz 🔨 | 15-30 pF    | 15 - 30 pF              |  |  |

| Higher capacitance, increases the stability of the<br>oscillator but also increases the start-up time.<br>These values are for design guidance only. Rs may<br>be required in HS mode as well as XT mode to<br>avoid overdriving crystals with low drive level<br>specification. Since each crystal has its own<br>characteristics, the user should consult the crystal<br>manufacturer for appropriate values of external<br>components. |          |             |                         |  |  |

#### 9.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOR)

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 9.4.4 BROWN-OUT RESET (BOR)

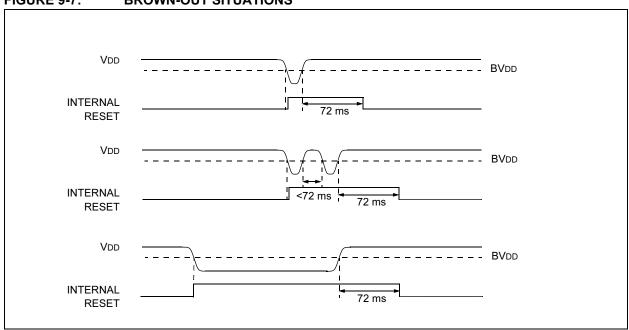

The PIC16C62X members have on-chip Brown-out Reset circuitry. A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V refer to VBOR parameter D005 (VBOR) for greater than parameter (TBOR) in Table 12-5. The brown-out situation will RESET the chip. A RESET won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

#### FIGURE 9-7: BROWN-OUT SITUATIONS

#### **FIGURE 9-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR** SLOW VDD POWER-UP) Vdd Vdd D R R1 MCLR PIC16C62X С Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down. **2:** < 40 k $\Omega$ is recommended to make sure that voltage drop across R does not violate the device's electrical specification. **3:** R1 = $100\Omega$ to 1 k $\Omega$ will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin

breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

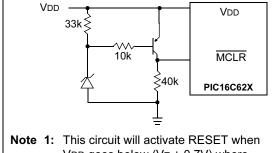

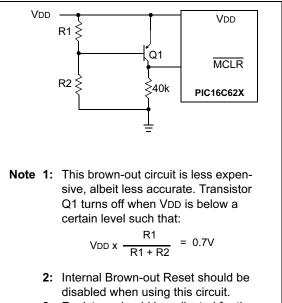

#### FIGURE 9-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate RESET when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- **2:** Internal Brown-out Reset circuitry should be disabled when using this circuit.

#### FIGURE 9-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

**3:** Resistors should be adjusted for the characteristics of the transistor.

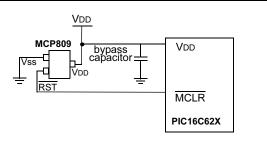

#### FIGURE 9-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

| RLF              | Rotate                          | Left f thr                                       | oua                    | h Car                                | rv                             |

|------------------|---------------------------------|--------------------------------------------------|------------------------|--------------------------------------|--------------------------------|

| Syntax:          | [ label ]                       | RLF                                              | f,d                    |                                      |                                |

| Operands:        | 0 ≤ f ≤ 1<br>d ∈ [0,1           |                                                  |                        |                                      |                                |

| Operation:       | See des                         | scription I                                      | pelov                  | N                                    |                                |

| Status Affected: | С                               |                                                  |                        |                                      |                                |

| Encoding:        | 00                              | 1101                                             | df                     | ff                                   | ffff                           |

| escription:      | rotated<br>the Carr<br>is place |                                                  | the<br>'d' is<br>V reg | left th<br>0, the<br>jister.<br>back | rough<br>e result<br>If 'd' is |

| Vords:           | 1                               |                                                  |                        |                                      |                                |

| Cycles:          | 1                               |                                                  |                        |                                      |                                |

| xample           | RLF                             | REG1,                                            | 0                      |                                      |                                |

|                  | Before I<br>After Ins           | nstructio<br>REG1<br>C<br>struction<br>REG1<br>W | n<br>=<br>=<br>=       | 1110<br>0<br>1110<br>1100            |                                |

|                  |                                 | С                                                | =                      | 1                                    |                                |

| RRF              | Rotate R                                                                                                                                                                                                          | ight f th                | nroug       | gh Ca             | arry     |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|-------------------|----------|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                         | [ <i>label</i> ] RRF f,d |             |                   |          |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                 |                          |             |                   |          |  |  |

| Operation:       | See desc                                                                                                                                                                                                          | ription b                | elow        | '                 |          |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |                          |             |                   |          |  |  |

| Encoding:        | 00                                                                                                                                                                                                                | 1100                     | df          | ff                | ffff     |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                          |             |                   |          |  |  |

|                  |                                                                                                                                                                                                                   | ; _▶                     | Regis       | ter f             | <b>}</b> |  |  |

| Words:           | 1                                                                                                                                                                                                                 |                          |             |                   |          |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |                          |             |                   |          |  |  |

| Example          | RRF                                                                                                                                                                                                               |                          | REG<br>0    | 61,               |          |  |  |

|                  | Before In                                                                                                                                                                                                         | structior                | ı           |                   |          |  |  |

|                  |                                                                                                                                                                                                                   | REG1<br>C                | =<br>=      | 1110<br>0         | 0110     |  |  |

|                  | After Inst                                                                                                                                                                                                        |                          |             |                   |          |  |  |

|                  | 1                                                                                                                                                                                                                 | REG1<br>W<br>C           | =<br>=<br>= | 1110<br>0111<br>0 |          |  |  |

SLEEP

| <b>VIII</b>      |                                                                                                                                                                                                                                                       |       |      |      |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|

| Syntax:          | [ label<br>]                                                                                                                                                                                                                                          | SLEEF | D    |      |  |  |

| Operands:        | None                                                                                                                                                                                                                                                  |       |      |      |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{W}DT \text{ prescaler,} \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                               |       |      |      |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                |       |      |      |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                    | 0000  | 0110 | 0011 |  |  |

| Description:     | The power-down STATUS bit,<br>PD is cleared. Time-out<br>STATUS bit, TO is set. Watch-<br>dog Timer and its prescaler are<br>cleared.<br>The processor is put into SLEEP<br>mode with the oscillator<br>stopped. See Section 9.8 for<br>more details. |       |      |      |  |  |

| Words:           | 1                                                                                                                                                                                                                                                     |       |      |      |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                     |       |      |      |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                 |       |      |      |  |  |

| SWAPF            | Swap Ni                                                                                                                                                                    | bbles in  | f          |              |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|--------------|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                 |           |            |              |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                         |           |            |              |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                                                                                                                                   |           | <i>,</i> . |              |  |  |

| Status Affected: | None                                                                                                                                                                       |           |            |              |  |  |

| Encoding:        | 00                                                                                                                                                                         | 1110      | dfff       | ffff         |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |           |            |              |  |  |

| Words:           | 1                                                                                                                                                                          |           |            |              |  |  |

| Cycles:          | 1                                                                                                                                                                          |           |            |              |  |  |

| Example          | SWAPF                                                                                                                                                                      | REG,      | 0          |              |  |  |

|                  | Before In                                                                                                                                                                  | struction |            |              |  |  |

|                  |                                                                                                                                                                            | REG1      | = (        | DxA5         |  |  |

|                  | After Inst                                                                                                                                                                 | ruction   |            |              |  |  |

|                  |                                                                                                                                                                            | REG1<br>W |            | 0xA5<br>0x5A |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                  |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |  |

| XORLW                                                                                                    | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Operands:                                                                                                | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operation:                                                                                               | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Description:                                                                                             | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                                                                              |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                                 | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                          | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                          | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XORWF                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                          | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Syntax:                                                                                                  | [label] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Syntax:                                                                                                  | [ <i>label</i> ] XORWF f,d $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Syntax:<br>Operands:                                                                                     | $ \begin{array}{ll} \textit{[label]} & XORWF & f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \end{array} $                                                                                                                                                                                                                                                                                                                                                                                    |

| Syntax:<br>Operands:<br>Operation:                                                                       | $ \begin{array}{ll} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) & \text{XOR.} & (\textit{f}) \rightarrow (\textit{dest}) \end{array} $                                                                                                                                                                                                                                                                                           |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                                                                             |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{c c} \textit{[label]} & \text{XORWF} & \textit{f,d} \\ 0 \leq \textit{f} \leq 127 \\ d \in [0,1] \\ (W) . \text{XOR.} (\textit{f}) \rightarrow (\text{dest}) \\ \hline Z \\ \hline \hline 00 & 0110 & \text{dfff} & \text{ffff} \\ \hline \text{Exclusive OR the contents of the} \\ W \text{ register with register 'f'. If 'd' is} \\ 0, \text{ the result is stored in the W} \\ \hline \text{register. If 'd' is 1, the result is} \end{array}$                      |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00 \qquad 0110 \qquad dfff \qquad ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'.                                                                                                                              |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $[label] XORWF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .XOR. (f) $\rightarrow$ (dest) Z $\boxed{00  0110  dfff  ffff}$ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1                                                                                                                                                                                   |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | [ <i>label</i> ] XORWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z<br>00 0110 dfff ffff<br>Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is<br>0, the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'.<br>1<br>1                                                                                                                                                   |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF REG 1 \\ \end{bmatrix}$                                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ REG & = 0xAF \\ \end{bmatrix}$                            |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ XORWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ \hline REG &= 0xAF \\ W &= 0xB5 \\ \end{bmatrix}$ |

NOTES:

#### 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

#### 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

#### 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

#### 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

#### 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

#### 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

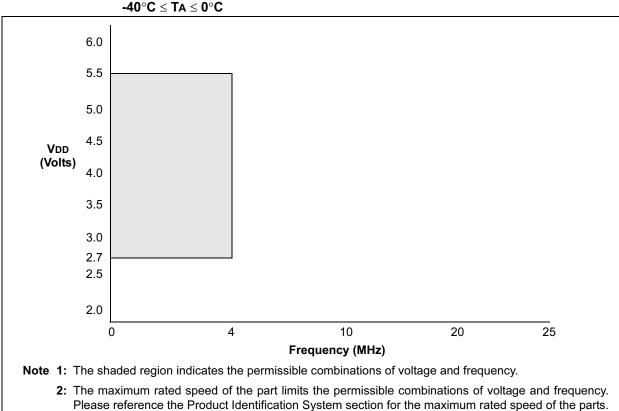

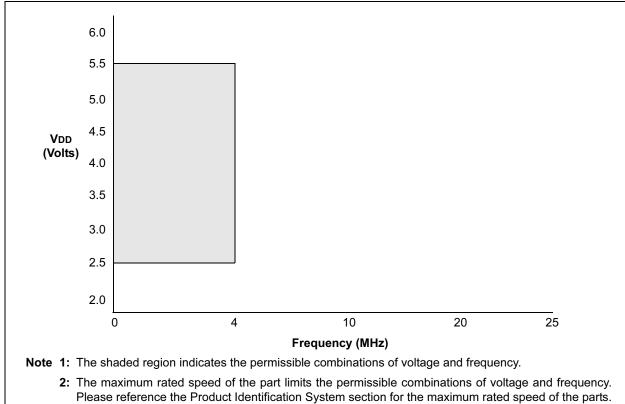

#### 12.1 DC Characteristics: PIC16C62X-04 (Commercial, Industrial, Extended) PIC16C62X-20 (Commercial, Industrial, Extended) PIC16LC62X-04 (Commercial, Industrial, Extended)

| PIC16C62X       Standard Operating Conditions (unless otherwis<br>Operating temperature -40°C ≤ TA ≤ +85°C for ind<br>0°C ≤ TA ≤ +70°C for con<br>-40°C ≤ TA ≤ +125°C for ex         Standard Operating Conditions (unless otherwise)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dustrial and mmercial and                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |