Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

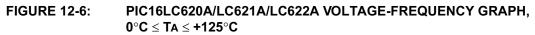

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc622-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **EPROM-Based 8-Bit CMOS Microcontrollers**

#### Devices included in this data sheet:

Referred to collectively as PIC16C62X.

- PIC16C620 PIC16C620A

- PIC16C621 PIC16C621A

- PIC16C622 PIC16C622A

- PIC16CR620A

#### **High Performance RISC CPU:**

- Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- Operating speed:

- DC 40 MHz clock input

- DC 100 ns instruction cycle

| Device      | Program<br>Memory | Data<br>Memory |

|-------------|-------------------|----------------|

| PIC16C620   | 512               | 80             |

| PIC16C620A  | 512               | 96             |

| PIC16CR620A | 512               | 96             |

| PIC16C621   | 1K                | 80             |

| PIC16C621A  | 1K                | 96             |

| PIC16C622   | 2K                | 128            |

| PIC16C622A  | 2K                | 128            |

· Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

#### **Peripheral Features:**

- 13 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs can be output signals

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

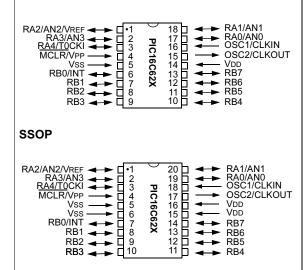

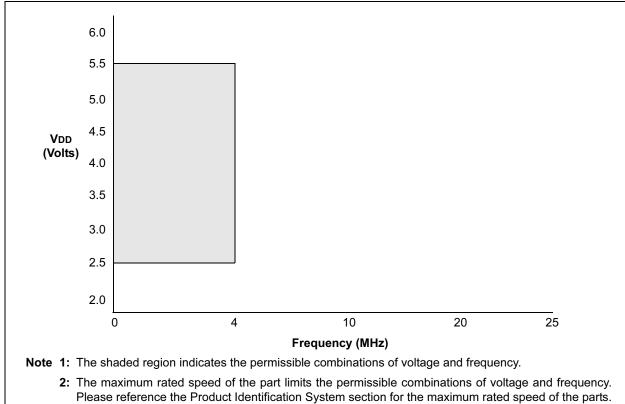

#### Pin Diagrams

#### PDIP, SOIC, Windowed CERDIP

#### **Special Microcontroller Features:**

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

- · Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

#### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- Fully static design

- · Wide operating range

- 2.5V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

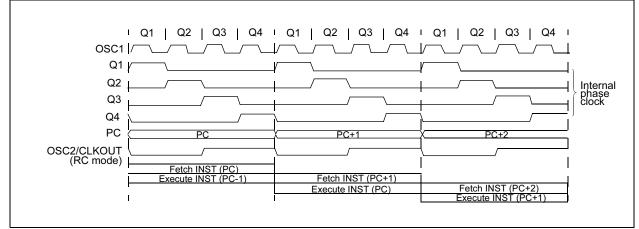

## 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

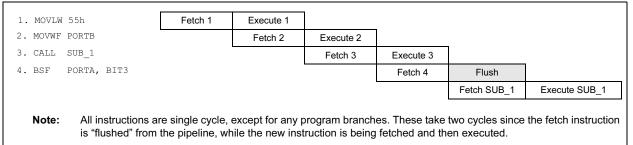

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

#### 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

### 5.0 I/O PORTS

The PIC16C62X have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

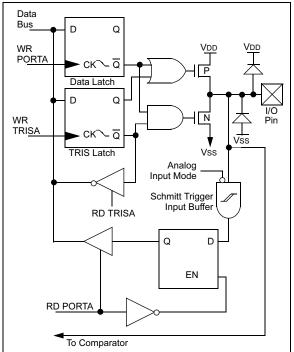

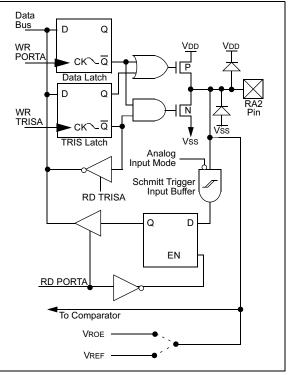

#### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the T0CKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (comparator control register) register and the VRCON (voltage reference control register) register. When selected as a comparator input, these pins will read as '0's.

#### FIGURE 5-1: BLOCK DIAGRAM OF RA1:RA0 PINS

| Note: | On RESET, the TRISA register is set to all  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | inputs. The digital inputs are disabled and |  |  |  |  |  |

|       | the comparator inputs are forced to ground  |  |  |  |  |  |

|       | to reduce excess current consumption.       |  |  |  |  |  |

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output and must be buffered prior to any external load. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the Comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### EXAMPLE 5-1: INITIALIZING PORTA

| CLRF  | PORTA                          | ;Initialize PORTA by setting<br>;output data latches |  |

|-------|--------------------------------|------------------------------------------------------|--|

| MOVLW | 0X07 ;Turn comparators off and |                                                      |  |

| MOVWF | CMCON                          | ;enable pins for I/O<br>;functions                   |  |

| BSF   | STATUS, RPO                    | ;Select Bank1                                        |  |

| MOVLW | 0x1F                           | ;Value used to initialize                            |  |

|       |                                | ;data direction                                      |  |

| MOVWF | TRISA                          | ;Set RA<4:0> as inputs                               |  |

|       |                                | ;TRISA<7:5> are always                               |  |

|       |                                | ;read as '0'.                                        |  |

#### FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

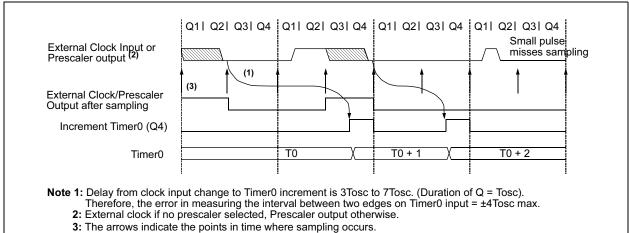

#### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

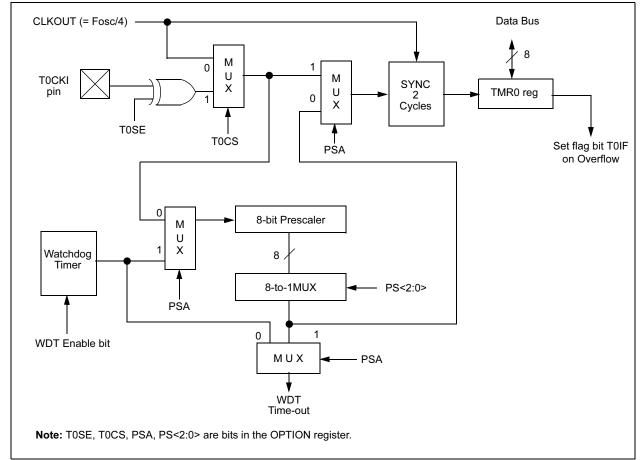

#### 6.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

#### FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

The code example in Example 7-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 7-1: INITIALIZING COMPARATOR MODULE

| MOVLW | 0x03         | ;Init comparator mode             |

|-------|--------------|-----------------------------------|

| MOVWF | CMCON        | ;CM<2:0> = 011                    |

| CLRF  | PORTA        | ;Init PORTA                       |

| BSF   | STATUS, RPO  | ;Select Bank1                     |

| MOVLW | 0x07         | ;Initialize data direction        |

| MOVWF | TRISA        | ;Set RA<2:0> as inputs            |

|       |              | ;RA<4:3> as outputs               |

|       |              | ;TRISA<7:5> always read `0'       |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| CALL  | DELAY 10     | ;10µs delay                       |

| MOVF  | CMCON,F      | ;Read CMCONtoend change condition |

| BCF   | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF   | STATUS, RPO  | ;Select Bank 1                    |

| BSF   | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF   | STATUS, RPO  | ;Select Bank 0                    |

| BSF   | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF   | INTCON, GIE  | ;Global interrupt enable          |

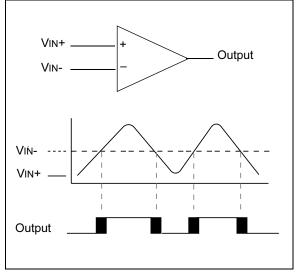

### 7.2 Comparator Operation

A single comparator is shown in Figure 7-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 7-2 represent the uncertainty due to input offsets and response time.

#### 7.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 7-2).

#### 7.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

#### 7.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 7-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 9.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### REGISTER 9-1: CONFIGURATION WORD (ADDRESS 2007h)

| CP1                                                                                                                                                                                                                                                                                                                                                                                            | CP0 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CP1                                 | CP0 <sup>(2)</sup> | CP1     | CP0 <sup>(2)</sup>    |        | BODEN                     | CP1     | CP0 <sup>(2)</sup> | PWRTE       | WDTE      | F0SC1     | F0SC0 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|---------|-----------------------|--------|---------------------------|---------|--------------------|-------------|-----------|-----------|-------|

| bit 13                                                                                                                                                                                                                                                                                                                                                                                         | ļ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u> </u>                            | ļļ                 |         | ļ                     |        | <u> </u>                  | <u></u> | <u>I</u>           | <u></u>     | <u> </u>  | ļ         | bit 0 |

| bit 13-8<br>5-4:                                                                                                                                                                                                                                                                                                                                                                               | bit 13-8, <b>CP&lt;1:0&gt;:</b> Code protection bit pairs <sup>(2)</sup><br>5-4: Code protection for 2K program memory<br>11 = Program memory code protection off<br>10 = 0400h-07FFh code protected<br>01 = 0200h-07FFh code protected<br>00 = 0000h-07FFh code protected<br>Code protection for 1K program memory<br>11 = Program memory code protection off<br>10 = Program memory code protected<br>01 = 0200h-03FFh code protected<br>02 = 0000h-03FFh code protected<br>Code protection for 0.5K program memory<br>11 = Program memory code protected<br>Code protection for 0.5K program memory<br>11 = Program memory code protection off<br>10 = Program memory code protection off |                                     |                    |         |                       |        |                           |         |                    |             |           |           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                   | m memo<br>-01FFh c |         |                       | on off |                           |         |                    |             |           |           |       |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     | nted: Re           | -       |                       |        |                           |         |                    |             |           |           |       |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                          | BOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DEN: Br                             | own-out l          | Reset E | nable bit             | (1)    |                           |         |                    |             |           |           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BOR en<br>BOR dis                   |                    |         |                       |        |                           |         |                    |             |           |           |       |

| bit 3                                                                                                                                                                                                                                                                                                                                                                                          | 1 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>RTE</b> : Po<br>PWRT o<br>PWRT e |                    | īmer Er | able bit <sup>(</sup> | 1, 3)  |                           |         |                    |             |           |           |       |

| bit 2                                                                                                                                                                                                                                                                                                                                                                                          | <b>WDTE</b> : Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                    |         |                       |        |                           |         |                    |             |           |           |       |

| <ul> <li>bit 1-0 FOSC1:FOSC0: Oscillator Selection bits</li> <li>11 = RC oscillator</li> <li>10 = HS oscillator</li> <li>01 = XT oscillator</li> <li>00 = LP oscillator</li> <li>Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Detect Reset is enabled.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |                    |         |                       |        |                           |         |                    |             |           |           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2: Al<br>lis                        | l of the C<br>ted. |         | -                     |        | e given the<br>Power-up T |         |                    | nable the c | code prot | tection s | cheme |

| Legend<br>R = Re                                                                                                                                                                                                                                                                                                                                                                               | l:<br>adable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | it                                  |                    | W =     | Writable              | bit    | U =                       | Unimple | emented            | bit, read a | s '0'     |           |       |

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16C62X devices can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

### 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

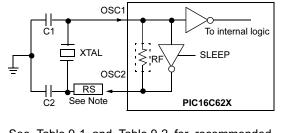

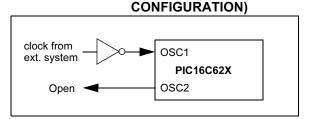

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 9-1). The PIC16C62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

See Table 9-1 and Table 9-2 for recommended values of C1 and C2.

**Note:** A series resistor may be required for AT strip cut crystals.

#### FIGURE 9-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

## TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| R                                                                                                                                                                                                                                                                                                                  | anges Charao                  | 21                                      |                                         |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|--|--|

| Mode                                                                                                                                                                                                                                                                                                               | Freq                          | <b>0562(C2)</b>                         |                                         |  |  |

| ХТ                                                                                                                                                                                                                                                                                                                 | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 82 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |

| HS                                                                                                                                                                                                                                                                                                                 | 8.0 MHz<br>16.0 MHz 🔨         | 10-68 pF<br>10-22 pF                    | 10 - 68 pF<br>10 - 22 pF                |  |  |

| Higher capacitance increases the stability of the oscil-<br>lator but also increases the start-up time. These<br>walkes are for design guidance only. Since each<br>resonator has its own characteristics, the user<br>should consult the resonator manufacturer for<br>appropriate values of external components. |                               |                                         |                                         |  |  |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                                                                                                                                                                                                                                                                                                                                                                                                                       | Freq     | OSC1(C1)    | OSC2(C2)                |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------------------------|--|--|

| LP                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32 kHz   | 68 - 100 pF | 68 - 100 pF             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | 200 kHz  | 15 - 30 pF  | 15 - 30 pF              |  |  |

| хт                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100 kHz  | 68 - 150 pF | 150-300 pF              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2 MHz    | 15 - 30 pF  | 15-30 pF                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4 MHz    | 15 - 30 pF  | 15-30 pF                |  |  |

| HS                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8 MHz    | 15-30 pF    | <sup>V</sup> 15 - 30 pF |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 MHz   | 15-30 pF    | 15 - 30 pF              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20 MHz 🔨 | 15-30 pF    | 15 - 30 pF              |  |  |

| Higher capacitance, hereases the stability of the<br>oscillator built also increases the start-up time.<br>These values are for design guidance only. Rs may<br>be required in HS mode as well as XT mode to<br>avoid overdriving crystals with low drive level<br>specification. Since each crystal has its own<br>characteristics, the user should consult the crystal<br>manufacturer for appropriate values of external<br>components. |          |             |                         |  |  |

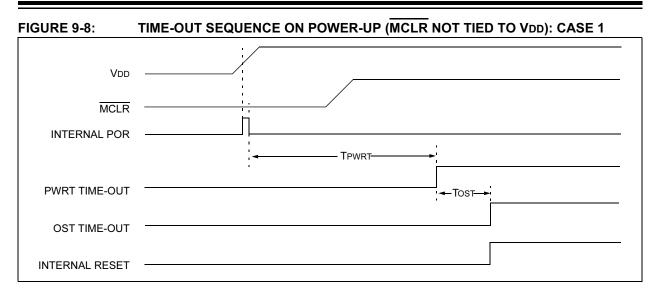

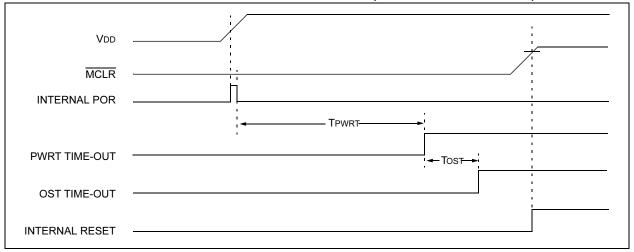

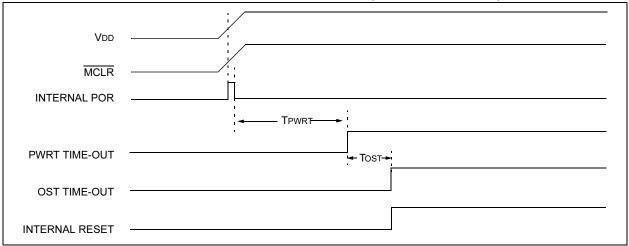

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two-cycle<br>instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                  | $\begin{array}{rcl} PC &=& address \ {\tt HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \ {\tt CONTINUE} \\ \mbox{if CNT} \neq& 0, \\ PC &=& address \ {\tt HERE} + 1 \\ \end{array}$                                                                                                 |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Encoding:        | 10 1kkk kkkk kkkk                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction.                                                                                                                                      |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Example          | GOTO THERE                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                  | After Instruction<br>PC = Address THERE                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                              |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                      |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                      |  |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                            |  |  |  |  |  |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                                  |  |  |  |  |  |

| INCFSZ                       | Increment f, Skip if 0                                                                                                                                                | IORWF            | Inclusive OR W with f                                                                                                                                                 |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                      | [ <i>label</i> ] INCFSZ f,d                                                                                                                                           | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |  |  |

| Operands:                    | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                    | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                    |  |  |

| Operation:                   | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                      | Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                     |  |  |

| Status Affected:             | None                                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                     |  |  |

| Encoding:                    | 00 1111 dfff ffff                                                                                                                                                     | Encoding:        | 00 0100 dfff ffff                                                                                                                                                     |  |  |

| Description:                 | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |

|                              | If the result is 0, the next instruc-<br>tion, which is already fetched, is                                                                                           | Words:           | 1                                                                                                                                                                     |  |  |

|                              | discarded. A NOP is executed                                                                                                                                          | Cycles:          | 1                                                                                                                                                                     |  |  |

|                              | instead making it a two-cycle                                                                                                                                         | Example          | IORWF RESULT, 0                                                                                                                                                       |  |  |

| Words:<br>Cycles:<br>Example | instruction. 1 1(2) HERE INCFSZ CNT, 1 GOTO LOOP CONTINUE • •                                                                                                         |                  | Before InstructionRESULT = $0x13$ W = $0x91$ After InstructionRESULT =RESULT = $0x13$ W = $0x93$ Z =1                                                                 |  |  |

|                              | •<br>Before Instruction                                                                                                                                               | MOVLW            | Move Literal to W                                                                                                                                                     |  |  |

|                              | PC = address HERE<br>After Instruction                                                                                                                                | Syntax:          | [ <i>label</i> ] MOVLW k                                                                                                                                              |  |  |

|                              | CNT = CNT + 1                                                                                                                                                         | Operands:        | $0 \le k \le 255$                                                                                                                                                     |  |  |

|                              | if CNT= 0,<br>PC = address CONTINUE                                                                                                                                   | Operation:       | $k \rightarrow (W)$                                                                                                                                                   |  |  |

|                              | if CNT≠ 0,                                                                                                                                                            | Status Affected: | None                                                                                                                                                                  |  |  |

|                              | PC = address HERE +1                                                                                                                                                  | Encoding:        | 11 00xx kkkk kkkk                                                                                                                                                     |  |  |

| IORLW                        | Inclusive OR Literal with W                                                                                                                                           | Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's.                                                                      |  |  |

| Syntax:                      | [ <i>label</i> ] IORLW k                                                                                                                                              | Words:           | 1                                                                                                                                                                     |  |  |

| Operands:                    | $0 \le k \le 255$                                                                                                                                                     | Cycles:          | 1                                                                                                                                                                     |  |  |

| Operation:                   | (W) .OR. $k \rightarrow$ (W)                                                                                                                                          | Example          | MOVLW 0x5A                                                                                                                                                            |  |  |

| Status Affected:             | Z                                                                                                                                                                     | Example          | After Instruction                                                                                                                                                     |  |  |

| Encoding:                    | 11 1000 kkkk kkkk                                                                                                                                                     |                  | W = 0x5A                                                                                                                                                              |  |  |

| Description:                 | The contents of the W register is<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register.                                              |                  |                                                                                                                                                                       |  |  |

| Words:                       | 1                                                                                                                                                                     |                  |                                                                                                                                                                       |  |  |

| Cycles:                      | 1                                                                                                                                                                     |                  |                                                                                                                                                                       |  |  |

| Example                      | IORLW 0x35                                                                                                                                                            |                  |                                                                                                                                                                       |  |  |

|                              | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBE                                                                                                       |                  |                                                                                                                                                                       |  |  |

W = Z =

0xBF 1

| SWAPF            | Swap Ni                                                                                                                                                                    | bbles in  | f     |              |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|--------------|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                 |           |       |              |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |           |       |              |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                                                                                                                                   |           | · · · |              |  |  |

| Status Affected: | None                                                                                                                                                                       |           |       |              |  |  |

| Encoding:        | 00                                                                                                                                                                         | 1110      | dfff  | ffff         |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |           |       |              |  |  |

| Words:           | 1                                                                                                                                                                          |           |       |              |  |  |

| Cycles:          | 1                                                                                                                                                                          |           |       |              |  |  |

| Example          | SWAPF                                                                                                                                                                      | REG,      | 0     |              |  |  |

|                  | Before Instruction                                                                                                                                                         |           |       |              |  |  |

|                  |                                                                                                                                                                            | REG1      | = (   | DxA5         |  |  |

|                  | After Inst                                                                                                                                                                 | ruction   |       |              |  |  |

|                  |                                                                                                                                                                            | REG1<br>W |       | 0xA5<br>0x5A |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                    |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |  |

| XORLW                                                                                         | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                       | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operands:                                                                                     | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operation:                                                                                    | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                   |

| Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Encoding:                                                                                     | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                               |

| Description:                                                                                  | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                      |

| Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                               |