Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc622a-04-p |

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

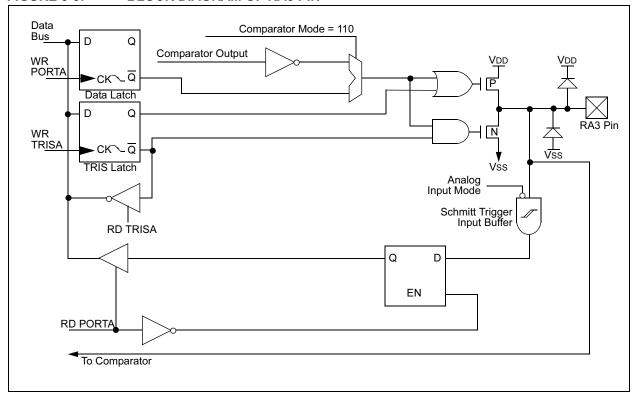

FIGURE 5-3: BLOCK DIAGRAM OF RA3 PIN

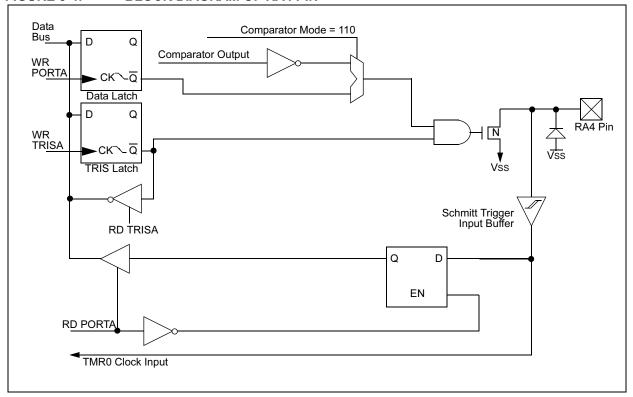

## FIGURE 5-4: BLOCK DIAGRAM OF RA4 PIN

TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer<br>Type | Function                                                                                       |

|--------------|------|----------------|------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | ST             | Input/output or comparator input                                                               |

| RA1/AN1      | bit1 | ST             | Input/output or comparator input                                                               |

| RA2/AN2/VREF | bit2 | ST             | Input/output or comparator input or VREF output                                                |

| RA3/AN3      | bit3 | ST             | Input/output or comparator input/output                                                        |

| RA4/T0CKI    | bit4 | ST             | Input/output or external clock input for TMR0 or comparator output. Output is open drain type. |

Legend: ST = Schmitt Trigger input

TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|--------------|---------------------------------|

| 05h     | PORTA | _     | _     | -     | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000       | u 0000                          |

| 85h     | TRISA |       |       | 1     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111       | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000      | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000    | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

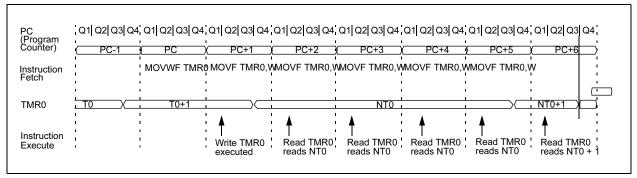

#### FIGURE 6-3: TIMERO TIMING: INTERNAL CLOCK/PRESCALE 1:2

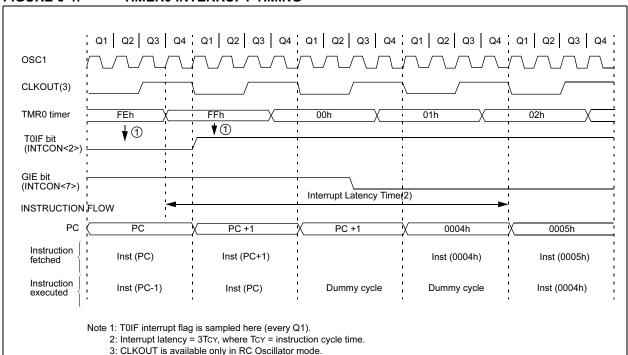

### FIGURE 6-4: TIMERO INTERRUPT TIMING

# 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.)

# EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          | •            | ,                                                           |

|----------|--------------|-------------------------------------------------------------|

| 1.BCF    | STATUS, RPO  | ;Skip if already in ;Bank 0                                 |

| 2.CLRWDT |              | ;Clear WDT                                                  |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler                                     |

| 4.BSF    | STATUS, RPO  | ;Bank 1                                                     |

| 5.MOVLW  | '00101111'b; | ;These 3 lines (5, 6, 7)                                    |

| 6.MOVWF  | OPTION       | <pre>;are required only if ;desired PS&lt;2:0&gt; are</pre> |

| 7.CLRWDT |              | ;000 or 001                                                 |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to                                          |

| 9.MOVWF  | OPTION       | ;desired WDT rate                                           |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0                                           |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

# EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT       |                           | ;Clear WDT and ;prescaler                                 |

|--------------|---------------------------|-----------------------------------------------------------|

| BSF          | STATUS, RPO               | ,prescarer                                                |

| MOVLW        | b'xxxx0xxx'               | ;Select TMR0, new<br>;prescale value and<br>;clock source |

| MOVWF<br>BCF | OPTION_REG<br>STATUS, RPO | ·                                                         |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMERO

| Address | Name   | Bit 7    | Bit 6                  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|------------------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 ı | Timer0 module register |       |        |        |        |        |        |                 | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | PEIE                   | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | RBPU     | INTEDG                 | T0CS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        | _                      | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by TMR0 module.

#### 9.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in RC mode with PWRTE bit erased (PWRT disabled), there will be no time-out at all. Figure 9-8, Figure 9-9 and Figure 9-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (see Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC16C62X device operating in parallel.

Table 9-4 shows the RESET conditions for some special registers, while Table 9-5 shows the RESET conditions for all the registers.

### 9.4.6 POWER CONTROL (PCON)/ STATUS REGISTER

The power control/STATUS register, PCON (address 8Eh), has two bits.

Bit0 is  $\overline{BOR}$  (Brown-out).  $\overline{BOR}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{BOR}$  = 0, indicating that a brown-out has occurred. The  $\overline{BOR}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is  $\overline{\mathsf{POR}}$  (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET, if  $\overline{\mathsf{POR}}$  is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

TABLE 9-1: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up    |

|--------------------------|-------------------|-----------|-------------------|------------|

| Oscillator Configuration | PWRTE = 0         | PWRTE = 1 | Brown-out Neset   | from SLEEP |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |

| RC                       | 72 ms             | _         | 72 ms             | _          |

TABLE 9-2: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                    |  |  |  |

|-----|-----|----|----|------------------------------------|--|--|--|

| 0   | Х   | 1  | 1  | Power-on Reset                     |  |  |  |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |  |  |  |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |  |  |  |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |  |  |  |

| 1   | 1   | 0  | u  | WDT Reset                          |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP            |  |  |  |

Legend: u = unchanged, x = unknown

TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 83h     | STATUS |       |       |       | TO    | PD    |       |       |       | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     |       | _     | _     |       | _     | POR   | BOR   | 0x                    | uq                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

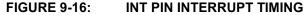

#### 9.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wake-up from SLEEP through RB0/INT interrupt.

#### 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

#### 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-4 Tcy. Synchronous latency = 3 Tcy, where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a two-cycle instruction.

- 3: CLKOUT is available only in RC Oscillator mode.

- 4: For minimum width of INT pulse, refer to AC specs.

- 5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

### 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or himpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or Vss with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |

|-------|-------------------------------------------|

|       | by a WDT time-out does not drive MCLR     |

|       | pin low.                                  |

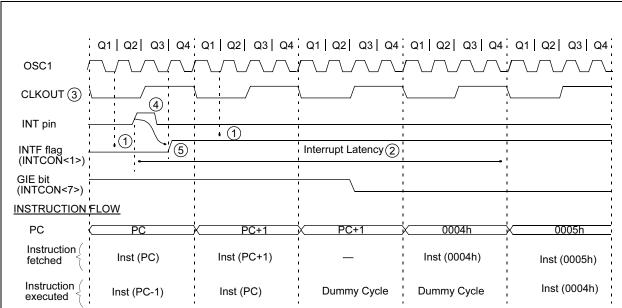

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device RESET.  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked.  $\overline{\text{TO}}$  bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

## FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

- Note 1: XT, HS or LP Oscillator mode assumed.

- 2: Tost = 1024Tosc (drawing not to scale) This delay will not be there for RC Osc mode.

- 3: GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

#### 9.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** Microchip does not recommend code protecting windowed devices.

#### 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. Only the Least Significant 4 bits of the ID locations are used.

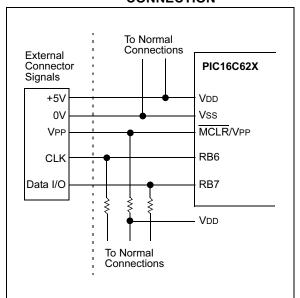

### 9.11 In-Circuit Serial Programming™

The PIC16C62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specification (DS30228).

A typical In-Circuit Serial Programming connection is shown in Figure 9-19.

FIGURE 9-19: TYPICAL IN-CIRCUIT

SERIAL PROGRAMMING

CONNECTION

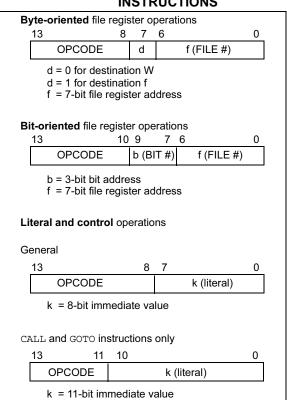

#### 10.0 INSTRUCTION SET SUMMARY

Each PIC16C62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C62X instruction set summary in Table 10-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 10-1: OPCODE FIELD DESCRIPTIONS

|               | DEGOTAL FIGHT                                                                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field         | Description                                                                                                                                                        |

| f             | Register file address (0x00 to 0x7F)                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                              |

| х             | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                       |

| label         | Label name                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                    |

| PCLAT         | Program Counter High Latch                                                                                                                                         |

| Н             |                                                                                                                                                                    |

| GIE           | Global Interrupt Enable bit                                                                                                                                        |

| WDT           | Watchdog Timer/Counter                                                                                                                                             |

| TO            | Time-out bit                                                                                                                                                       |

| PD            | Power-down bit                                                                                                                                                     |

| dest          | Destination either the W register or the specified register file location                                                                                          |

| []            | Options                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                        |

| <>            | Register bit field                                                                                                                                                 |

| €             | In the set of                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                |

|               |                                                                                                                                                                    |

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 10-1 lists the instructions recognized by the MPASM $^{\text{TM}}$  assembler.

Figure 10-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PICmicro<sup>®</sup> products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

| RETFIE           | Return from Interrupt                                                                                                                                                                              |                        |          |      |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|------|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                          | RETFIE                 |          |      |  |  |  |  |

| Operands:        | None                                                                                                                                                                                               |                        |          |      |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$ , $1 \rightarrow GIE$                                                                                                                                                         |                        |          |      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                               |                        |          |      |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                 | 0000                   | 0000     | 1001 |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed and Top of Stack (TOS) is loaded in the PC. Interrupts are enabled by setting Global Interrupt Enable bit, GIE (INTCON<7>). This is a two-cycle instruction. |                        |          |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                  |                        |          |      |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                  |                        |          |      |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                             |                        |          |      |  |  |  |  |

|                  |                                                                                                                                                                                                    | rrupt<br>PC =<br>GIE = | TOS<br>1 |      |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETLW k                                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                     |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                    |  |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                       |  |  |  |  |

| Description:     | The W register is loaded with the eight bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                       |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                       |  |  |  |  |

| Example          | CALL TABLE; W contains table :offset value                                                                                                                              |  |  |  |  |

| TABLE            | • ;W now has table value                                                                                                                                                |  |  |  |  |

|                  | ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ; •                                                                                                                 |  |  |  |  |

|                  | RETLW kn ; End of table                                                                                                                                                 |  |  |  |  |

|                  | Before Instruction  W = 0x07  After Instruction                                                                                                                         |  |  |  |  |

|                  | W = value of k8                                                                                                                                                         |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                         |   |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|

| Syntax:          | [label] RETURN                                                                                                                                 |   |  |  |

| Operands:        | None                                                                                                                                           |   |  |  |

| Operation:       | $TOS \to PC$                                                                                                                                   |   |  |  |

| Status Affected: | None                                                                                                                                           |   |  |  |

| Encoding:        | 00 0000 0000 1000                                                                                                                              | ) |  |  |

| Description:     | Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a two-cycle instruction. |   |  |  |

| Words:           | 1                                                                                                                                              |   |  |  |

| Cycles:          | 2                                                                                                                                              |   |  |  |

| Example          | RETURN                                                                                                                                         |   |  |  |

|                  | After Interrupt PC = TOS                                                                                                                       |   |  |  |

# **PIC16C62X**

NOTES:

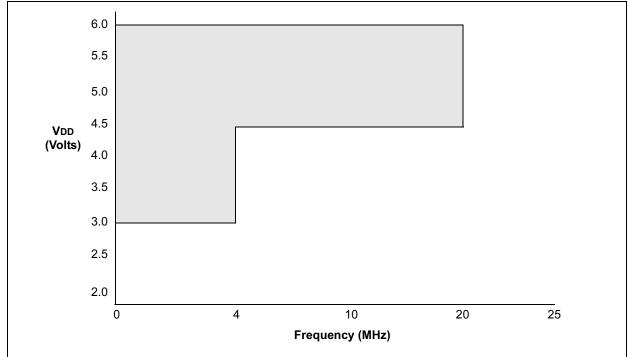

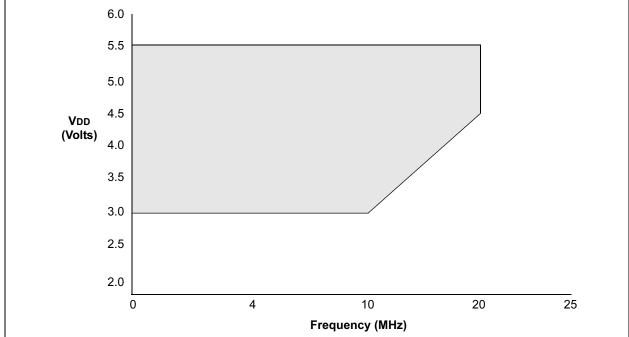

FIGURE 12-1: PIC16C62X VOLTAGE-FREQUENCY GRAPH, -40°C ≤ TA ≤ +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

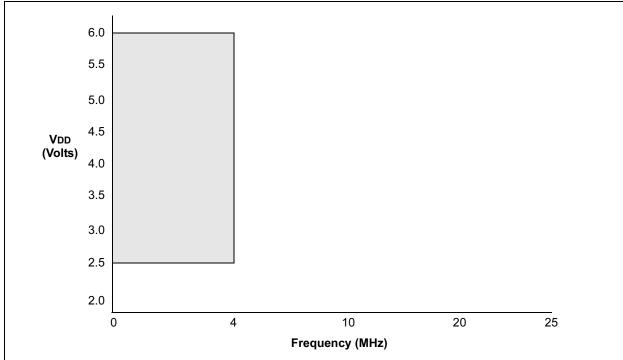

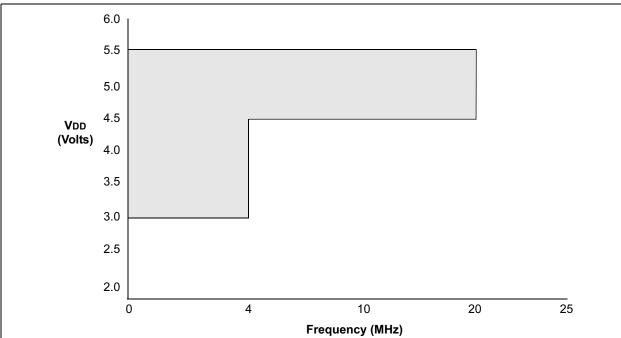

FIGURE 12-2: PIC16LC62X VOLTAGE-FREQUENCY GRAPH, -40°C ≤ TA ≤ +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

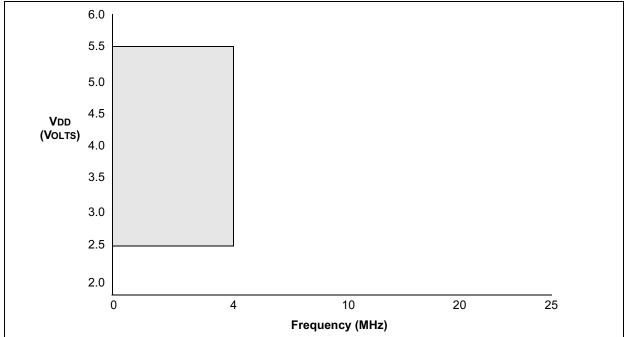

FIGURE 12-3: PIC16C62XA VOLTAGE-FREQUENCY GRAPH, 0°C ≤ TA ≤ +70°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

FIGURE 12-4: PIC16C62XA VOLTAGE-FREQUENCY GRAPH, -40°C  $\leq$  TA  $\leq$  0°C, +70°C  $\leq$  TA  $\leq$  +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

FIGURE 12-9: PIC16LCR62XA VOLTAGE-FREQUENCY GRAPH, -40°C ≤ TA ≤ +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

# 12.4 DC Characteristics: PIC16C62X/C62XA/CR62XA (Commercial, Industrial, Extended) PIC16LC62X/LC62XA/LCR62XA (Commercial, Industrial, Extended) (CONT.)

| PIC16C62X/C62XA/CR62XA    |           |                                            | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial and $0^{\circ}\text{C} \le \text{TA} \le +70^{\circ}\text{C}$ for commercial and $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended        |                               |             |    |                                                                                                |  |

|---------------------------|-----------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------|----|------------------------------------------------------------------------------------------------|--|

| PIC16LC62X/LC62XA/LCR62XA |           |                                            | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial and $0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C}$ for commercial and $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ for extended |                               |             |    |                                                                                                |  |

| Param.<br>No.             | Sym       | Characteristic                             | Min                                                                                                                                                                                                                                                                                                                        | Min Typ† Max Units Conditions |             |    |                                                                                                |  |

|                           | Vol       | Output Low Voltage                         |                                                                                                                                                                                                                                                                                                                            |                               |             |    |                                                                                                |  |

| D080                      |           | I/O ports                                  | _                                                                                                                                                                                                                                                                                                                          | _                             | 0.6         | V  | IOL = 8.5 mA, VDD = 4.5V, -40° to +85°C                                                        |  |

|                           |           |                                            | _                                                                                                                                                                                                                                                                                                                          | _                             | 0.6         | V  | IOL = 7.0 mA, VDD = 4.5V, +125°C                                                               |  |

| D083                      |           | OSC2/CLKOUT (RC only)                      | _                                                                                                                                                                                                                                                                                                                          | _                             | 0.6         | V  | IOL = 1.6 mA, VDD = 4.5V, -40° to +85°C                                                        |  |

|                           |           |                                            | _                                                                                                                                                                                                                                                                                                                          | _                             | 0.6         | V  | IOL = 1.2 mA, VDD = 4.5V, +125°C                                                               |  |

|                           | Vон       | Output High Voltage <sup>(3)</sup>         |                                                                                                                                                                                                                                                                                                                            |                               |             |    |                                                                                                |  |

| D090                      |           | I/O ports (Except RA4)                     | VDD-0.7                                                                                                                                                                                                                                                                                                                    | _                             | _           | V  | IOH = -3.0 mA, VDD = 4.5V, -40° to +85°C                                                       |  |

|                           |           |                                            | VDD-0.7                                                                                                                                                                                                                                                                                                                    | _                             | _           | V  | IOH = -2.5 mA, VDD = 4.5V, +125°C                                                              |  |

| D092                      |           | OSC2/CLKOUT (RC only)                      | VDD-0.7                                                                                                                                                                                                                                                                                                                    | _                             | _           | V  | IOH = -1.3 mA, VDD = 4.5V, -40° to +85°C                                                       |  |

|                           |           | - (2)                                      | VDD-0.7                                                                                                                                                                                                                                                                                                                    | _                             | _           | V  | IOH = -1.0 mA, VDD = 4.5V, +125°C                                                              |  |

|                           | Voн       | Output High Voltage <sup>(3)</sup>         |                                                                                                                                                                                                                                                                                                                            |                               |             |    |                                                                                                |  |

| D090                      |           | I/O ports (Except RA4)                     | VDD-0.7                                                                                                                                                                                                                                                                                                                    | _                             | _           | V  | IOH = -3.0 mA, VDD = 4.5V, -40° to +85°C                                                       |  |

| D092                      |           | OSC2/CLKOUT (RC only)                      | VDD-0.7<br>VDD-0.7                                                                                                                                                                                                                                                                                                         | _                             | _           | V  | IOH = -2.5 mA, VDD = 4.5V, +125°C<br>IOH = -1.3 mA, VDD = 4.5V, -40° to +85°C                  |  |

| D092                      |           | OGCZ/CEROOT (IXC OHly)                     | VDD-0.7                                                                                                                                                                                                                                                                                                                    |                               |             | V  | IOH = -1.0 mA, VDD = 4.5V, +125°C                                                              |  |

| *D150                     | Vod       | Open-Drain High Voltage                    |                                                                                                                                                                                                                                                                                                                            |                               | 10*<br>8.5* | V  | RA4 pin PIC16C62X, PIC16LC62X<br>RA4 pin PIC16C62XA, PIC16LC62XA,<br>PIC16CR62XA, PIC16LCR62XA |  |

| *D150                     | Vod       | Open-Drain High Voltage                    |                                                                                                                                                                                                                                                                                                                            |                               | 10*<br>8.5* | V  | RA4 pin PIC16C62X, PIC16LC62X<br>RA4 pin PIC16C62XA, PIC16LC62XA,<br>PIC16CR62XA, PIC16LCR62XA |  |

|                           |           | Capacitive Loading Specs on<br>Output Pins |                                                                                                                                                                                                                                                                                                                            |                               |             |    |                                                                                                |  |

| D100                      | COSC<br>2 | OSC2 pin                                   |                                                                                                                                                                                                                                                                                                                            |                               | 15          | pF | In XT, HS and LP modes when external clock used to drive OSC1.                                 |  |

| D101                      | Cıo       | All I/O pins/OSC2 (in RC mode)             |                                                                                                                                                                                                                                                                                                                            |                               | 50          | pF |                                                                                                |  |

|                           |           | Capacitive Loading Specs on Output Pins    |                                                                                                                                                                                                                                                                                                                            |                               |             |    |                                                                                                |  |

| D100                      | COSC 2    | OSC2 pin                                   |                                                                                                                                                                                                                                                                                                                            |                               | 15          | pF | In XT, HS and LP modes when external clock used to drive OSC1.                                 |  |

| D101                      | Cio       | All I/O pins/OSC2 (in RC mode)             |                                                                                                                                                                                                                                                                                                                            |                               | 50          | pF |                                                                                                |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C62X(A) be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as coming out of the pin.

# 12.8 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Т |           |   |      |  |

|---|-----------|---|------|--|

| F | Frequency | Т | Time |  |

|   |           | - |      |  |

Lowercase subscripts (pp) and their meanings:

| рр |          |     |       |

|----|----------|-----|-------|

| ck | CLKOUT   | osc | OSC1  |

| io | I/O port | tO  | T0CKI |

| mc | MCLR     |     |       |

Uppercase letters and their meanings:

| S |                        |   |              |

|---|------------------------|---|--------------|

| F | Fall                   | Р | Period       |

| Н | High                   | R | Rise         |

| 1 | Invalid (Hi-impedance) | V | Valid        |

| L | Low                    | Z | Hi-Impedance |

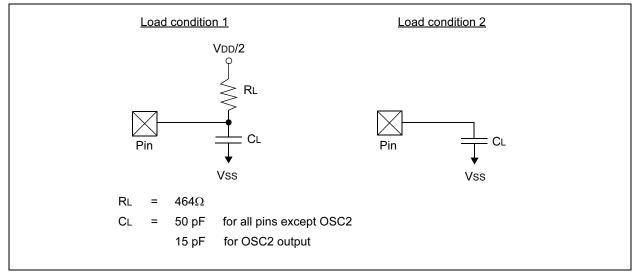

## FIGURE 12-11: LOAD CONDITIONS

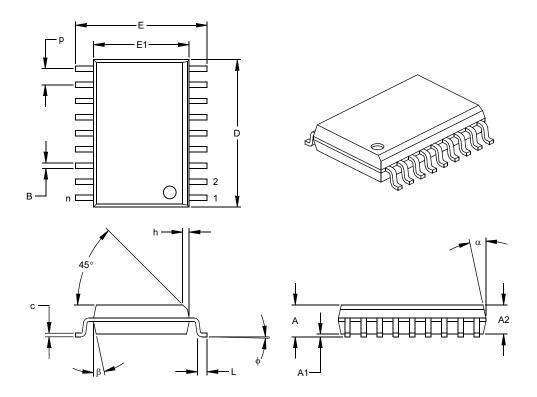

## 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

|                          | Units  |      |      | INCHES* |       |       | MILLIMETERS |  |  |

|--------------------------|--------|------|------|---------|-------|-------|-------------|--|--|

| Dimension                | Limits | MIN  | NOM  | MAX     | MIN   | NOM   | MAX         |  |  |

| Number of Pins           | n      |      | 18   |         |       | 18    |             |  |  |

| Pitch                    | р      |      | .050 |         |       | 1.27  |             |  |  |

| Overall Height           | Α      | .093 | .099 | .104    | 2.36  | 2.50  | 2.64        |  |  |

| Molded Package Thickness | A2     | .088 | .091 | .094    | 2.24  | 2.31  | 2.39        |  |  |

| Standoff §               | A1     | .004 | .008 | .012    | 0.10  | 0.20  | 0.30        |  |  |

| Overall Width            | Е      | .394 | .407 | .420    | 10.01 | 10.34 | 10.67       |  |  |

| Molded Package Width     | E1     | .291 | .295 | .299    | 7.39  | 7.49  | 7.59        |  |  |

| Overall Length           | D      | .446 | .454 | .462    | 11.33 | 11.53 | 11.73       |  |  |

| Chamfer Distance         | h      | .010 | .020 | .029    | 0.25  | 0.50  | 0.74        |  |  |

| Foot Length              | L      | .016 | .033 | .050    | 0.41  | 0.84  | 1.27        |  |  |

| Foot Angle               | ф      | 0    | 4    | 8       | 0     | 4     | 8           |  |  |

| Lead Thickness           | С      | .009 | .011 | .012    | 0.23  | 0.27  | 0.30        |  |  |

| Lead Width               | В      | .014 | .017 | .020    | 0.36  | 0.42  | 0.51        |  |  |

| Mold Draft Angle Top     | α      | 0    | 12   | 15      | 0     | 12    | 15          |  |  |

| Mold Draft Angle Bottom  | β      | 0    | 12   | 15      | 0     | 12    | 15          |  |  |

#### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

<sup>\*</sup> Controlling Parameter § Significant Characteristic

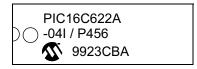

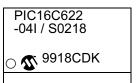

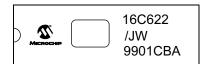

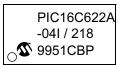

## 14.1 Package Marking Information

#### 18-Lead PDIP

#### 18-Lead SOIC (.300")

#### 18-Lead CERDIP Windowed

#### 20-Lead SSOP

### **Example**

## **Example**

#### Example

#### Example

**Legend:** XX...X Customer specific information\*

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

**lote**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information.

\* Standard PICmicro device marking consists of Microchip part number, year code, week code, and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| Io:  | Technical Publications Manager                   | Total Pages Sent                                 |

|------|--------------------------------------------------|--------------------------------------------------|

| RE:  | Reader Response                                  |                                                  |

| Fron | m: Name                                          | <u> </u>                                         |

|      | Company                                          |                                                  |

|      |                                                  |                                                  |

|      | City / State / ZIP / Country                     |                                                  |

|      | Telephone: ()                                    |                                                  |

| App  | olication (optional):                            |                                                  |

| Wou  | uld you like a reply?YN                          |                                                  |

| Dev  | rice: PIC16C62X Literature                       | Number: DS30235J                                 |

| Que  | estions:                                         |                                                  |

| 1.   | What are the best features of this documer       | nt?                                              |

|      |                                                  |                                                  |

|      |                                                  |                                                  |

| 2.   | How does this document meet your hardwa          | are and software development needs?              |

|      |                                                  |                                                  |

| 2    | Do you find the organization of this docume      | ont oncy to follow? If not, why?                 |

| Э.   | Do you find the organization of this docume      | ent easy to follow? If flot, why?                |

|      |                                                  |                                                  |

| 4.   | What additions to the document do you thin       | nk would enhance the structure and subject?      |

|      |                                                  |                                                  |

|      |                                                  |                                                  |

| 5.   | What deletions from the document could be        | e made without affecting the overall usefulness? |

|      |                                                  |                                                  |

|      |                                                  |                                                  |

| 6.   | Is there any incorrect or misleading information | ation (what and where)?                          |

|      |                                                  |                                                  |

| 7    | How would you improve this document?             |                                                  |

|      | Tion would you improve this document:            |                                                  |

|      |                                                  |                                                  |

|      |                                                  |                                                  |