Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 18-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc622a-04i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Device Differences**

| Device                     | Voltage Range | Oscillator | Process Technology<br>(Microns) |

|----------------------------|---------------|------------|---------------------------------|

| PIC16C620 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C621 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C622 <sup>(3)</sup>   | 2.5 - 6.0     | See Note 1 | 0.9                             |

| PIC16C620A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16CR620A <sup>(2)</sup> | 2.5 - 5.5     | See Note 1 | 0.7                             |

| PIC16C621A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

| PIC16C622A <sup>(4)</sup>  | 2.7 - 5.5     | See Note 1 | 0.7                             |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

2: For ROM parts, operation from 2.5V - 3.0V will require the PIC16LCR62X parts.

**3:** For OTP parts, operation from 2.5V - 3.0V will require the PIC16LC62X parts.

4: For OTP parts, operations from 2.7V - 3.0V will require the PIC16LC62XA parts.

NOTES:

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C620(A) and PIC16CR620A address 512 x 14 on-chip program memory. The PIC16C621(A) addresses 1K x 14 program memory. The PIC16C622(A) addresses 2K x 14 program memory. All program memory is internal.

The PIC16C62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C62X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

## 4.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Reset.

| Note: | BOR is unknown on Power-on Reset. It        |

|-------|---------------------------------------------|

|       | must then be set by the user and checked    |

|       | on subsequent RESETS to see if BOR is       |

|       | cleared, indicating a brown-out has         |

|       | occurred. The BOR STATUS bit is a "don't    |

|       | care" and is not necessarily predictable if |

|       | the brown-out circuit is disabled (by       |

|       | programming BODEN bit in the                |

|       | Configuration word).                        |

## REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

|   | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---|-------|-----|-----|-----|-----|-----|-------|-------|

| ſ | _     | —   | —   | —   | —   | —   | POR   | BOR   |

| - | bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset STATUS bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

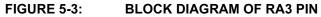

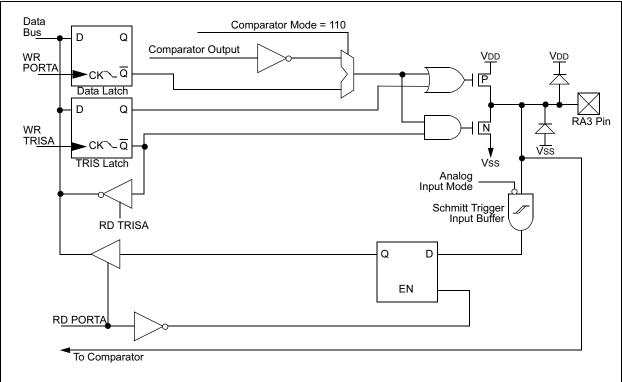

## TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

## TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

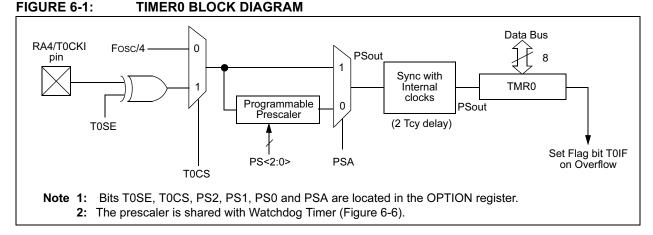

## 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

## 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

## FIGURE 6-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| (Program<br>Counter) | ( PC-1      | ) PC        | ( <u>PC+1</u> )        | PC+2                   | <u>PC+3</u> χ          | PC+4                   | PC+5 χ                     | PC+6                     |

|----------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch |             | MOVWF TMR   | 0MOVF TMR0,V           | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                | 1                        |

|                      | i.          | 1           |                        |                        | i                      |                        | i                          |                          |

| TMR0                 | то х        | T0+1 )(     | T0+2 X                 | 1                      | NT0                    |                        | NT0+1 \                    | NT0+2 )                  |

| Instruction          | 1<br>1<br>1 | 1<br>1<br>1 | <b></b>                | <b>≜</b>               | <b>≜</b>               | <b>†</b>               | <b>†</b>                   | <b>≜</b>                 |

| Executed             | 1           | 1           | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + |

## 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

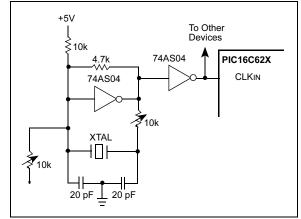

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

Figure 9-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

## FIGURE 9-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

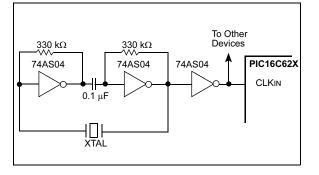

Figure 9-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 9-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

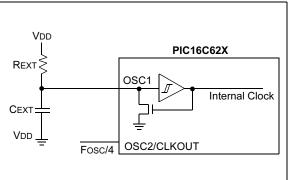

## 9.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-5 shows how the R/C combination is connected to the PIC16C62X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 13.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 13.0 for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

## FIGURE 9-5: RC OSCILLATOR MODE

## 9.5.1 RB0/INT INTERRUPT

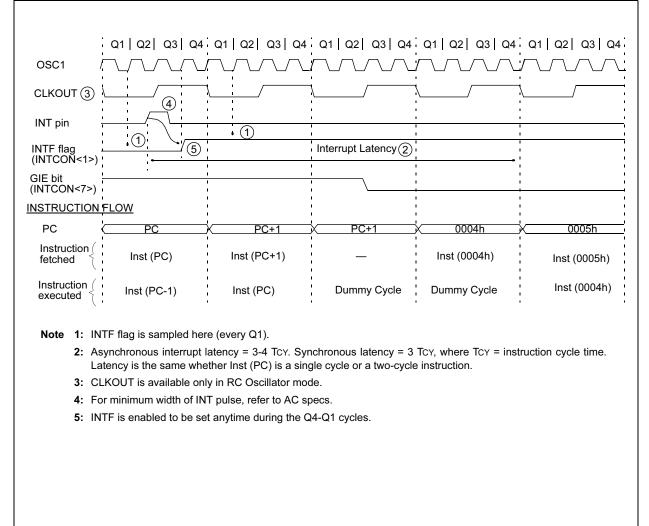

External interrupt on RB0/INT pin is edge triggered, either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP and Figure 9-18 for timing of wakeup from SLEEP through RB0/INT interrupt.

## 9.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

## 9.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the RBIF    |

|       | interrupt flag may not get set.           |

## 9.5.4 COMPARATOR INTERRUPT

See Section 7.6 for complete description of comparator interrupts.

## FIGURE 9-16: INT PIN INTERRUPT TIMING

| TABLE 10-2: PIC16C62X INSTRUCTION SET |

|---------------------------------------|

|---------------------------------------|

| Mnemonio  | ,        | Description                  | Cycles |     |      | Opcode | e    | Status   | Notes |

|-----------|----------|------------------------------|--------|-----|------|--------|------|----------|-------|

| Operands  |          |                              |        | MSb |      |        | LSb  | Affected |       |

| BYTE-OR   | IENTED I | FILE REGISTER OPERATIONS     |        |     |      |        |      |          |       |

| ADDWF     | f, d     | Add W and f                  | 1      | 00  | 0111 | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF     | f, d     | AND W with f                 | 1      | 00  | 0101 | dfff   | ffff | Z        | 1,2   |

| CLRF      | f        | Clear f                      | 1      | 00  | 0001 | lfff   | ffff | Z        | 2     |

| CLRW      | -        | Clear W                      | 1      | 00  | 0001 | 0000   | 0011 | Z        |       |

| COMF      | f, d     | Complement f                 | 1      | 00  | 1001 | dfff   | ffff | Z        | 1,2   |

| DECF      | f, d     | Decrement f                  | 1      | 00  | 0011 | dfff   | ffff | Z        | 1,2   |

| DECFSZ    | f, d     | Decrement f, Skip if 0       | 1(2)   | 00  | 1011 | dfff   | ffff |          | 1,2,3 |

| INCF      | f, d     | Increment f                  | 1      | 00  | 1010 | dfff   | ffff | Z        | 1,2   |

| INCFSZ    | f, d     | Increment f, Skip if 0       | 1(2)   | 00  | 1111 | dfff   | ffff |          | 1,2,3 |

| IORWF     | f, d     | Inclusive OR W with f        | 1      | 00  | 0100 | dfff   | ffff | Z        | 1,2   |

| MOVF      | f, d     | Move f                       | 1      | 00  | 1000 | dfff   | ffff | Z        | 1,2   |

| MOVWF     | f        | Move W to f                  | 1      | 00  | 0000 | lfff   | ffff |          |       |

| NOP       | -        | No Operation                 | 1      | 00  | 0000 | 0xx0   | 0000 |          |       |

| RLF       | f, d     | Rotate Left f through Carry  | 1      | 00  | 1101 | dfff   | ffff | С        | 1,2   |

| RRF       | f, d     | Rotate Right f through Carry | 1      | 00  | 1100 | dfff   | ffff | С        | 1,2   |

| SUBWF     | f, d     | Subtract W from f            | 1      | 00  | 0010 | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF     | f, d     | Swap nibbles in f            | 1      | 00  | 1110 | dfff   | ffff |          | 1,2   |

| XORWF     | f, d     | Exclusive OR W with f        | 1      | 00  | 0110 | dfff   | ffff | Z        | 1,2   |

| BIT-ORIEN | NTED FIL | E REGISTER OPERATIONS        |        |     |      |        |      | •        |       |

| BCF       | f, b     | Bit Clear f                  | 1      | 01  | 00bb | bfff   | ffff |          | 1,2   |

| BSF       | f, b     | Bit Set f                    | 1      | 01  | 01bb | bfff   | ffff |          | 1,2   |

| BTFSC     | f, b     | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb | bfff   | ffff |          | 3     |

| BTFSS     | f, b     | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb | bfff   | ffff |          | 3     |

| LITERAL   | AND CO   | NTROL OPERATIONS             |        |     |      |        |      |          |       |

| ADDLW     | k        | Add literal and W            | 1      | 11  | 111x | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW     | k        | AND literal with W           | 1      | 11  | 1001 | kkkk   | kkkk | Z        |       |

| CALL      | k        | Call subroutine              | 2      | 10  | 0kkk | kkkk   | kkkk |          |       |

| CLRWDT    | -        | Clear Watchdog Timer         | 1      | 00  | 0000 | 0110   | 0100 | TO,PD    |       |

| GOTO      | k        | Go to address                | 2      | 10  | 1kkk | kkkk   | kkkk |          |       |

| IORLW     | k        | Inclusive OR literal with W  | 1      | 11  | 1000 | kkkk   | kkkk | Z        |       |

| MOVLW     | k        | Move literal to W            | 1      | 11  | 00xx | kkkk   | kkkk |          |       |

| RETFIE    | -        | Return from interrupt        | 2      | 00  | 0000 | 0000   | 1001 |          |       |

| RETLW     | k        | Return with literal in W     | 2      | 11  | 01xx | kkkk   | kkkk |          |       |

| RETURN    | -        | Return from Subroutine       | 2      | 00  | 0000 | 0000   | 1000 |          |       |

| SLEEP     | -        | Go into Standby mode         | 1      | 00  | 0000 | 0110   | 0011 | TO,PD    |       |

| SUBLW     | k        | Subtract W from literal      | 1      | 11  | 110x | kkkk   | kkkk | C,DC,Z   |       |

| XORLW     | k        | Exclusive OR literal with W  | 1      | 11  | 1010 | kkkk   | kkkk | Z        |       |

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**2:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| CLRW                                                                               | Clear W                                                                                                                                                                                                                                                                                                                                                | COMF                                                                                          | Complement f                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                            | [ <i>label</i> ] CLRW                                                                                                                                                                                                                                                                                                                                  | Syntax:                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                           |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                   | Operands:                                                                                     | $0 \leq f \leq 127$                                                                                                                                                                                                                                                                                 |

| Operation:                                                                         | $00h \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                  |                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                           |

|                                                                                    | $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                      | Operation:                                                                                    | $(\bar{f}) \rightarrow (dest)$                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                   | Z                                                                                                                                                                                                                                                                                                                                                      | Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                          | 00 0001 0000 0011                                                                                                                                                                                                                                                                                                                                      | Encoding:                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                   |

| Description:                                                                       | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                            | Description:                                                                                  | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the                                                                                                                                                                                       |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | result is stored back in register 'f'.                                                                                                                                                                                                                                                              |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                      | Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                   |

| Example                                                                            | CLRW                                                                                                                                                                                                                                                                                                                                                   | Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                   |

|                                                                                    | Before Instruction<br>W = 0x5A                                                                                                                                                                                                                                                                                                                         | Example                                                                                       | COMF REG1,0                                                                                                                                                                                                                                                                                         |

|                                                                                    | W = 0x5A<br>After Instruction                                                                                                                                                                                                                                                                                                                          |                                                                                               | Before Instruction                                                                                                                                                                                                                                                                                  |

|                                                                                    | W = 0x00 $Z = 1$                                                                                                                                                                                                                                                                                                                                       |                                                                                               | REG1 = 0x13 After Instruction $REG1 = 0x13$ $W = 0xEC$                                                                                                                                                                                                                                              |

| CLRWDT                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                   |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Syntax:                                                                            | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| <b>-j</b>                                                                          |                                                                                                                                                                                                                                                                                                                                                        | DECF                                                                                          | Decrement f                                                                                                                                                                                                                                                                                         |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                   | DECF<br>Svntax:                                                                               | Decrement f                                                                                                                                                                                                                                                                                         |

| -                                                                                  | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                             | Syntax:                                                                                       | [label] DECF f,d                                                                                                                                                                                                                                                                                    |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,                                                                                                                                                                                                                                                                                        | _                                                                                             |                                                                                                                                                                                                                                                                                                     |

| Operands:                                                                          | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                             | Syntax:                                                                                       | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                            |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow TO$                                                                                                                                                                                                                                                                  | Syntax:<br>Operands:                                                                          | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                               |

| Operands:<br>Operation:                                                            | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                      | Syntax:<br>Operands:<br>Operation:                                                            | $\begin{bmatrix} label \end{bmatrix} DECF f,d$<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:                                        | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow PD$<br>$\overline{TO}, PD$                                                                                                                                                                                                          | Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | [ <i>label</i> ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow PD$<br>$\overline{TO}, PD$<br>00  0000  0110  0100<br>CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>pres <u>caler</u> of <u>the</u> WDT. STATUS                                                            | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                                    |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO$<br>$1 \rightarrow PD$<br>TO, PD<br>OUDIMIC OTIO<br>CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.                                                                                | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011 \qquad dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 & 0000 & 0110 & 0100 \\ \hline \end{array}$ CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. STATUS<br>bits TO and PD are set.<br>1 | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1     |

| MOVF                    | Move f                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:                 | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Operands:               | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Operation:              | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Status Affected:        | Z                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Encoding:               | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Description:            | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |  |  |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Example                 | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| MOVANE                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| MOVWF                   | Move W to f                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Syntax:                 | [ <i>label</i> ] MOVWF f<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Operands:<br>Operation: | $0 \le 1 \le 127$<br>(W) $\rightarrow$ (f)                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Status Affected:        | None $(1)$                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Encoding:               | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Description:            | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Example                 | MOVWF OPTION                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|                         | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F<br>W = 0x4F                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|                         | W = 0x4F                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| NOP              | No Operation |       |      |      |  |  |  |  |  |

|------------------|--------------|-------|------|------|--|--|--|--|--|

| Syntax:          | [ label ]    | NOP   |      |      |  |  |  |  |  |

| Operands:        | None         |       |      |      |  |  |  |  |  |

| Operation:       | No operation |       |      |      |  |  |  |  |  |

| Status Affected: | None         |       |      |      |  |  |  |  |  |

| Encoding:        | 00           | 0000  | 0xx0 | 0000 |  |  |  |  |  |

| Description:     | No opera     | tion. |      |      |  |  |  |  |  |

| Words:           | 1            |       |      |      |  |  |  |  |  |

| Cycles:          | 1            |       |      |      |  |  |  |  |  |

| Example          | NOP          |       |      |      |  |  |  |  |  |

| [ lahel ]                                                                                                            |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Load Option Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| [label] OPTION                                                                                                       |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| None                                                                                                                 |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| $(W) \rightarrow O$                                                                                                  | $(W) \rightarrow OPTION$                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |