Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                |                                                                              |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc622a-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

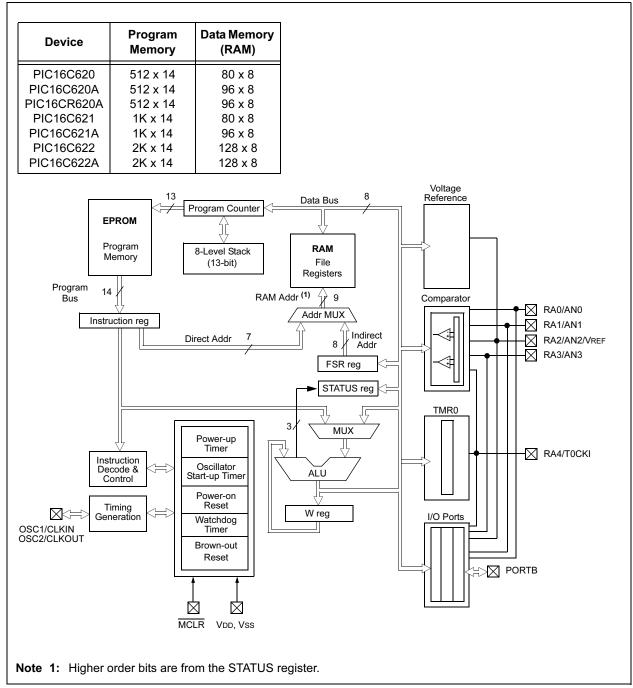

## FIGURE 3-1: BLOCK DIAGRAM

| Name         | DIP/SOIC<br>Pin # | SSOP<br>Pin # | I/O/P Type             | Buffer<br>Type        | Description                                                                                                                                                                                                         |

|--------------|-------------------|---------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                | 18            | I                      | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                               |

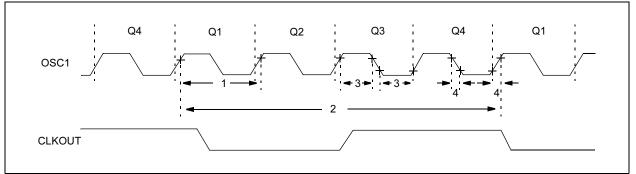

| OSC2/CLKOUT  | 15                | 17            | 0                      | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin out-<br>puts CLKOUT, which has 1/4 the frequency of OSC1<br>and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                 | 4             | I/P                    | ST                    | Master Clear (Reset) input/programming voltage input.<br>This pin is an Active Low Reset to the device.                                                                                                             |

|              |                   |               |                        |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |

| RA0/AN0      | 17                | 19            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA1/AN1      | 18                | 20            | I/O                    | ST                    | Analog comparator input                                                                                                                                                                                             |

| RA2/AN2/VREF | 1                 | 1             | I/O                    | ST                    | Analog comparator input or VREF output                                                                                                                                                                              |

| RA3/AN3      | 2                 | 2             | I/O                    | ST                    | Analog comparator input /output                                                                                                                                                                                     |

| RA4/T0CKI    | 3                 | 3             | I/O                    | ST                    | Can be selected to be the clock input to the Timer<br>timer/counter or a comparator output. Output is<br>open drain type.                                                                                           |

|              |                   |               |                        |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                                 |

| RB0/INT      | 6                 | 7             | I/O                    | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an externa interrupt pin.                                                                                                                                                           |

| RB1          | 7                 | 8             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB2          | 8                 | 9             | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB3          | 9                 | 10            | I/O                    | TTL                   |                                                                                                                                                                                                                     |

| RB4          | 10                | 11            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB5          | 11                | 12            | I/O                    | TTL                   | Interrupt-on-change pin.                                                                                                                                                                                            |

| RB6          | 12                | 13            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming clock                                                                                                                                                                   |

| RB7          | 13                | 14            | I/O                    | TTL/ST <sup>(2)</sup> | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                   |

| Vss          | 5                 | 5,6           | Р                      |                       | Ground reference for logic and I/O pins.                                                                                                                                                                            |

| Vdd          | 14                | 15,16         | Р                      | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                             |

| Legend:      | O = out<br>— = No | •             | I/O = inp<br>I = Input | ut/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                             |

TTL = TTL input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

# 4.2 Data Memory Organization

The data memory (Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20-7Fh (Bank0) on the PIC16C620A/CR620A/621A and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16C622 and PIC16C622A are General Purpose Registers implemented as static RAM. Some Special Purpose Registers are mapped in Bank 1.

Addresses F0h-FFh of bank1 are implemented as common ram and mapped back to addresses 70h-7Fh in bank0 on the PIC16C620A/621A/622A/CR620A.

## 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 80 x 8 in the PIC16C620/621, 96 x 8 in the PIC16C620A/621A/CR620A and 128 x 8 in the PIC16C622(A). Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1).                                |

|         | R/W-1                    | R/W-1                          | R/W-1                         | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|--------------------------|--------------------------------|-------------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU                     | INTEDG                         | TOCS                          | TOSE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7                    |                                |                               |                              |               | •     |       | bit 0 |

| bit 7   | RBPU: PO                 | RTB Pull-u                     | p Enable bi                   | it                           |               |       |       |       |

|         |                          | 3 pull-ups ai<br>3 pull-ups ai |                               | y individual                 | port latch va | alues |       |       |

| bit 6   | INTEDG: I                | nterrupt Edg                   | e Select bit                  | -                            |               |       |       |       |

|         |                          |                                | edge of RB0<br>edge of RB0    |                              |               |       |       |       |

| bit 5   | TOCS: TMI                | R0 Clock Sc                    | ource Select                  | bit                          |               |       |       |       |

|         |                          | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock      | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM                 | R0 Source E                    | Edge Select                   | bit                          |               |       |       |       |

|         |                          |                                |                               | ition on RA4<br>ition on RA4 |               |       |       |       |

| bit 3   | PSA: Pres                | caler Assigr                   | iment bit                     |                              | -             |       |       |       |

|         |                          |                                | ned to the W<br>ned to the Ti | DT<br>mer0 module            | Э             |       |       |       |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : F | Prescaler Ra                   | ate Select bi                 | ts                           |               |       |       |       |

|         | E                        | Bit Value T                    | MR0 Rate                      | WDT Rate                     |               |       |       |       |

|         | -                        | 0000001                        | 1:2<br>1:4                    | 1:1<br>1:2                   |               |       |       |       |

|         |                          | 010<br>011                     | 1 : 8<br>1 : 16               | 1:4<br>1:8                   |               |       |       |       |

|         |                          | 100                            | 1:32                          | 1:16                         |               |       |       |       |

|         |                          | 101                            | 1:64                          | 1:32                         |               |       |       |       |

|         |                          | 110                            | 1:128                         | 1:64                         |               |       |       |       |

|         |                          | 111                            | 1:256                         | 1 : 128                      |               |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

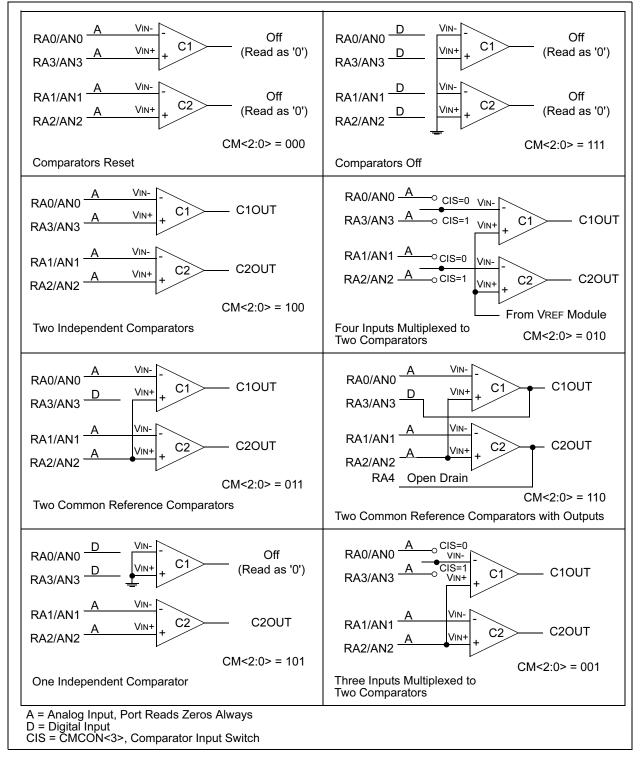

## 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

# 7.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise the maximum delay of the comparators should be used (Table 12-2).

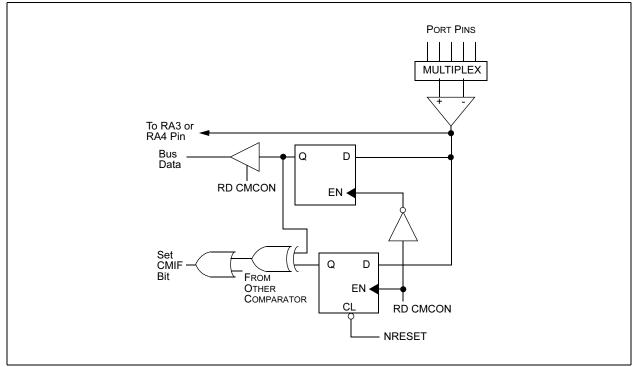

# 7.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 7-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

## FIGURE 7-3: COMPARATOR OUTPUT BLOCK DIAGRAM

| <b>TABLE 7-1</b> : | REGISTERS ASSOCIATED WITH COMPARATOR MODULE |

|--------------------|---------------------------------------------|

|--------------------|---------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 1Fh     | CMCON  | C2OUT | C10UT |       | _      | CIS    | CM2    | CM1    | CM0    | 00 0000         | 00 0000                         |

| 9Fh     | VRCON  | VREN  | VROE  | VRR   |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch     | PIR1   | _     | CMIF  | _     | _      | _      | _      | _      | _      | -0              | -0                              |

| 8Ch     | PIE1   | _     | CMIE  | _     | _      | _      | _      | _      | _      | -0              | -0                              |

| 85h     | TRISA  |       |       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as "0"

-

## TABLE 9-4: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | _       | xxxx xxxx      | <u>uuuu</u> uuuu                                                                                                                                           | <u></u>                                                                                                           |

| INDF     | 00h     |                | _                                                                                                                                                          | _                                                                                                                 |

| TMR0     | 01h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | սսսս սսսս                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

## TABLE 9-5: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:legend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-4 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

**6:** If RESET was due to brown-out, then bit 0 = 0. All other RESETS will cause bit 0 = u.

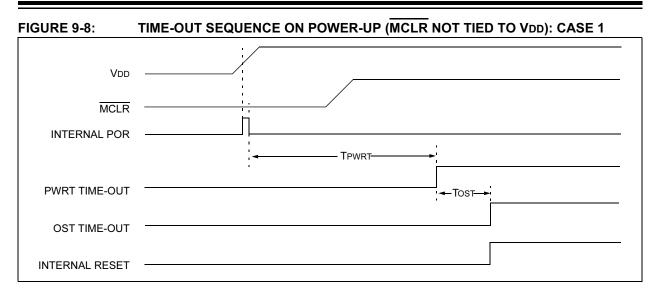

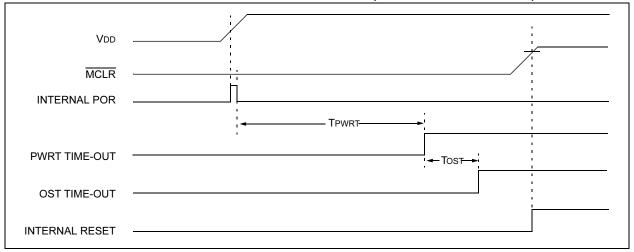

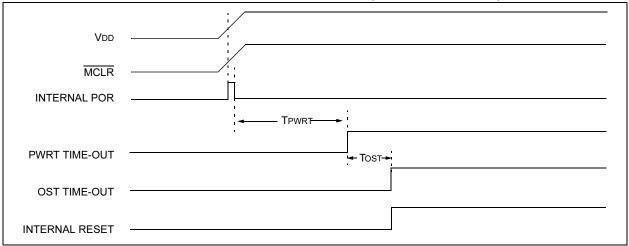

FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

| TABLE 10-2: PIC16C62X INSTRUCTION SET |

|---------------------------------------|

|---------------------------------------|

| Mnemonic,<br>Operands |          | Description                  | Cycles | 14-Bit Opcode |      |      |          | Status | Notes |

|-----------------------|----------|------------------------------|--------|---------------|------|------|----------|--------|-------|

|                       |          |                              |        | MSb           | LSb  |      | Affected |        |       |

| BYTE-OR               | ENTED I  | FILE REGISTER OPERATIONS     |        |               |      |      |          |        |       |

| ADDWF                 | f, d     | Add W and f                  | 1      | 00            | 0111 | dfff | ffff     | C,DC,Z | 1,2   |

| ANDWF                 | f, d     | AND W with f                 | 1      | 00            | 0101 | dfff | ffff     | Z      | 1,2   |

| CLRF                  | f        | Clear f                      | 1      | 00            | 0001 | lfff | ffff     | Z      | 2     |

| CLRW                  | -        | Clear W                      | 1      | 00            | 0001 | 0000 | 0011     | Z      |       |

| COMF                  | f, d     | Complement f                 | 1      | 00            | 1001 | dfff | ffff     | Z      | 1,2   |

| DECF                  | f, d     | Decrement f                  | 1      | 00            | 0011 | dfff | ffff     | Z      | 1,2   |

| DECFSZ                | f, d     | Decrement f, Skip if 0       | 1(2)   | 00            | 1011 | dfff | ffff     |        | 1,2,3 |

| INCF                  | f, d     | Increment f                  | 1      | 00            | 1010 | dfff | ffff     | Z      | 1,2   |

| INCFSZ                | f, d     | Increment f, Skip if 0       | 1(2)   | 00            | 1111 | dfff | ffff     |        | 1,2,3 |

| IORWF                 | f, d     | Inclusive OR W with f        | 1      | 00            | 0100 | dfff | ffff     | Z      | 1,2   |

| MOVF                  | f, d     | Move f                       | 1      | 00            | 1000 | dfff | ffff     | Z      | 1,2   |

| MOVWF                 | f        | Move W to f                  | 1      | 00            | 0000 | lfff | ffff     |        |       |

| NOP                   | -        | No Operation                 | 1      | 00            | 0000 | 0xx0 | 0000     |        |       |

| RLF                   | f, d     | Rotate Left f through Carry  | 1      | 00            | 1101 | dfff | ffff     | С      | 1,2   |

| RRF                   | f, d     | Rotate Right f through Carry | 1      | 00            | 1100 | dfff | ffff     | С      | 1,2   |

| SUBWF                 | f, d     | Subtract W from f            | 1      | 00            | 0010 | dfff | ffff     | C,DC,Z | 1,2   |

| SWAPF                 | f, d     | Swap nibbles in f            | 1      | 00            | 1110 | dfff | ffff     |        | 1,2   |

| XORWF                 | f, d     | Exclusive OR W with f        | 1      | 00            | 0110 | dfff | ffff     | Z      | 1,2   |

| BIT-ORIEN             | NTED FIL | E REGISTER OPERATIONS        |        |               |      |      |          | •      |       |

| BCF                   | f, b     | Bit Clear f                  | 1      | 01            | 00bb | bfff | ffff     |        | 1,2   |

| BSF                   | f, b     | Bit Set f                    | 1      | 01            | 01bb | bfff | ffff     |        | 1,2   |

| BTFSC                 | f, b     | Bit Test f, Skip if Clear    | 1 (2)  | 01            | 10bb | bfff | ffff     |        | 3     |

| BTFSS                 | f, b     | Bit Test f, Skip if Set      | 1 (2)  | 01            | 11bb | bfff | ffff     |        | 3     |

| LITERAL               | AND CO   | NTROL OPERATIONS             |        |               |      |      |          |        |       |

| ADDLW                 | k        | Add literal and W            | 1      | 11            | 111x | kkkk | kkkk     | C,DC,Z |       |

| ANDLW                 | k        | AND literal with W           | 1      | 11            | 1001 | kkkk | kkkk     | Z      |       |

| CALL                  | k        | Call subroutine              | 2      | 10            | 0kkk | kkkk | kkkk     |        |       |

| CLRWDT                | -        | Clear Watchdog Timer         | 1      | 00            | 0000 | 0110 | 0100     | TO,PD  |       |

| GOTO                  | k        | Go to address                | 2      | 10            | 1kkk | kkkk | kkkk     |        |       |

| IORLW                 | k        | Inclusive OR literal with W  | 1      | 11            | 1000 | kkkk | kkkk     | Z      |       |

| MOVLW                 | k        | Move literal to W            | 1      | 11            | 00xx | kkkk | kkkk     |        |       |

| RETFIE                | -        | Return from interrupt        | 2      | 00            | 0000 | 0000 | 1001     |        |       |

| RETLW                 | k        | Return with literal in W     | 2      | 11            | 01xx | kkkk | kkkk     |        |       |

| RETURN                | -        | Return from Subroutine       | 2      | 00            | 0000 | 0000 | 1000     |        |       |

| SLEEP                 | -        | Go into Standby mode         | 1      | 00            | 0000 | 0110 | 0011     | TO,PD  |       |

| SUBLW                 | k        | Subtract W from literal      | 1      | 11            | 110x | kkkk | kkkk     | C,DC,Z |       |

| XORLW                 | k        | Exclusive OR literal with W  | 1      | 11            | 1010 | kkkk | kkkk     | Z      |       |

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**2:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| CLRW                                                                               | Clear W                                                                                                                                                                                                                                                                                                                                                                                             | COMF                                                                                          | Complement f                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                            | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                        | Syntax:                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                           |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                | Operands:                                                                                     | $0 \leq f \leq 127$                                                                                                                                                                                                                                                                                 |

| Operation:                                                                         | $00h \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                               |                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                           |

|                                                                                    | $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                                                   | Operation:                                                                                    | $(\bar{f}) \rightarrow (dest)$                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                   | Z                                                                                                                                                                                                                                                                                                                                                                                                   | Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                          | 00 0001 0000 0011                                                                                                                                                                                                                                                                                                                                                                                   | Encoding:                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                   |

| Description:                                                                       | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                         | Description:                                                                                  | The contents of register 'f' are<br>complemented. If 'd' is 0, the                                                                                                                                                                                                                                  |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               | result is stored in W. If 'd' is 1, the result is stored back in register 'f'.                                                                                                                                                                                                                      |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                   | Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                   |

| Example                                                                            | CLRW                                                                                                                                                                                                                                                                                                                                                                                                | Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                   |

|                                                                                    | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                  | Example                                                                                       | COMF REG1,0                                                                                                                                                                                                                                                                                         |

|                                                                                    | W = 0x5A<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                       | Example                                                                                       | Before Instruction                                                                                                                                                                                                                                                                                  |

|                                                                                    | W = 0x00 $Z = 1$                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               | REG1 = 0x13<br>After Instruction<br>REG1 = 0x13<br>W = 0xEC                                                                                                                                                                                                                                         |

| CLRWDT                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| Syntax:                                                                            | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               |                                                                                                                                                                                                                                                                                                     |

| - <b>)</b>                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                     | DECF                                                                                          | Decrement f                                                                                                                                                                                                                                                                                         |

| Operands:                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                | DECF<br>Syntax:                                                                               | Decrement f                                                                                                                                                                                                                                                                                         |

|                                                                                    | None<br>00h → WDT                                                                                                                                                                                                                                                                                                                                                                                   | Syntax:                                                                                       | <b>Decrement f</b><br>[ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                      |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow \underline{WD}T$ prescaler,                                                                                                                                                                                                                                                                                                                         | -                                                                                             | [label] DECF f,d                                                                                                                                                                                                                                                                                    |

| Operands:                                                                          | None<br>00h → WDT                                                                                                                                                                                                                                                                                                                                                                                   | Syntax:                                                                                       | [ <i>label</i> ] DECF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                            |

| Operands:                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$                                                                                                                                                                                                                                                                                                    | Syntax:<br>Operands:                                                                          | $ \begin{bmatrix} \textit{label} \end{bmatrix} \text{ DECF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] $                                                                                                                                                                                                |

| Operands:<br>Operation:                                                            | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                    | Syntax:<br>Operands:<br>Operation:                                                            | $\begin{bmatrix} label \end{bmatrix} DECF f,d$<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>$(f) - 1 \rightarrow (dest)$                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:                                        | None<br>$00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$ $\overline{TO, PD}$                                                                                                                                                                                                                                                           | Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                        | [ <i>label</i> ] DECF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow PD$<br>$\overline{TO}, PD$<br>00  0000  0110  0100<br>CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>pres <u>caler of the</u> WDT. STATUS                                                                                                                | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is                                    |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \hline \overline{TO}, \overline{PD} \\ \hline \hline 00 & 0000 & 0110 & 0100 \\ \hline \\ CLRWDT \text{ instruction resets the} \\ Watchdog Timer. It also resets the \\ prescaler of the WDT. STATUS \\ bits TO and PD are set. \\ \hline \end{array}$ | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:           | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011 \qquad dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | None<br>$\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline TO, \overline{PD} \\ \hline \hline 00 & 0000 & 0110 & 0100 \\ \hline \\ CLRWDT \text{ instruction resets the} \\ Watchdog Timer. It also resets the \\ prescaler of the WDT. STATUS \\ bits TO and PD are set. \\ 1 \end{array}$      | Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words: | $\begin{bmatrix} label \end{bmatrix} DECF f,d$ $0 \le f \le 127$ $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest) Z $\boxed{00 \qquad 0011  dfff \qquad ffff}$ Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. 1     |

| SWAPF            | Swap Nibbles in f                                                  |                                            |                                          |                   |  |  |  |

|------------------|--------------------------------------------------------------------|--------------------------------------------|------------------------------------------|-------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                         |                                            |                                          |                   |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$        |                                            |                                          |                   |  |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                           |                                            | <i>,</i> .                               |                   |  |  |  |

| Status Affected: | None                                                               |                                            |                                          |                   |  |  |  |

| Encoding:        | 00                                                                 | 1110                                       | dfff                                     | ffff              |  |  |  |

| Description:     | The upper<br>register 'f<br>0, the res<br>register. I<br>placed in | " are excl<br>sult is plac<br>If 'd' is 1, | hanged<br>ced in <sup>v</sup><br>the res | d. If 'd' is<br>W |  |  |  |

| Words:           | 1                                                                  |                                            |                                          |                   |  |  |  |

| Cycles:          | 1                                                                  |                                            |                                          |                   |  |  |  |

| Example          | SWAPF                                                              | REG,                                       | 0                                        |                   |  |  |  |

|                  | Before Instruction                                                 |                                            |                                          |                   |  |  |  |

|                  |                                                                    | REG1                                       | = (                                      | DxA5              |  |  |  |

|                  | After Inst                                                         | ruction                                    |                                          |                   |  |  |  |

|                  |                                                                    | REG1<br>W                                  |                                          | 0xA5<br>0x5A      |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow TRIS$ register f;                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |  |  |

| XORLW                                                                                         | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                                                       | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Operands:                                                                                     | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Operation:                                                                                    | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Encoding:                                                                                     | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:                                                                                  | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Example:                                                                                      | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                                                                                               | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                               | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                                                                                               | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                                                                               | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| XORWF                                                                                         | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Syntax:                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |