# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

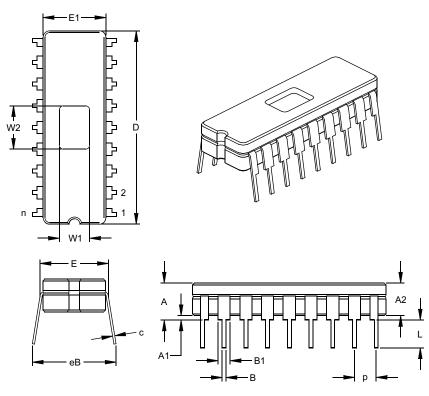

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc622t-04e-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16C62X devices are 18 and 20-Pin ROM/ EPROM-based members of the versatile PICmicro<sup>®</sup> family of low cost, high performance, CMOS, fullystatic, 8-bit microcontrollers.

All PICmicro microcontrollers employ an advanced RISC architecture. The PIC16C62X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16C62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16C620A, PIC16C621A and PIC16CR620A have 96 bytes of RAM. The PIC16C622(A) has 128 bytes of RAM. Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16C62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16C62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and RESET.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost effective One-Time-Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16C62X midrange microcontroller families.

A simplified block diagram of the PIC16C62X is shown in Figure 3-1.

The PIC16C62X series fits perfectly in applications ranging from battery chargers to low power remote sensors. The EPROM technology makes

customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C62X very versatile.

## 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to PIC16C62X family of devices (Appendix B). The PIC16C62X family fills the niche for users wanting to migrate up from the PIC16C5X family and not needing various peripheral features of other members of the PIC16XX mid-range microcontroller family.

## 1.2 Development Support

The PIC16C62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. Third Party "C" compilers are also available.

## 2.0 PIC16C62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the Oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16C62X.

Note: Microchip does not recommend code protecting windowed devices.

### 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

## 2.4 Serialized Quick-Turnaround-Production<sup>sm</sup> (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number. NOTES:

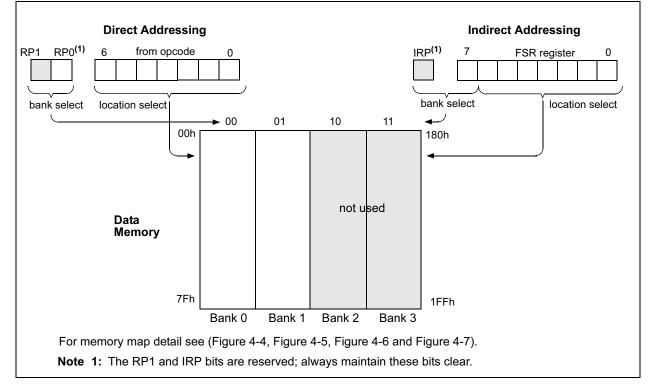

### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-9. However, IRP is not used in the PIC16C62X.

A simple program to clear RAM location 20h-7Fh using indirect addressing is shown in Example 4-1.

| EXAN  | IPLE 4- | 1: INC | DIRECT ADDRESSING    |

|-------|---------|--------|----------------------|

|       | movlw   | 0x20   | ;initialize pointer  |

|       | movwf   | FSR    | ;to RAM              |

| NEXT  | clrf    | INDF   | ;clear INDF register |

|       | incf    | FSR    | ;inc pointer         |

|       | btfss   | FSR,7  | ;all done?           |

|       | goto    | NEXT   | ;no clear next       |

|       |         |        | ;yes continue        |

| CONTI | NUE:    |        |                      |

|       |         |        |                      |

## FIGURE 4-9: DIRECT/INDIRECT ADDRESSING PIC16C62X

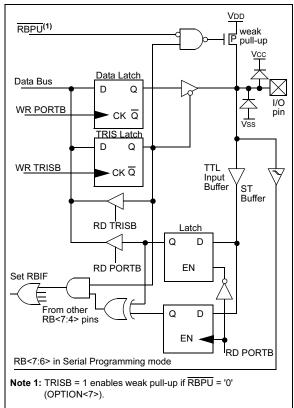

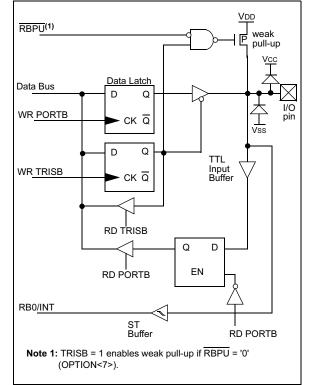

## 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a High Impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A \ typical$ ). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (e.g., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

#### FIGURE 5-5: BLOCK DIAGRAM OF RB<7:4> PINS

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes.)

| Note: | If a change on the I/O pin should occur       |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|

|       | when the read operation is being executed     |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |  |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

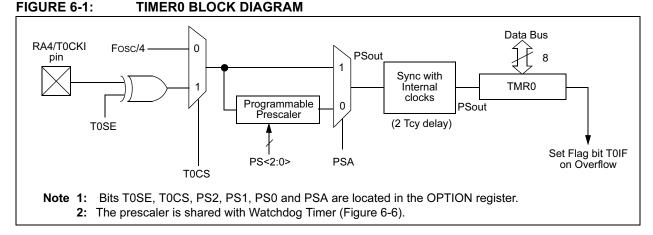

## 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to TMR0.

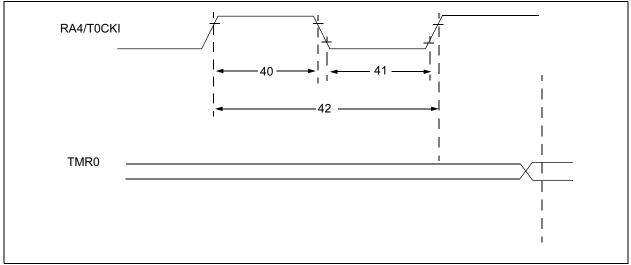

Counter mode is selected by setting the T0CS bit. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

## 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

### FIGURE 6-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| (Program<br>Counter) | ( PC-1      | ) PC        | ( <u>PC+1</u> )        | PC+2                   | <u>PC+3</u> χ          | PC+4                   | PC+5 χ                     | PC+6                     |

|----------------------|-------------|-------------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch |             | MOVWF TMR   | 0MOVF TMR0,V           | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                | 1                        |

|                      | i.          | 1           |                        |                        | i                      |                        | i                          |                          |

| TMR0                 | то х        | T0+1 )(     | T0+2 X                 | 1                      | NT0                    |                        | NT0+1 \                    | NT0+2 )                  |

| Instruction          | 1<br>1<br>1 | 1<br>1<br>1 | <b></b>                | <b>≜</b>               | <b>≜</b>               | <b>†</b>               | <b>†</b>                   | <b>≜</b>                 |

| Executed             | 1           | 1           | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + |

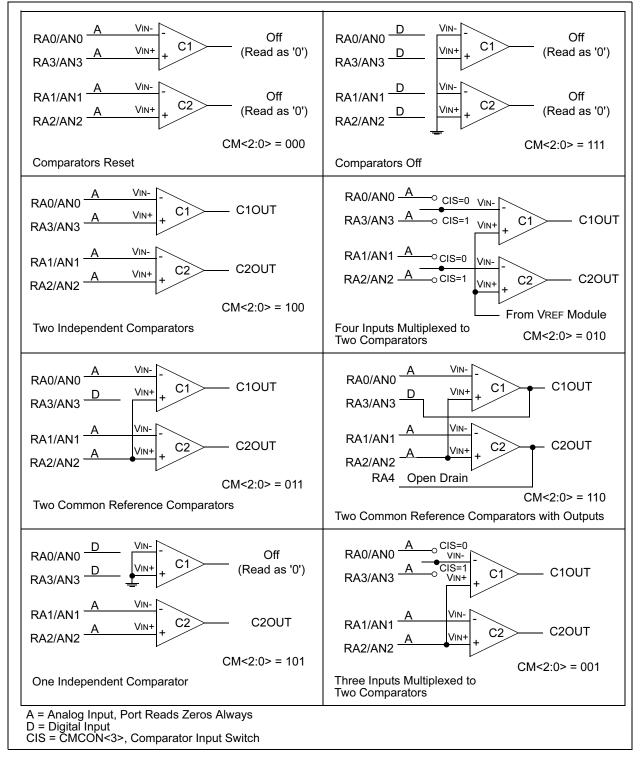

## 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

## 9.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16C62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-Circuit Serial Programming™

The PIC16C62X devices have a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 9.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs with no external circuitry drawing current from the I/O pin and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | <u> </u>                                       |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|

|       | by a WDT time-out does not drive MCLR pin low. |  |  |  |  |

|       |                                                |  |  |  |  |

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up, is cleared when SLEEP is invoked. TO bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from SLEEP, regardless of the source of wake-up.

| Q1 Q2 Q                  | 3 Q4 Q1 Q2 Q3 Q4 Q | Q1                    | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 0    | Q1 Q2 Q3 Q4 |

|--------------------------|--------------------|-----------------------|------------------|-------------|------------------|-------------|

| OSC1 //////              |                    |                       |                  |             |                  |             |

| CLKOUT(4)                |                    | Tost(2)               | <u> </u>         |             | \ <u>`</u>       |             |

| INT pin                  | 1 I                |                       | 1<br>1           |             | 1                |             |

| NTF flag                 |                    |                       | Interrupt Latend | SV.         |                  |             |

| INTCON<1>)               |                    | <del>≉</del>          | (Note 2)         | ,           |                  |             |

| GIE bit<br>INTCON<7>)    |                    | Processor in<br>SLEEP | 1                |             |                  |             |

| INSTRUCTION FLOW         |                    |                       | 1<br>1<br>1      |             | 1                |             |

| PC X PC                  | <u>Υ PC+1 Χ</u>    | PC+2                  | X PC+2           | PC + 2      | <u>χ 0004h χ</u> | 0005h       |

| Instruction { Inst(PC) = | SLEEP Inst(PC + 1) |                       | Inst(PC + 2)     |             | Inst(0004h)      | Inst(0005h) |

| Instruction Inst(PC      | - 1) SLEEP         |                       | Inst(PC + 1)     | Dummy cycle | Dummy cycle      | Inst(0004h) |

### FIGURE 9-18: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**3:** GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these Osc modes, but shown here for timing reference.

| MOVF             | Move f                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                    |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |  |  |  |  |

| MOVWF            | Move W to f                                                                                                                                                                                                                                                                          |  |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                                                                                                                                                                                             |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                    |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                                                                                                                |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:     | Move data from W register to reg-<br>ister 'f'.                                                                                                                                                                                                                                      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Example          | MOVWF OPTION                                                                                                                                                                                                                                                                         |  |  |  |  |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F                                                                                                                                                                                                |  |  |  |  |

|                  | $\begin{array}{rcl} \text{OPTION} &= & 0x4F \\ \text{W} &= & 0x4F \end{array}$                                                                                                                                                                                                       |  |  |  |  |

| NOP              | No Oper   | ation  |      |      |

|------------------|-----------|--------|------|------|

| Syntax:          | [ label ] | NOP    |      |      |

| Operands:        | None      |        |      |      |

| Operation:       | No opera  | ation  |      |      |

| Status Affected: | None      |        |      |      |

| Encoding:        | 00        | 0000   | 0xx0 | 0000 |

| Description:     | No opera  | ition. |      |      |

| Words:           | 1         |        |      |      |

| Cycles:          | 1         |        |      |      |

| Example          | NOP       |        |      |      |

| OPTION           | Load Op                                                                                                                                                                                                                                            | tion Reg | gister |      |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                          | OPTION   | N      |      |  |

| Operands:        | None                                                                                                                                                                                                                                               |          |        |      |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |          |        |      |  |

| Status Affected: | None                                                                                                                                                                                                                                               |          |        |      |  |

| Encoding:        | 00                                                                                                                                                                                                                                                 | 0000     | 0110   | 0010 |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a read-<br>able/writable register, the user can<br>directly address it. |          |        |      |  |

| Words:           | 1                                                                                                                                                                                                                                                  |          |        |      |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |          |        |      |  |

| Example          |                                                                                                                                                                                                                                                    |          |        |      |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup><br>products, do not use this<br>instruction.                                                                                                                               |          |        |      |  |

|                  |                                                                                                                                                                                                                                                    |          |        |      |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |  |  |  |

| Operands:        | None                                                                                                                                                                                                                 |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                           |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                 |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                    |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-cycle<br>instruction. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                    |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                               |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                       |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                      |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                                                         |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction.                                       |

| Words:           | 1                                                                                                                                                                                                                         |

| Cycles:          | 2                                                                                                                                                                                                                         |

| Example          | CALL TABLE;W contains table                                                                                                                                                                                               |

| TABLE            | ;offset value<br>;W now has table value<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>RETLW k2 ;<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8 |

| RETURN           | Return from Subroutine                                                                                                                                                                                                    |

| Syntax:          | [label] RETURN                                                                                                                                                                                                            |

| Operands:        | None                                                                                                                                                                                                                      |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                      |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                                                         |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction.                                                                |

| Words:           | 1                                                                                                                                                                                                                         |

| Cycles:          | 2                                                                                                                                                                                                                         |

| Example          | RETURN                                                                                                                                                                                                                    |

|                  | After Interrupt<br>PC = TOS                                                                                                                                                                                               |

| SWAPF            | Swap Ni                                                                                                                                                                    | bbles in  | f    |              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|--------------|

| Syntax:          | [label]                                                                                                                                                                    | SWAPF     | f,d  |              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |           |      |              |

| Operation:       | (f<3:0>) → (dest<7:4>),<br>(f<7:4>) → (dest<3:0>)                                                                                                                          |           |      |              |

| Status Affected: | None                                                                                                                                                                       |           |      |              |

| Encoding:        | 00                                                                                                                                                                         | 1110      | dfff | ffff         |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |           |      |              |

| Words:           | 1                                                                                                                                                                          |           |      |              |

| Cycles:          | 1                                                                                                                                                                          |           |      |              |

| Example          | SWAPF                                                                                                                                                                      | REG,      | 0    |              |

|                  | Before In                                                                                                                                                                  | struction |      |              |

|                  |                                                                                                                                                                            | REG1      | = (  | DxA5         |

|                  | After Inst                                                                                                                                                                 | ruction   |      |              |

|                  |                                                                                                                                                                            | REG1<br>W |      | 0xA5<br>0x5A |

| TRIS             | Load TRIS Register                                                                                                                                                                 |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                                                     |  |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                    |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                                  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                  |  |  |  |  |  |

| Example          |                                                                                                                                                                                    |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                             |  |  |  |  |  |

| XORLW                                                                                         | Exclusive OR Literal with W                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                       | [ <i>label</i> XORLW k<br>]                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operands:                                                                                     | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operation:                                                                                    | (W) .XOR. $k \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                   |

| Status Affected:                                                                              | Z                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Encoding:                                                                                     | 11 1010 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                               |

| Description:                                                                                  | The contents of the W register<br>are XOR'ed with the eight bit<br>literal 'k'. The result is placed in<br>the W register.                                                                                                                                                                                                                                                                                                      |

| Words:                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cycles:                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Example:                                                                                      | XORLW 0xAF                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                               | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                               | W = 0xB5                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                               | After Instruction                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                               | W = 0x1A                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XORWF                                                                                         | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                           |

| Syntax:                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| - ,                                                                                           | [ <i>label</i> ] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                      |

| Operands:                                                                                     | $\begin{bmatrix} \text{label} \end{bmatrix} \text{ XORWF}  f,d$<br>$0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                           |

| -                                                                                             | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operands:                                                                                     | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                              |

| Operands:<br>Operation:                                                                       | $0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                                                                        |

| Operands:<br>Operation:<br>Status Affected:                                                   | $0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .XOR. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                                                                   |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ Z \\ \hline \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ \end{array}$                                                                                                         |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ \hline Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \end{array}$                                                                            |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ \hline Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \\ 1 \end{array}$                                                                        |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ Z \\ \hline \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \\ 1 \\ 1 \end{array}$                                                                  |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) . XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is \\ stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \end{array}$                                                   |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .XOR. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0110 & dfff & ffff \\ \hline Exclusive OR the contents of the \\ W register with register 'f'. If 'd' is \\ 0, the result is stored in the W \\ register. If 'd' is 1, the result is stored back in register 'f'. \\ 1 \\ 1 \\ XORWF & REG & 1 \\ \hline Before Instruction \\ \hline REG & = & 0xAF \\ \end{array}$ |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                            |

NOTES:

## 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 11.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

## 11.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

## 11.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

## 11.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

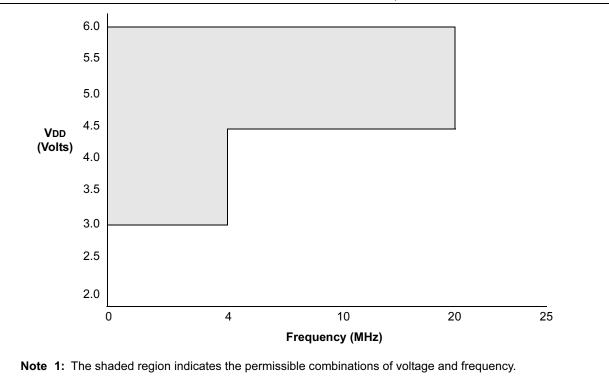

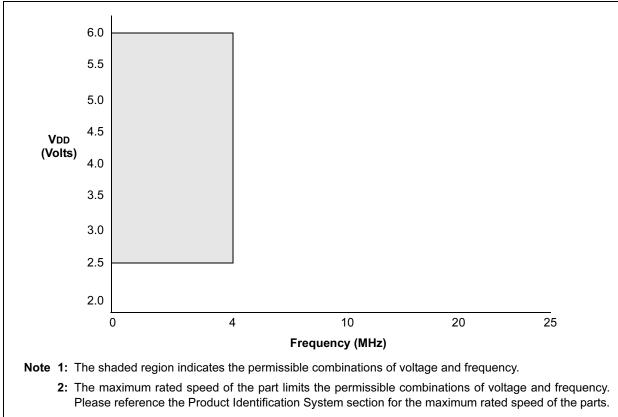

**2**: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

## 12.4 DC Characteristics: PIC16C62X/C62XA/CR62XA (Commercial, Industrial, Extended) PIC16LC62X/LC62XA/LCR62XA (Commercial, Industrial, Extended)

| PIC16C                    | 62XA/CR62XA | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial and |                                |      |                  |       |                                             |  |  |

|---------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|------------------|-------|---------------------------------------------|--|--|

|                           |             |                                                                                                                                                                                                |                                |      |                  | -40°C |                                             |  |  |

| PIC16LC62X/LC62XA/LCR62XA |             |                                                                                                                                                                                                | Operating temperature -40<br>0 |      |                  |       |                                             |  |  |

| Param.<br>No.             | Sym         | Characteristic                                                                                                                                                                                 | Min                            | Тур† | Conditions       |       |                                             |  |  |

|                           | VIL         | Input Low Voltage                                                                                                                                                                              |                                |      |                  |       |                                             |  |  |

|                           |             | I/O ports                                                                                                                                                                                      |                                |      |                  |       |                                             |  |  |

| D030                      |             | with TTL buffer                                                                                                                                                                                | Vss                            | —    | 0.8V<br>0.15 Vdd | V     | VDD = 4.5V to 5.5V<br>otherwise             |  |  |

| D031                      |             | with Schmitt Trigger input                                                                                                                                                                     | Vss                            | —    | 0.2 VDD          | V     |                                             |  |  |

| D032                      |             | MCLR, RA4/T0CKI,OSC1 (in RC mode)                                                                                                                                                              | Vss                            | —    | 0.2 VDD          | V     | (Note 1)                                    |  |  |

| D033                      |             | OSC1 (in XT and HS)                                                                                                                                                                            | Vss                            | _    | 0.3 VDD          | V     |                                             |  |  |

|                           |             | OSC1 (in LP)                                                                                                                                                                                   | Vss                            | —    | 0.6 Vdd-<br>1.0  | V     |                                             |  |  |

|                           | VIL         | Input Low Voltage                                                                                                                                                                              |                                |      |                  |       |                                             |  |  |

|                           |             | I/O ports                                                                                                                                                                                      |                                |      |                  |       |                                             |  |  |

| D030                      |             | with TTL buffer                                                                                                                                                                                | Vss                            | -    | 0.8V<br>0.15 VDD | V     | VDD = 4.5V to 5.5V<br>otherwise             |  |  |

| D031                      |             | with Schmitt Trigger input                                                                                                                                                                     | Vss                            | —    | 0.2 Vdd          | V     |                                             |  |  |

| D032                      |             | MCLR, RA4/T0CKI,OSC1 (in RC mode)                                                                                                                                                              | Vss                            | —    | 0.2 VDD          | V     | (Note 1)                                    |  |  |

| D033                      |             | OSC1 (in XT and HS)                                                                                                                                                                            | Vss                            | —    | 0.3 VDD          | V     |                                             |  |  |

|                           |             | OSC1 (in LP)                                                                                                                                                                                   | Vss                            | _    | 0.6 Vdd-<br>1.0  | V     |                                             |  |  |

|                           | VIH         | Input High Voltage                                                                                                                                                                             |                                |      |                  |       |                                             |  |  |