Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

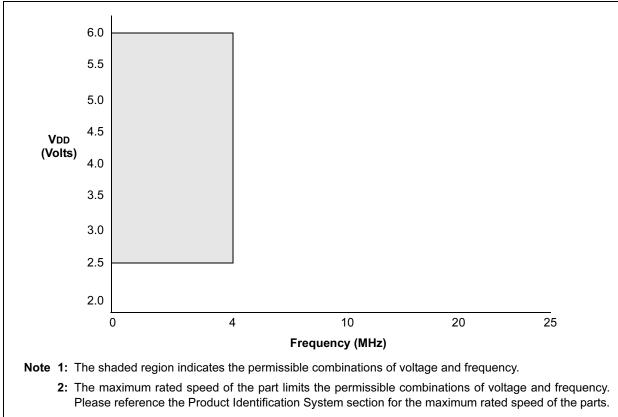

| Speed                      | 4MHz                                                                         |

| Connectivity               |                                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                |                                                                              |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | - ·                                                                          |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

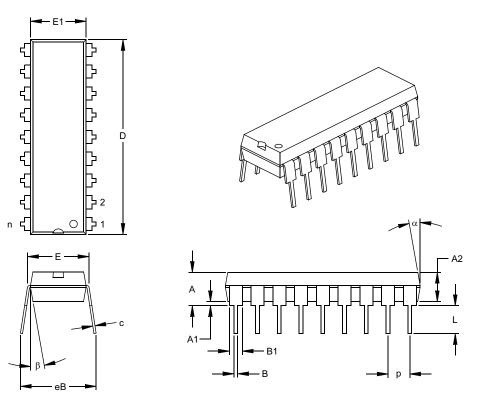

| Mounting Type              | Surface Mount                                                                |

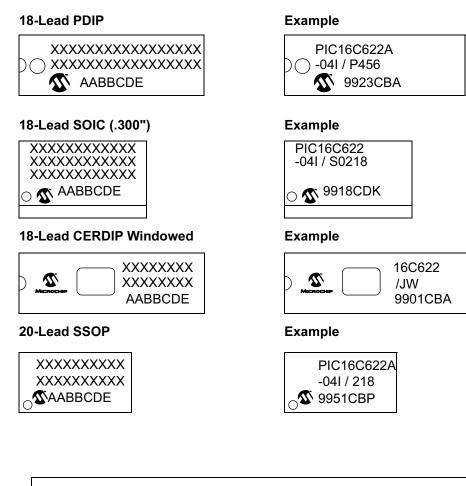

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc622t-04i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

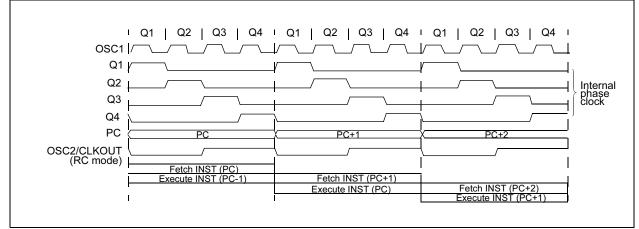

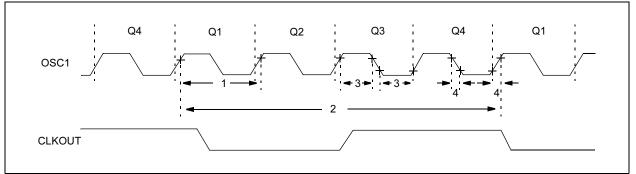

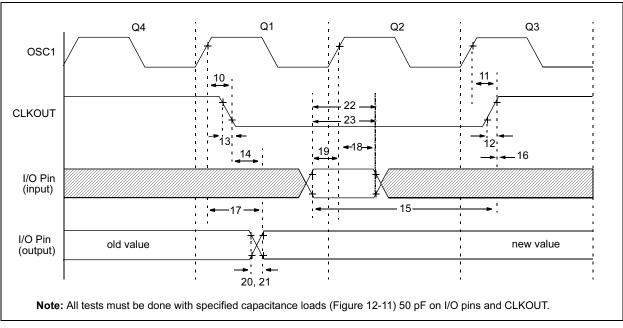

## 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

#### 3.2 Instruction Flow/Pipelining

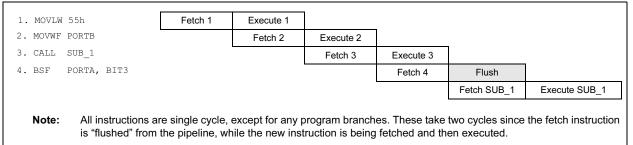

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.0 MEMORY ORGANIZATION

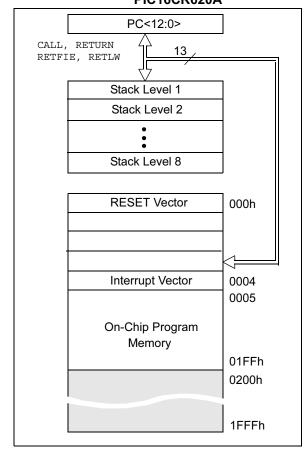

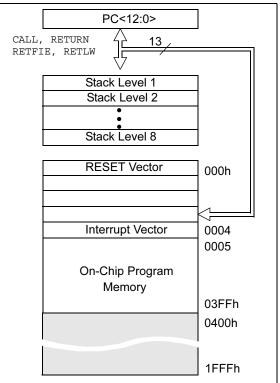

#### 4.1 Program Memory Organization

The PIC16C62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C620(A) and PIC16CR620, 1K x 14 (0000h - 03FFh) for the PIC16C621(A) and 2K x 14 (0000h - 07FFh) for the PIC16C622(A) are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16C(R)620(A)) or 1K x 14 space (PIC16C621(A)) or 2K x 14 space (PIC16C622(A)). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16C620/PIC16C620A/

PIC16C620/PIC16C620 PIC16CR620A

#### FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C621/PIC16C621A

FIGURE 4-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C622/PIC16C622A

#### 4.2.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uuluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bit. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C and DC bits</u> operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

|         | Reserved                                                                                                                                                               | Reserved                           | R/W-0          | R-1            | R-1            | R/W-x          | R/W-x        | R/W-x          |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|----------------|----------------|--------------|----------------|--|--|

|         | IRP                                                                                                                                                                    | RP1                                | RP0            | TO             | PD             | Z              | DC           | С              |  |  |

|         | bit 7                                                                                                                                                                  |                                    |                |                |                |                |              | bit 0          |  |  |

|         |                                                                                                                                                                        |                                    |                |                |                |                |              |                |  |  |

| bit 7   | -                                                                                                                                                                      | ter Bank Sel                       | -              | d for indirect | addressing     | )              |              |                |  |  |

|         |                                                                                                                                                                        | , 3 (100h - 1<br>, 1 (00h - FF     |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                                        | t is reserved                      |                | 16C62X; alv    | /ays maintai   | n this bit cle | ar.          |                |  |  |

| bit 6-5 |                                                                                                                                                                        | Register Ban                       |                |                | -              |                |              |                |  |  |

|         |                                                                                                                                                                        | 1 (80h - FFh                       |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                                        | 0 (00h - 7Fh                       |                |                |                |                |              |                |  |  |

|         | Each bank<br>clear.                                                                                                                                                    | is 128 bytes                       | . The RP1 t    | oit is reserve | ed on the PIC  | C16C62X; a     | lways mainta | ain this bit   |  |  |

| bit 4   | TO: Time-c                                                                                                                                                             | out bit                            |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                                        | ower-up, CLI                       | RWDT instruc   | ction. or SLE  | EP instruction | on             |              |                |  |  |

|         |                                                                                                                                                                        | time-out oc                        |                | ,              |                |                |              |                |  |  |

| bit 3   | PD: Power                                                                                                                                                              | -down bit                          |                |                |                |                |              |                |  |  |

|         | -                                                                                                                                                                      | ower-up or b<br>cution of the      | -              |                | n              |                |              |                |  |  |

| bit 2   | Z: Zero bit                                                                                                                                                            |                                    |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                                        | sult of an arit<br>sult of an arit |                |                |                | )              |              |                |  |  |

| bit 1   | 0 = The result of an arithmetic or logic operation is not zero<br><b>DC</b> : Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(for borrow the polarity |                                    |                |                |                |                |              |                |  |  |

|         | is reversed)                                                                                                                                                           |                                    |                |                |                |                |              |                |  |  |

|         | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul>               |                                    |                |                |                |                |              |                |  |  |

|         |                                                                                                                                                                        | -                                  |                |                |                |                |              |                |  |  |

| bit 0   | •                                                                                                                                                                      | orrow bit (AD                      |                |                |                |                |              |                |  |  |

|         | •                                                                                                                                                                      | -out from the<br>ry-out from th    | -              |                |                |                |              |                |  |  |

|         | Note:                                                                                                                                                                  | For borrow t                       | he polarity i  | s reversed.    | A subtraction  | on is execut   | ed by addin  | g the two's    |  |  |

|         |                                                                                                                                                                        | complement                         |                |                |                |                |              | s, this bit is |  |  |

|         |                                                                                                                                                                        | loaded with e                      | either the hig | gh or low or   | der bit of the | source reg     | ister.       |                |  |  |

|         | Legend:                                                                                                                                                                | L. L. 14                           |                |                |                |                | hit as a d   | 0              |  |  |

|         | R = Reada                                                                                                                                                              |                                    |                | ritable bit    |                | •              | bit, read as |                |  |  |

|         | - n = Value                                                                                                                                                            | at POR                             | 1′ = Bi        | it is set      | '0' = Bit i    | scleared       | x = Bit is u | nknown         |  |  |

#### **OPTION Register** 4.2.2.2

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | TMR0, assign the prescaler to the WDT     |  |  |  |  |  |  |  |

|       | (PSA = 1).                                |  |  |  |  |  |  |  |

|         | R/W-1                    | R/W-1                          | R/W-1                         | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|--------------------------|--------------------------------|-------------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU                     | INTEDG                         | TOCS                          | TOSE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7                    |                                |                               |                              |               | •     |       | bit 0 |

| bit 7   | RBPU: PO                 | RTB Pull-u                     | p Enable bi                   | it                           |               |       |       |       |

|         |                          | 3 pull-ups ai<br>3 pull-ups ai |                               | y individual                 | port latch va | alues |       |       |

| bit 6   | INTEDG: I                | nterrupt Edg                   | e Select bit                  | -                            |               |       |       |       |

|         |                          |                                | edge of RB0<br>edge of RB0    |                              |               |       |       |       |

| bit 5   | TOCS: TMI                | R0 Clock Sc                    | ource Select                  | bit                          |               |       |       |       |

|         |                          | ion on RA4/<br>Il instruction  | T0CKI pin<br>cycle clock      | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM                 | R0 Source E                    | Edge Select                   | bit                          |               |       |       |       |

|         |                          |                                |                               | ition on RA4<br>ition on RA4 |               |       |       |       |

| bit 3   | PSA: Pres                | caler Assigr                   | ment bit                      |                              | -             |       |       |       |

|         |                          |                                | ned to the W<br>ned to the Ti | DT<br>mer0 module            | Э             |       |       |       |

| bit 2-0 | <b>PS&lt;2:0&gt;</b> : [ | Prescaler Ra                   | ate Select bi                 | ts                           |               |       |       |       |

|         | E                        | Bit Value T                    | MR0 Rate                      | WDT Rate                     |               |       |       |       |

|         | -                        | 0000001                        | 1:2<br>1:4                    | 1:1<br>1:2                   |               |       |       |       |

|         |                          | 010<br>011                     | 1 : 8<br>1 : 16               | 1:4<br>1:8                   |               |       |       |       |

|         |                          | 100                            | 1:32                          | 1:16                         |               |       |       |       |

|         |                          | 101                            | 1:64                          | 1:32                         |               |       |       |       |

|         |                          | 110                            | 1:128                         | 1:64                         |               |       |       |       |

|         |                          | 111                            | 1:256                         | 1 : 128                      |               |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|------------|------------|------------|------------|------------|-----------------|---------------------------------|

| 05h     | PORTA |       |       |       | RA4        | RA3        | RA2        | RA1        | RA0        | x 0000          | u 0000                          |

| 85h     | TRISA |       |       | _     | TRISA<br>4 | TRISA<br>3 | TRISA<br>2 | TRISA<br>1 | TRISA<br>0 | 1 1111          | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _          | CIS        | CM2        | CM1        | CM0        | 00 0000         | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _          | VR3        | VR2        | VR1        | VR0        | 000- 0000       | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

Note: Shaded bits are not used by PORTA.

### 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-Chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Register 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-1.

#### REGISTER 7-1: CMCON REGISTER (ADDRESS 1Fh)

|         |                   |                                 | <b>(</b> | ,   |       |       |       |       |

|---------|-------------------|---------------------------------|----------|-----|-------|-------|-------|-------|

|         | R-0               | R-0                             | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | C2OUT             | C10UT                           | —        | —   | CIS   | CM2   | CM1   | CM0   |

|         | bit 7             |                                 |          |     |       |       |       | bit 0 |

|         |                   |                                 |          |     |       |       |       |       |

| bit 7   | <b>C2OUT</b> : Co | omparator 2                     | output   |     |       |       |       |       |

|         | 1 = C2 VIN        | + > C2 VIN-                     |          |     |       |       |       |       |

|         | 0 = C2 VIN        | + < C2 VIN-                     |          |     |       |       |       |       |

| bit 6   | <b>C1OUT</b> : Co | omparator 1                     | output   |     |       |       |       |       |

|         | 1 = C1 VIN        | + > C1 VIN-                     |          |     |       |       |       |       |

|         | 0 = C1 VIN        | + < C1 VIN-                     |          |     |       |       |       |       |

| bit 5-4 | Unimplem          | ented: Read                     | d as '0' |     |       |       |       |       |

| bit 3   | CIS: Comp         | arator Input                    | Switch   |     |       |       |       |       |

|         | When CM<          | <2:0>: = 001                    | :        |     |       |       |       |       |

|         | 1 = C1 VIN-       | - connects to                   | o RA3    |     |       |       |       |       |

|         | 0 = C1 VIN        | - connects to                   | o RA0    |     |       |       |       |       |

|         | When CM<          | <2:0> = 010:                    |          |     |       |       |       |       |

|         |                   | <ul> <li>connects to</li> </ul> |          |     |       |       |       |       |

|         |                   | I- connects t                   |          |     |       |       |       |       |

|         |                   | - connects to                   |          |     |       |       |       |       |

|         | C2 VIN            | I- connects t                   | 0 RA1    |     |       |       |       |       |

| bit 2-0 | CM<2:0>:          | Comparator                      | mode.    |     |       |       |       |       |

|         |                   |                                 |          |     |       |       |       |       |

|         | Legend:           |                                 |          |     |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.0 **VOLTAGE REFERENCE** MODULE

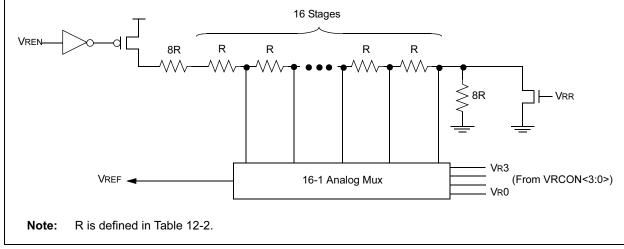

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 8-1. The block diagram is given in Figure 8-1.

#### 8.1 **Configuring the Voltage Reference**

The Voltage Reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 12-1). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

|                                                                             | R/W-0       | R/W-0                   | R/W-0                      | U-0                     | R/W-0       | R/W-0      | R/W-0        | R/W-0  |

|-----------------------------------------------------------------------------|-------------|-------------------------|----------------------------|-------------------------|-------------|------------|--------------|--------|

|                                                                             | VREN        | VROE                    | Vrr                        | —                       | VR3         | VR2        | VR1          | VR0    |

|                                                                             | bit 7       |                         |                            |                         |             |            |              | bit 0  |

|                                                                             |             |                         |                            |                         |             |            |              |        |

| bit 7                                                                       |             | Enable<br>ircuit powere | od on                      |                         |             |            |              |        |

|                                                                             |             | -                       | ed down, no                | IDD drain               |             |            |              |        |

| bit 6                                                                       |             | F Output En             |                            |                         |             |            |              |        |

|                                                                             |             | s output on F           | RA2 pin<br>ed from RA2     | 2 nin                   |             |            |              |        |

| bit 5                                                                       |             | Range sele              |                            | 2 pm                    |             |            |              |        |

| bit o                                                                       | 1 = Low Ra  |                         |                            |                         |             |            |              |        |

|                                                                             | 0 = High R  | ange                    |                            |                         |             |            |              |        |

| bit 4                                                                       | Unimplem    | ented: Rea              | d as '0'                   |                         |             |            |              |        |

| bit 3-0                                                                     |             |                         |                            | VR [3:0] ≤ 1            | 5           |            |              |        |

|                                                                             |             |                         | (VR<3:0>/ 2<br>1/4 * Voo + | 4) * VDD<br>(VR<3:0>/ 3 | 2) * \/חח   |            |              |        |

|                                                                             |             | - 0. VILLI -            |                            | (111-0.0-7-0            | 2) 100      |            |              |        |

|                                                                             | Legend:     |                         |                            |                         |             |            |              |        |

|                                                                             | R = Reada   | ble bit                 | W = W                      | /ritable bit            | U = Unim    | nplemented | bit, read as | '0'    |

|                                                                             | - n = Value | at POR                  | '1' = B                    | it is set               | '0' = Bit i | s cleared  | x = Bit is u | nknown |

| 8-1:                                                                        | VOLTAGE     | REFERE                  |                            | K DIAGRA                | M           |            |              |        |

|                                                                             |             |                         | 16 \$                      | Stages                  |             |            |              |        |

| $\sim$                                                                      |             | _                       |                            |                         | _           | _          |              |        |

| $-\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 에드 8R       | R                       | R                          | R                       | R           |            |              |        |

|                                                                             |             | <u>\</u>                |                            |                         |             | • •        |              |        |

#### **REGISTER 8-1:** VRCON REGISTER(ADDRESS 9Fh)

| Legend:            |                  |                                    |                    |  |  |

|--------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### **FIGURE 8-**

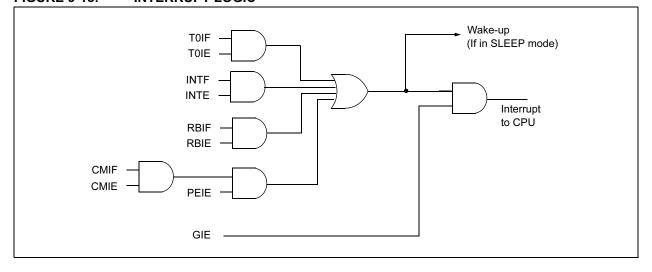

#### 9.5 Interrupts

The PIC16C62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h.

FIGURE 9-15: INTERRUPT LOGIC

Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/ INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

TABLE 9-6: SUMMARY OF INTERRUPT REGISTERS

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR<br>Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1   | —     | CMIF  | —     | —     | —     | —     | —     | —     | -0                    | -0                                             |

| 8Ch     | PIE1   | —     | CMIE  | _     | _     | —     | _     | —     | _     | -0                    | -0                                             |

**Note 1:** Other (non Power-up) Resets include MCLR Reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

#### 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 9-3 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-3:

- · Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 9-3: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP            | ;copy W to temp register,<br>;could be in either bank                       |

|-------|-------------------|-----------------------------------------------------------------------------|

| SWAPF | STATUS,W          | ;swap status to be saved<br>into W                                          |

| BCF   | STATUS, RPO       | ;change to bank 0 regardless<br>;of current bank                            |

| MOVWF | STATUS_TEMP       | ;save status to bank 0<br>;register                                         |

| :     |                   |                                                                             |

| :     | (ISR)             |                                                                             |

| :     |                   |                                                                             |

| SWAPF | STATUS_TEMP,<br>W | ;swap STATUS_TEMP register<br>;into W, sets bank to origi-<br>nal<br>;state |

| MOVWF | STATUS            | ;move W into STATUS register                                                |

| SWAPF | W_TEMP,F          | ;swap W_TEMP                                                                |

| SWAPF | W_TEMP,W          | ;swap W_TEMP into W                                                         |

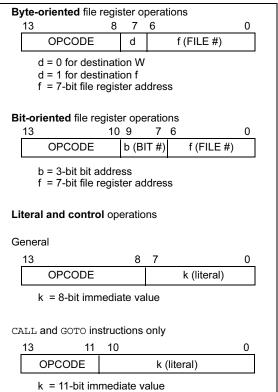

## **10.0 INSTRUCTION SET SUMMARY**

Each PIC16C62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C62X instruction set summary in Table 10-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| DESCRIPTIONS  |                                                                                                                                                                                |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Field         | Description                                                                                                                                                                    |  |  |  |  |  |

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |  |  |  |  |  |

| W             | Working register (accumulator)                                                                                                                                                 |  |  |  |  |  |

| b             | Bit address within an 8-bit file register                                                                                                                                      |  |  |  |  |  |

| k             | Literal field, constant data or label                                                                                                                                          |  |  |  |  |  |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |  |  |  |  |  |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |  |  |  |  |  |

| label         | Label name                                                                                                                                                                     |  |  |  |  |  |

| TOS           | Top of Stack                                                                                                                                                                   |  |  |  |  |  |

| PC            | Program Counter                                                                                                                                                                |  |  |  |  |  |

| PCLAT<br>H    | Program Counter High Latch                                                                                                                                                     |  |  |  |  |  |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |  |  |  |  |  |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |  |  |  |  |  |

| то            | Time-out bit                                                                                                                                                                   |  |  |  |  |  |

| PD            | Power-down bit                                                                                                                                                                 |  |  |  |  |  |

| dest          | Destination either the W register or the specified regis-<br>ter file location                                                                                                 |  |  |  |  |  |

| []            | Options                                                                                                                                                                        |  |  |  |  |  |

| ( )           | Contents                                                                                                                                                                       |  |  |  |  |  |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |  |  |  |  |  |

| < >           | Register bit field                                                                                                                                                             |  |  |  |  |  |

| e             | In the set of                                                                                                                                                                  |  |  |  |  |  |

| italics       | User defined term (font is courier)                                                                                                                                            |  |  |  |  |  |

|               | · · · · · · · · · · · · · · · · · · ·                                                                                                                                          |  |  |  |  |  |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- **Bit-oriented** operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 10-1 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

Figure 10-1 shows the three general formats that the instructions can have.

| Note: | To maintain upward compatibility with     |   |

|-------|-------------------------------------------|---|

|       | future PICmicro® products, do not use the | ÷ |

|       | OPTION and TRIS instructions.             |   |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16C62X

| INCFSZ                       | Increment f, Skip if 0                                                                                                                                                | IORWF            | Inclusive OR W with f                                                                                                                                                                                        |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                      | [ <i>label</i> ] INCFSZ f,d                                                                                                                                           | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                                                   |  |  |  |

| Operands:                    | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                    | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                           |  |  |  |

| Operation:                   | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                      | Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                                                            |  |  |  |

| Status Affected:             | None                                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                                                            |  |  |  |

| Encoding:                    | 00 1111 dfff ffff                                                                                                                                                     | Encoding:        | 00 0100 dfff ffff                                                                                                                                                                                            |  |  |  |

| Description:                 | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.                                        |  |  |  |

|                              | If the result is 0, the next instruc-<br>tion, which is already fetched, is                                                                                           | Words:           | 1                                                                                                                                                                                                            |  |  |  |

|                              | discarded. A NOP is executed                                                                                                                                          | Cycles:          | 1                                                                                                                                                                                                            |  |  |  |

|                              | instead making it a two-cycle                                                                                                                                         | Example          | IORWF RESULT, 0                                                                                                                                                                                              |  |  |  |

| Words:<br>Cycles:<br>Example | instruction.<br>1<br>1(2)<br>HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                       |                  | Before Instruction<br>$\begin{array}{rcl} \text{RESULT} &= & 0x13 \\ W &= & 0x91 \\ \end{array}$ After Instruction<br>$\begin{array}{rcl} \text{RESULT} &= & 0x13 \\ W &= & 0x93 \\ Z &= & 1 \\ \end{array}$ |  |  |  |

|                              | Before Instruction                                                                                                                                                    | MOVLW            | Move Literal to W                                                                                                                                                                                            |  |  |  |

|                              | PC = address HERE<br>After Instruction                                                                                                                                | Syntax:          | [ <i>label</i> ] MOVLW k                                                                                                                                                                                     |  |  |  |

|                              | CNT = CNT + 1                                                                                                                                                         | Operands:        | $0 \le k \le 255$                                                                                                                                                                                            |  |  |  |

|                              | if CNT= 0,<br>PC = address CONTINUE                                                                                                                                   | Operation:       | $k \rightarrow (W)$                                                                                                                                                                                          |  |  |  |

|                              | if CNT≠ 0,                                                                                                                                                            | Status Affected: | None                                                                                                                                                                                                         |  |  |  |

|                              | PC = address HERE +1                                                                                                                                                  | Encoding:        | 11 00xx kkkk kkkk                                                                                                                                                                                            |  |  |  |

| IORLW                        | Inclusive OR Literal with W                                                                                                                                           | Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's.                                                                                                             |  |  |  |

| Syntax:                      | [ <i>label</i> ] IORLW k                                                                                                                                              | Words:           | 1                                                                                                                                                                                                            |  |  |  |

| Operands:                    | $0 \le k \le 255$                                                                                                                                                     | Cycles:          | 1                                                                                                                                                                                                            |  |  |  |

| Operation:                   | (W) .OR. $k \rightarrow$ (W)                                                                                                                                          | Example          | MOVLW 0x5A                                                                                                                                                                                                   |  |  |  |

| Status Affected:             | Z                                                                                                                                                                     | Example          | After Instruction                                                                                                                                                                                            |  |  |  |

| Encoding:                    | 11 1000 kkkk kkkk                                                                                                                                                     |                  | W = 0x5A                                                                                                                                                                                                     |  |  |  |

| Description:                 | The contents of the W register is<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register.                                              |                  |                                                                                                                                                                                                              |  |  |  |

| Words:                       | 1                                                                                                                                                                     |                  |                                                                                                                                                                                                              |  |  |  |

| Cycles:                      | 1                                                                                                                                                                     |                  |                                                                                                                                                                                                              |  |  |  |

| Example                      | IORLW 0x35                                                                                                                                                            |                  |                                                                                                                                                                                                              |  |  |  |

|                              | Before Instruction<br>W = 0x9A<br>After Instruction                                                                                                                   |                  |                                                                                                                                                                                                              |  |  |  |

|                              | $W = 0_{\rm Y} {\rm BE}$                                                                                                                                              |                  |                                                                                                                                                                                                              |  |  |  |

W = Z =

0xBF 1

#### 11.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

#### 11.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

#### 11.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

### 11.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

#### 11.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow onboard hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface, ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

### 11.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

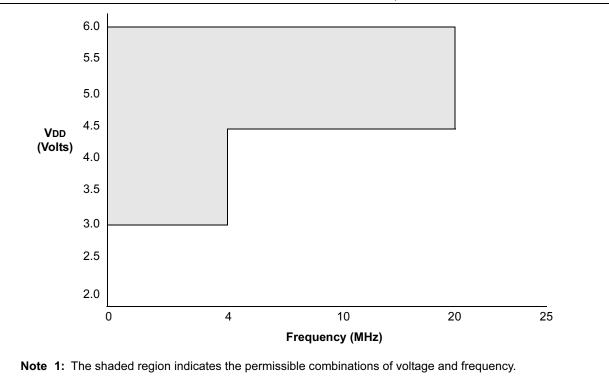

# PIC16C62X

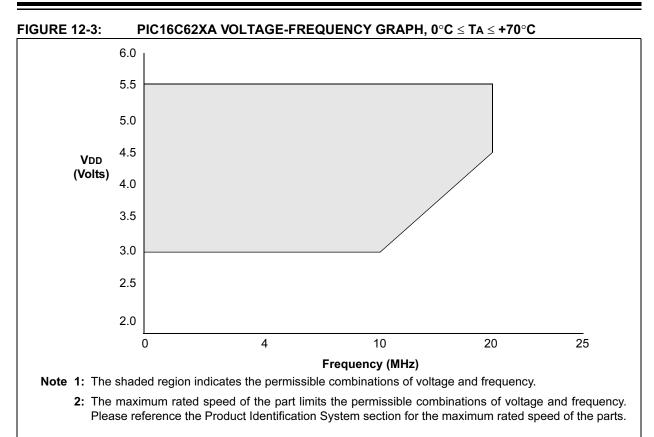

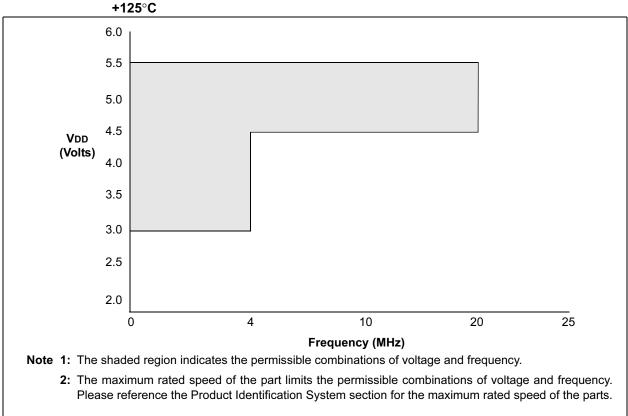

**2**: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

## FIGURE 12-4: PIC16C62XA VOLTAGE-FREQUENCY GRAPH, $-40^{\circ}C \le Ta \le 0^{\circ}C$ , $+70^{\circ}C \le Ta \le +125^{\circ}C$

#### 12.4 DC Characteristics: PIC16C62X/C62XA/CR62XA (Commercial, Industrial, Extended) PIC16LC62X/LC62XA/LCR62XA (Commercial, Industrial, Extended) (CONT.)

| PIC16C        | $ \begin{array}{ l l l l l l l l l l l l l l l l l l l$                                                                                                                                                                                                               |                                                                     |                            |     |            |       |                                                             |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------|-----|------------|-------|-------------------------------------------------------------|--|--|

| PIC16L0       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial and $-40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extended |                                                                     |                            |     |            |       |                                                             |  |  |

| Param.<br>No. | Sym                                                                                                                                                                                                                                                                   | Characteristic                                                      | Characteristic Min Typ†    |     |            | Units | Conditions                                                  |  |  |

|               | Vih                                                                                                                                                                                                                                                                   | Input High Voltage                                                  |                            |     |            |       |                                                             |  |  |

| D040          |                                                                                                                                                                                                                                                                       | with TTL buffer                                                     | 2.0V<br>0.25 VDD<br>+ 0.8V | _   | Vdd<br>Vdd | V     | VDD = 4.5V to 5.5V<br>otherwise                             |  |  |

| D041          |                                                                                                                                                                                                                                                                       | with Schmitt Trigger input                                          | 0.8 Vdd                    | _   | VDD        |       |                                                             |  |  |

| D042          |                                                                                                                                                                                                                                                                       | MCLR RA4/T0CKI                                                      | 0.8 VDD                    | _   | Vdd        | V     |                                                             |  |  |

| D043<br>D043A |                                                                                                                                                                                                                                                                       | OSC1 (XT, HS and LP)<br>OSC1 (in RC mode)                           | 0.7 Vdd<br>0.9 Vdd         | -   | Vdd        | V     | (Note 1)                                                    |  |  |

| D070          | IPURB                                                                                                                                                                                                                                                                 | PORTB weak pull-up current                                          | 50                         | 200 | 400        | μA    | VDD = 5.0V, VPIN = VSS                                      |  |  |

| D070          | IPURB                                                                                                                                                                                                                                                                 | PORTB weak pull-up current                                          | 50                         | 200 | 400        | μA    | VDD = 5.0V, VPIN = VSS                                      |  |  |

|               | lı∟                                                                                                                                                                                                                                                                   | Input Leakage Current <sup>(2, 3)</sup><br>I/O ports (Except PORTA) |                            |     | ±1.0       | μA    | Vss ≤ VPIN ≤ VDD, pin at hi-impedance                       |  |  |

| D060          |                                                                                                                                                                                                                                                                       | PORTA                                                               | _                          | _   | ±0.5       | μΑ    | $Vss \leq VPIN \leq VDD$ , pin at hi-impedance              |  |  |

| D061          |                                                                                                                                                                                                                                                                       | RA4/T0CKI                                                           | _                          | _   | ±1.0       | μΑ    | $Vss \leq VPIN \leq VDD$                                    |  |  |

| D063          |                                                                                                                                                                                                                                                                       | OSC1, MCLR                                                          | _                          | _   | ±5.0       | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |  |

|               | lı∟                                                                                                                                                                                                                                                                   | Input Leakage Current <sup>(2, 3)</sup>                             |                            |     |            |       |                                                             |  |  |

|               |                                                                                                                                                                                                                                                                       | I/O ports (Except PORTA)                                            |                            |     | ±1.0       | μA    | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance             |  |  |

| D060          |                                                                                                                                                                                                                                                                       | PORTA                                                               | -                          | —   | ±0.5       | μA    | $Vss \le VPIN \le VDD$ , pin at hi-impedance                |  |  |

| D061          |                                                                                                                                                                                                                                                                       | RA4/T0CKI                                                           | -                          | —   | ±1.0       | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                    |  |  |

| D063          |                                                                                                                                                                                                                                                                       | OSC1, MCLR                                                          | —                          | —   | ±5.0       | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |  |

|               | Vol                                                                                                                                                                                                                                                                   | Output Low Voltage                                                  |                            |     |            |       |                                                             |  |  |

| D080          |                                                                                                                                                                                                                                                                       | I/O ports                                                           | —                          | —   | 0.6        | V     | IOL = 8.5 mA, VDD = 4.5V, $-40^{\circ}$ to $+85^{\circ}$ C  |  |  |

|               |                                                                                                                                                                                                                                                                       |                                                                     | —                          | -   | 0.6        | V     | IOL = 7.0 mA, VDD = 4.5V, +125°C                            |  |  |

| D083          |                                                                                                                                                                                                                                                                       | OSC2/CLKOUT (RC only)                                               | —                          | -   | 0.6        | V     | IOL = 1.6 mA, VDD = 4.5V, $-40^{\circ}$ to $+85^{\circ}$ C  |  |  |

|               |                                                                                                                                                                                                                                                                       |                                                                     | —                          | —   | 0.6        | V     | IOL = 1.2 mA, VDD = 4.5V, +125°C                            |  |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C62X(A) be driven with external clock in RC mode.