# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                       |

| Speed                           | 66MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                  |

| RAM Controllers                 | DRAM                                                                 |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | · ·                                                                  |

| Ethernet                        | 10/100Mbps (2)                                                       |

| SATA                            | -                                                                    |

| USB                             | USB 2.0 (1)                                                          |

| Voltage - I/O                   | 3.3V                                                                 |

| Operating Temperature           | -40°C ~ 100°C (TA)                                                   |

| Security Features               | -                                                                    |

| Package / Case                  | 256-BBGA                                                             |

| Supplier Device Package         | 256-PBGA (23x23)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc870cvr66 |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

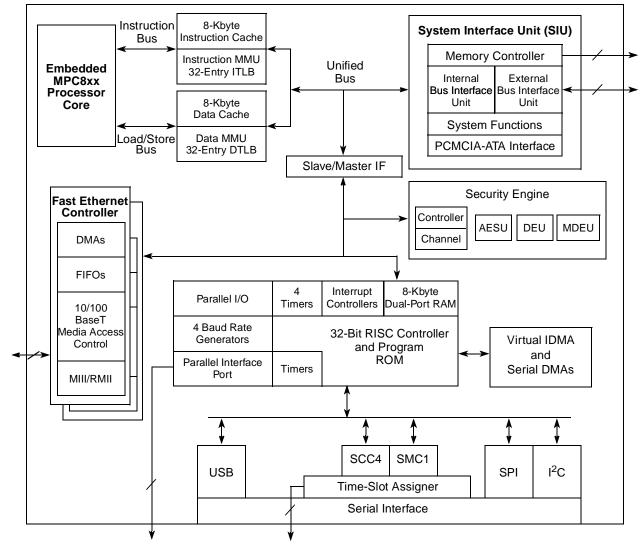

The MPC875 block diagram is shown in Figure 1.

Figure 1. MPC875 Block Diagram

Layout Practices

| Register/Configuration                 | Field                                 | Value<br>(Binary) |

|----------------------------------------|---------------------------------------|-------------------|

| PADIR (Port A data direction register) | PADIR[5:9]<br>PADIR[12:13]            | 0                 |

| PBPAR (Port B pin assignment register) | PBPAR[14:18]<br>PBPAR[20:22]          | 0                 |

| PBDIR (Port B data direction register) | PBDIR[14:8]<br>PBDIR[20:22]           | 0                 |

| PCPAR (Port C pin assignment register) | PCPAR[4:5]<br>PCPAR[8:9]<br>PCPAR[14] | 0                 |

| PCDIR (Port C data direction register) | PCDIR[4:5]<br>PCDIR[8:9]<br>PCDIR[14] | 0                 |

| PDPAR (Port D pin assignment register) | PDPAR[3:7]<br>PDPAR[9:5]              | 0                 |

| PDDIR (Port D data direction register) | PDDIR[3:7]<br>PDDIR[9:15]             | 0                 |

#### Table 7. Mandatory Reset Configuration of MPC875/MPC870 (continued)

## **10 Layout Practices**

Each  $V_{DD}$  pin on the MPC875/MPC870 should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1-µF bypass capacitors located as close as possible to the four sides of the package. Each board designed should be characterized and additional appropriate decoupling capacitors should be used if required. The capacitor leads and associated printed-circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than half an inch per capacitor lead. At a minimum, a four-layer board employing two inner layers as  $V_{DD}$  and GND planes should be used.

All output pins on the MPC875/MPC870 have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of 6 inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the V<sub>DD</sub> and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins. For more information, refer to Section 14.4.3, "Clock Synthesizer Power (V<sub>DDSYN</sub>, V<sub>SSSYN</sub>, V<sub>SSSYN1</sub>)," in the *MPC885 PowerQUICC*<sup>TM</sup> *Family Reference Manual*.

**Bus Signal Timing**

| Num  | Characteristic                                                                                                                                               |      | 33 MHz |      | 40 MHz |      | MHz   | 80 MHz |       | Unit |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|--------|------|-------|--------|-------|------|

| num  |                                                                                                                                                              |      | Max    | Min  | Мах    | Min  | Мах   | Min    | Мах   | Unit |

| B2   | CLKOUT pulse width low (MIN = $0.4 \times B1$ ,<br>MAX = $0.6 \times B1$ )                                                                                   |      | 18.2   | 10.0 | 15.0   | 6.1  | 9.1   | 5.0    | 7.5   | ns   |

| B3   | CLKOUT pulse width high (MIN = $0.4 \times B1$ , MAX = $0.6 \times B1$ )                                                                                     | 12.1 | 18.2   | 10.0 | 15.0   | 6.1  | 9.1   | 5.0    | 7.5   | ns   |

| B4   | CLKOUT rise time                                                                                                                                             |      | 4.00   | —    | 4.00   | _    | 4.00  | _      | 4.00  | ns   |

| B5   | CLKOUT fall time                                                                                                                                             | _    | 4.00   | —    | 4.00   | —    | 4.00  | —      | 4.00  | ns   |

| B7   | CLKOUT to A(0:31), BADDR(28:30), RD/ $\overline{WR}$ , BURST, D(0:31) output hold (MIN = 0.25 × B1)                                                          | 7.60 | —      | 6.30 | —      | 3.80 | —     | 3.13   | —     | ns   |

| B7a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ , $\overline{\text{BDIP}}$ , PTR output hold (MIN = 0.25 × B1)                        | 7.60 | —      | 6.30 | —      | 3.80 | —     | 3.13   | —     | ns   |

| B7b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , FRZ, VFLS(0:1), VF(0:2)<br>IWP(0:2), LWP(0:1), $\overline{STS}$ output hold<br>(MIN = 0.25 × B1)               | 7.60 | —      | 6.30 | —      | 3.80 | —     | 3.13   | —     | ns   |

| B8   | CLKOUT to A(0:31), BADDR(28:30), RD/ $\overline{WR}$ ,<br>BURST, D(0:31) valid (MAX = 0.25 × B1 + 6.3)                                                       | _    | 13.80  | —    | 12.50  | —    | 10.00 | —      | 9.43  | ns   |

| B8a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ , $\overline{\text{BDIP}}$ , PTR valid (MAX = 0.25 × B1 + 6.3)                        | _    | 13.80  | —    | 12.50  | —    | 10.00 | —      | 9.43  | ns   |

| B8b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , VFLS(0:1), VF(0:2),<br>IWP(0:2), FRZ, LWP(0:1), $\overline{STS}$ valid <sup>2</sup><br>(MAX = 0.25 × B1 + 6.3) | _    | 13.80  | —    | 12.50  | —    | 10.00 | —      | 9.43  | ns   |

| B9   | CLKOUT to A(0:31), BADDR(28:30), RD/WR,<br>BURST, D(0:31), TSIZ(0:1), REG, RSV, PTR<br>High-Z (MAX = 0.25 × B1 + 6.3)                                        | 7.60 | 13.80  | 6.30 | 12.50  | 3.80 | 10.00 | 3.13   | 9.43  | ns   |

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion<br>(MAX = 0.25 × B1 + 6.0)                                                                             | 7.60 | 13.60  | 6.30 | 12.30  | 3.80 | 9.80  | 3.13   | 9.13  | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion (when driven by<br>the memory controller or PCMCIA interface)<br>(MAX = $0.00 \times B1 + 9.30^{1}$ )  | 2.50 | 9.30   | 2.50 | 9.30   | 2.50 | 9.80  | 2.5    | 9.3   | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation<br>(MAX = 0.25 × B1 + 4.8)                                                                              | 7.60 | 12.30  | 6.30 | 11.00  | 3.80 | 8.50  | 3.13   | 7.92  | ns   |

| B12a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ negation (when driven by<br>the memory controller or PCMCIA interface)<br>(MAX = $0.00 \times B1 + 9.00$ )       | 2.50 | 9.00   | 2.50 | 9.00   | 2.50 | 9.00  | 2.5    | 9.00  | ns   |

| B13  | CLKOUT to $\overline{\text{TS}}$ , $\overline{\text{BB}}$ High-Z (MIN = 0.25 × B1)                                                                           | 7.60 | 21.60  | 6.30 | 20.30  | 3.80 | 14.00 | 3.13   | 12.93 | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ High-Z (when driven by the memory controller or PCMCIA interface)<br>(MIN = $0.00 \times B1 + 2.5$ )             |      | 15.00  | 2.50 | 15.00  | 2.50 | 15.00 | 2.5    | 15.00 | ns   |

| B14  | CLKOUT to $\overline{\text{TEA}}$ assertion<br>(MAX = $0.00 \times \text{B1} + 9.00$ )                                                                       | 2.50 | 9.00   | 2.50 | 9.00   | 2.50 | 9.00  | 2.50   | 9.00  | ns   |

#### Table 10. Bus Operation Timings (continued)

| Nivues | Characteristic                                                                                                                                                                   |       | 33 MHz |       | 40 MHz |      | MHz   | 80   | MHz   | Unit |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|--------|------|-------|------|-------|------|

| Num    |                                                                                                                                                                                  |       | Max    | Min   | Мах    | Min  | Max   | Min  | Мах   | Unit |

| B15    | CLKOUT to $\overline{\text{TEA}}$ High-Z<br>(MIN = 0.00 × B1 + 2.50)                                                                                                             |       | 15.00  | 2.50  | 15.00  | 2.50 | 15.00 | 2.50 | 15.00 | ns   |

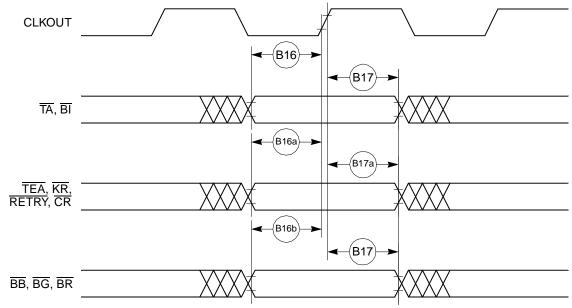

| B16    | $\overline{\text{TA}}$ , $\overline{\text{BI}}$ valid to CLKOUT (setup time)<br>(MIN = 0.00 × B1 + 6.00)                                                                         | 6.00  |        | 6.00  | _      | 6.00 | _     | 6    | _     | ns   |

| B16a   | TEA, $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid to CLKOUT (setup time) (MIN = 0.00 × B1 + 4.5)                                            | 4.50  | —      | 4.50  | —      | 4.50 | —     | 4.50 | —     | ns   |

| B16b   | $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ , valid to CLKOUT (setup time) <sup>2</sup><br>(4MIN = 0.00 × B1 + 0.00)                                                     | 4.00  | —      | 4.00  | —      | 4.00 | —     | 4.00 | —     | ns   |

| B17    | CLKOUT to $\overline{TA}$ , $\overline{TEA}$ , $\overline{BI}$ , $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ valid<br>(hold time) (MIN = 0.00 × B1 + 1.00 <sup>3</sup> ) | 1.00  | —      | 1.00  | —      | 2.00 | —     | 2.00 | —     | ns   |

| B17a   | CLKOUT to $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid (hold time)<br>(MIN = 0.00 × B1 + 2.00)                                              | 2.00  | —      | 2.00  | —      | 2.00 | —     | 2.00 | —     | ns   |

| B18    | D(0:31) valid to CLKOUT rising edge (setup time) <sup>4</sup> (MIN = $0.00 \times B1 + 6.00$ )                                                                                   | 6.00  | —      | 6.00  | —      | 6.00 | —     | 6.00 | —     | ns   |

| B19    | CLKOUT rising edge to D(0:31) valid (hold time) <sup>4</sup> (MIN = $0.00 \times B1 + 1.00^5$ )                                                                                  | 1.00  |        | 1.00  | —      | 2.00 | _     | 2.00 | —     | ns   |

| B20    | D(0:31) valid to CLKOUT falling edge (setup time) <sup>6</sup> (MIN = $0.00 \times B1 + 4.00$ )                                                                                  | 4.00  | _      | 4.00  | —      | 4.00 | _     | 4.00 | —     | ns   |

| B21    | CLKOUT falling edge to D(0:31) valid (hold time) <sup>6</sup> (MIN = $0.00 \times B1 + 2.00$ )                                                                                   | 2.00  | _      | 2.00  | —      | 2.00 | —     | 2.00 | —     | ns   |

| B22    | CLKOUT rising edge to $\overline{CS}$ asserted GPCM<br>ACS = 00 (MAX = 0.25 × B1 + 6.3)                                                                                          | 7.60  | 13.80  | 6.30  | 12.50  | 3.80 | 10.00 | 3.13 | 9.43  | ns   |

| B22a   | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 10, TRLX = 0 (MAX = 0.00 × B1 + 8.00)                                                                              | _     | 8.00   | —     | 8.00   |      | 8.00  | —    | 8.00  | ns   |

| B22b   | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = 0, EBDF = 0<br>(MAX = 0.25 × B1 + 6.3)                                                                  | 7.60  | 13.80  | 6.30  | 12.50  | 3.80 | 10.00 | 3.13 | 9.43  | ns   |

| B22c   | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = 0, EBDF = 1<br>(MAX = 0.375 × B1 + 6.6)                                                                 | 10.90 | 18.00  | 10.90 | 16.00  | 5.20 | 12.30 | 4.69 | 10.93 | ns   |

| B23    | CLKOUT rising edge to $\overline{CS}$ negated GPCM<br>read access, GPCM write access ACS = 00,<br>TRLX = 0 and CSNT = 0<br>(MAX = 0.00 × B1 + 8.00)                              | 2.00  | 8.00   | 2.00  | 8.00   | 2.00 | 8.00  | 2.00 | 8.00  | ns   |

| B24    | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 0<br>(MIN = $0.25 \times B1 - 2.00$ )                                                              | 5.60  | _      | 4.30  | —      | 1.80 | —     | 1.13 | —     | ns   |

| B24a   | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 11, TRLX = 0<br>(MIN = 0.50 × B1 - 2.00)                                                                      | 13.20 |        | 10.50 | —      | 5.60 | —     | 4.25 | —     | ns   |

#### Table 10. Bus Operation Timings (continued)

**Bus Signal Timing**

| Num  | Characteristic                                                                                                                                                                                                                               | 33    | MHz   | 40 MHz |       | 66    | MHz   | 80    | MHz   | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------|-------|-------|-------|-------|-------|------|

| Num  | Characteristic                                                                                                                                                                                                                               | Min   | Max   | Min    | Max   | Min   | Max   | Min   | Max   | Unit |

| B30d | $\overline{WE}(0:3)/BS\_B[0:3] \text{ negated to } A(0:31),$<br>BADDR(28:30) invalid GPCM write access<br>TRLX = 1, CSNT =1, $\overline{CS}$ negated to A(0:31)<br>invalid GPCM write access TRLX = 1,<br>CSNT = 1, ACS = 10 or 11, EBDF = 1 |       |       | 31.38  |       | 17.83 |       | 14.19 |       | ns   |

| B31  | CLKOUT falling edge to $\overline{CS}$ valid as requested<br>by control bit CST4 in the corresponding word<br>in the UPM (MAX = $0.00 \times B1 + 6.00$ )                                                                                    | 1.50  | 6.00  | 1.50   | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | ns   |

| B31a | CLKOUT falling edge to $\overline{CS}$ valid as requested<br>by control bit CST1 in the corresponding word<br>in the UPM (MAX = $0.25 \times B1 + 6.80$ )                                                                                    | 7.60  | 14.30 | 6.30   | 13.00 | 3.80  | 10.50 | 3.13  | 10.00 | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid, as requested<br>by control bit CST2 in the corresponding word<br>in the UPM (MAX = $0.00 \times B1 + 8.00$ )                                                                                    | 1.50  | 8.00  | 1.50   | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | ns   |

| B31c | CLKOUT rising edge to $\overline{CS}$ valid, as requested<br>by control bit CST3 in the corresponding word<br>in the UPM (MAX = $0.25 \times B1 + 6.30$ )                                                                                    |       | 13.80 | 6.30   | 12.50 | 3.80  | 10.00 | 3.13  | 9.40  | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$ valid as requested<br>by control bit CST1 in the corresponding word<br>in the UPM EBDF = 1<br>(MAX = 0.375 × B1 + 6.6)                                                                                | 13.30 | 18.00 | 11.30  | 16.00 | 7.60  | 12.30 | 4.69  | 11.30 | ns   |

| B32  | CLKOUT falling edge to $\overline{\text{BS}}$ valid as requested<br>by control bit BST4 in the corresponding word<br>in the UPM (MAX = 0.00 × B1 + 6.00)                                                                                     | 1.50  | 6.00  | 1.50   | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | ns   |

| B32a | CLKOUT falling edge to $\overline{BS}$ valid as requested<br>by control bit BST1 in the corresponding word<br>in the UPM, EBDF = 0<br>(MAX = 0.25 × B1 + 6.80)                                                                               | 7.60  | 14.30 | 6.30   | 13.00 | 3.80  | 10.50 | 3.13  | 10.00 | ns   |

| B32b | CLKOUT rising edge to $\overline{\text{BS}}$ valid, as requested<br>by control bit BST2 in the corresponding word<br>in the UPM (MAX = $0.00 \times \text{B1} + 8.00$ )                                                                      | 1.50  | 8.00  | 1.50   | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | ns   |

| B32c | CLKOUT rising edge to $\overline{\text{BS}}$ valid, as requested<br>by control bit BST3 in the corresponding word<br>in the UPM (MAX = $0.25 \times \text{B1} + 6.80$ )                                                                      | 7.60  | 14.30 | 6.30   | 13.00 | 3.80  | 10.50 | 3.13  | 10.00 | ns   |

| B32d | CLKOUT falling edge to $\overline{\text{BS}}$ valid as requested<br>by control bit BST1 in the corresponding word<br>in the UPM, EBDF = 1<br>(MAX = 0.375 × B1 + 6.60)                                                                       |       | 18.00 | 11.30  | 16.00 | 7.60  | 12.30 | 4.49  | 11.30 | ns   |

| B33  | CLKOUT falling edge to $\overline{\text{GPL}}$ valid as<br>requested by control bit GxT4 in the<br>corresponding word in the UPM<br>(MAX = 0.00 × B1 + 6.00)                                                                                 | 1.50  | 6.00  | 1.50   | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | ns   |

#### Table 10. Bus Operation Timings (continued)

Figure 9 provides the timing for the synchronous input signals.

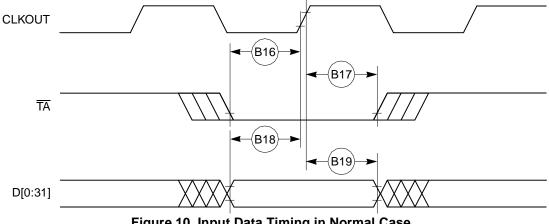

Figure 10 provides normal case timing for input data. It also applies to normal read accesses under the control of the user-programmable machine (UPM) in the memory controller.

Figure 10. Input Data Timing in Normal Case

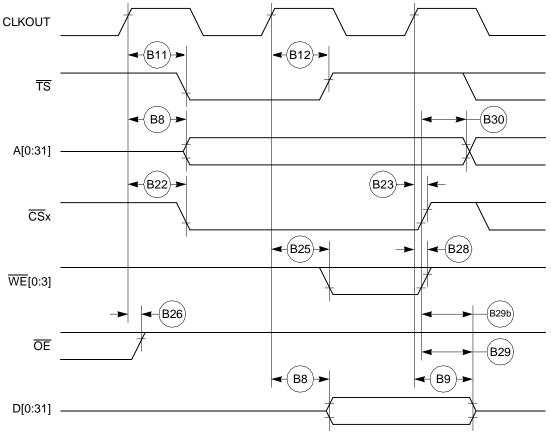

Figure 16 through Figure 18 provide the timing for the external bus write controlled by various GPCM factors.

```

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 0)

```

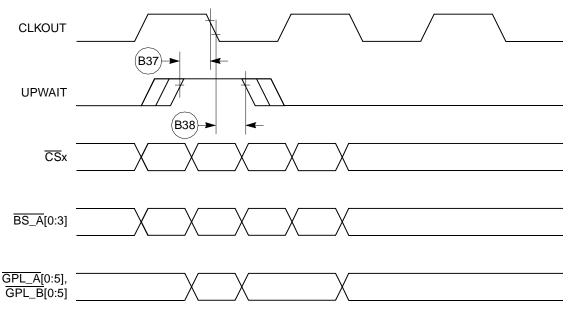

Figure 20 provides the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Figure 20. Asynchronous UPWAIT Asserted Detection in UPM Handled Cycles Timing

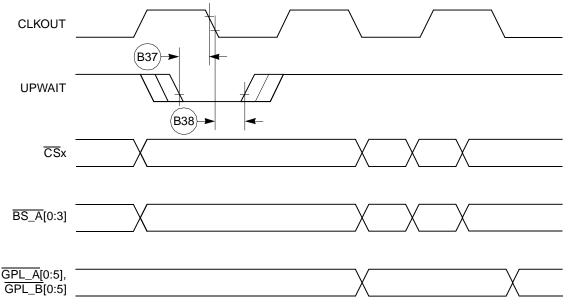

Figure 21 provides the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

Figure 21. Asynchronous UPWAIT Negated Detection in UPM Handled Cycles Timing

1

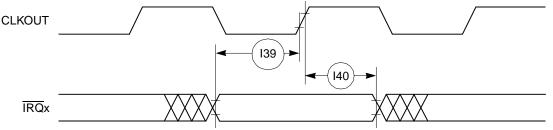

Table 11 provides the interrupt timing for the MPC875/MPC870.

| Table 11. Interrupt Timing |  |

|----------------------------|--|

|----------------------------|--|

| Num   | Characteristic <sup>1</sup>                   | All Freq                  | Unit |      |

|-------|-----------------------------------------------|---------------------------|------|------|

| Nulli | Characteristic                                | Min                       | Мах  | Unit |

| 139   | IRQx valid to CLKOUT rising edge (setup time) | 6.00                      |      | ns   |

| 140   | IRQx hold time after CLKOUT                   | 2.00                      |      | ns   |

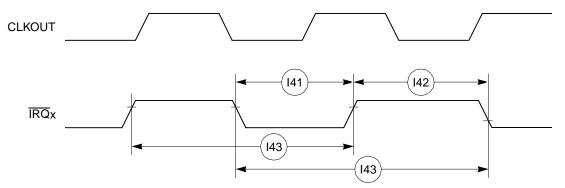

| 141   | IRQx pulse width low                          | 3.00                      |      | ns   |

| 142   | IRQx pulse width high                         | 3.00                      |      | ns   |

| 143   | IRQx edge-to-edge time                        | 4 × T <sub>CLOCKOUT</sub> |      | —    |

The I39 and I40 timings describe the testing conditions under which the IRQ lines are tested when being defined as level sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT. The I41, I42, and I43 timings are specified to allow correct functioning of the IRQ lines detection circuitry and have no direct relation with the total system interrupt latency that the MPC875/MPC870 is able to support.

Figure 25 provides the interrupt detection timing for the external level-sensitive lines.

Figure 25. Interrupt Detection Timing for External Level Sensitive Lines

Figure 26 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 26. Interrupt Detection Timing for External Edge-Sensitive Lines

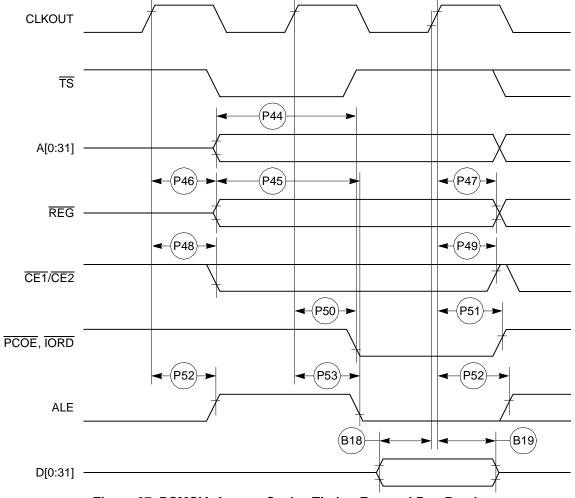

Figure 27 provides the PCMCIA access cycle timing for the external bus read.

Figure 27. PCMCIA Access Cycles Timing External Bus Read

Table 13 shows the PCMCIA port timing for the MPC875/MPC870.

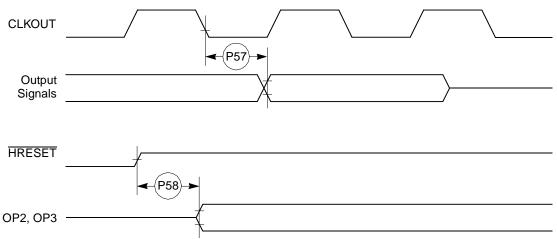

#### 33 MHz 40 MHz 66 MHz 80 MHz Num Characteristic Unit Min Max Min Max Min Max Min Max CLKOUT to OPx valid 19.00 19.00 19.00 19.00 \_\_\_\_ \_\_\_\_ \_\_\_\_ ns P57 $(MAX = 0.00 \times B1 + 19.00)$ HRESET negated to OPx drive<sup>1</sup> 25.70 21.70 14.40 12.40 ns \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ P58 $(MIN = 0.75 \times B1 + 3.00)$ IP\_Xx valid to CLKOUT rising edge 5.00 5.00 5.00 5.00 \_\_\_\_ \_\_\_\_ ns P59 $(MIN = 0.00 \times B1 + 5.00)$ CLKOUT rising edge to IP\_Xx invalid 1.00 1.00 1.00 1.00 ns \_\_\_\_ P60 $(MIN = 0.00 \times B1 + 1.00)$

#### Table 13. PCMCIA Port Timing

OP2 and OP3 only.

#### Figure 30 provides the PCMCIA output port timing for the MPC875/MPC870.

#### Figure 30. PCMCIA Output Port Timing

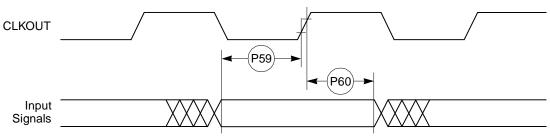

Figure 31 provides the PCMCIA input port timing for the MPC875/MPC870.

Figure 31. PCMCIA Input Port Timing

#### MPC875/MPC870 PowerQUICC™ Hardware Specifications, Rev. 4

**CPM Electrical Characteristics**

| Num | Characteristic                                                           | All Fre | Unit  |        |

|-----|--------------------------------------------------------------------------|---------|-------|--------|

| Num | Characteristic                                                           | Min     | Мах   | Unit   |

| 83a | L1RCLKB, L1TCLKB width high (DSC = $1$ ) <sup>3</sup>                    | P + 10  | _     | ns     |

| 84  | L1CLKB edge to L1CLKOB valid (DSC = 1)                                   | —       | 30.00 | ns     |

| 85  | L1RQB valid before falling edge of L1TSYNCB <sup>4</sup>                 | 1.00    | _     | L1TCLK |

| 86  | L1GRB setup time <sup>2</sup>                                            | 42.00   | _     | ns     |

| 87  | L1GRB hold time                                                          | 42.00   | _     | ns     |

| 88  | L1CLKB edge to L1SYNCB valid (FSD = 00) CNT = 0000, BYT = 0,<br>DSC = 0) | _       | 0.00  | ns     |

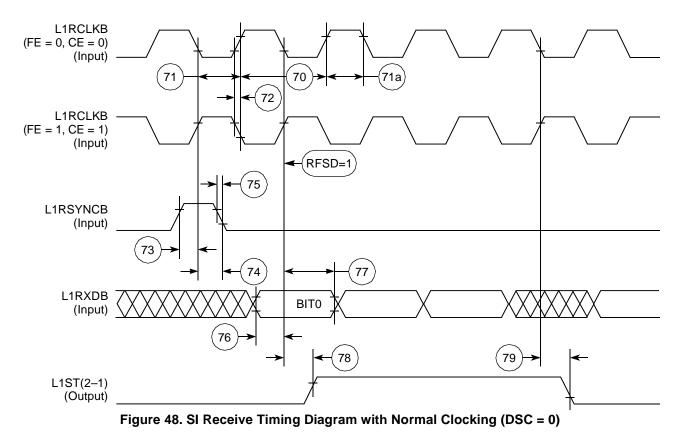

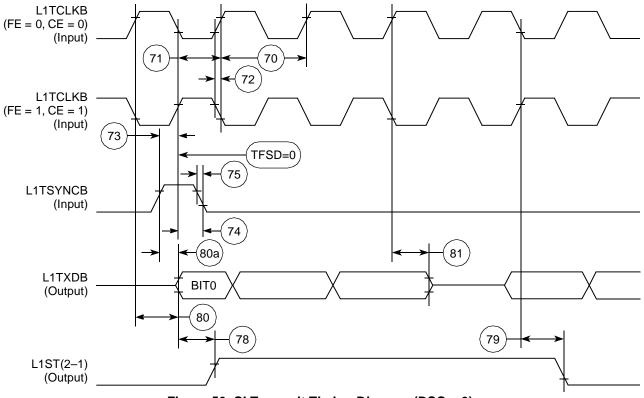

Table 21. SI Timing (continued)

<sup>1</sup> The ratio SYNCCLK/L1RCLKB must be greater than 2.5/1.

<sup>2</sup> These specs are valid for IDL mode only.

<sup>3</sup> Where P = 1/CLKOUT. Thus, for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after the L1CLKB edge or L1SYNCB, whichever comes later.

#### MPC875/MPC870 PowerQUICC<sup>™</sup> Hardware Specifications, Rev. 4

**CPM Electrical Characteristics**

MPC875/MPC870 PowerQUICC<sup>™</sup> Hardware Specifications, Rev. 4

**CPM Electrical Characteristics**

| Num | Characteristic            | All Freq | uencies | Unit |

|-----|---------------------------|----------|---------|------|

| Num | Gharacteristic            | Min      | Мах     | onit |

| 210 | SDL/SCL fall time         | _        | 300     | ns   |

| 211 | Stop condition setup time | 4.7      | _       | μs   |

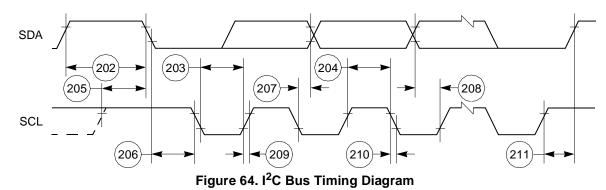

### Table 28. I<sup>2</sup>C Timing (SCL < 100 kHz) (continued)

SCL frequency is given by SCL = BRGCLK\_frequency/((BRG register + 3) × pre\_scalar × 2). The ratio SYNCCLK/(BRGCLK/pre\_scalar) must be greater than or equal to 4/1.

### Table 29 provides the $I^2C$ (SCL > 100 kHz) timings.

| Table 29. | I <sup>2</sup> C | Timing | (SCL | > | 100 | kHz) |

|-----------|------------------|--------|------|---|-----|------|

|-----------|------------------|--------|------|---|-----|------|

| Num   | Characteristic                            | Expression | All Freq        | Unit                        |      |

|-------|-------------------------------------------|------------|-----------------|-----------------------------|------|

| Nulli | Characteristic                            | Expression | Min             | Max                         | Unit |

| 200   | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48                   | Hz   |

| 200   | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48                   | Hz   |

| 202   | Bus free time between transmissions       | _          | 1/(2.2 × fSCL)  | _                           | S    |

| 203   | Low period of SCL                         | _          | 1/(2.2 × fSCL)  | _                           | S    |

| 204   | High period of SCL                        | _          | 1/(2.2 × fSCL)  | _                           | S    |

| 205   | Start condition setup time                | —          | 1/(2.2 × fSCL)  | —                           | S    |

| 206   | Start condition hold time                 | —          | 1/(2.2 × fSCL)  | —                           | S    |

| 207   | Data hold time                            | —          | 0               | —                           | S    |

| 208   | Data setup time                           | —          | 1/(40 × fSCL)   | —                           | S    |

| 209   | SDL/SCL rise time                         | —          | —               | 1/(10 × fSCL)               | S    |

| 210   | SDL/SCL fall time                         | —          | —               | $1/(33 \times \text{fSCL})$ | S    |

| 211   | Stop condition setup time                 | —          | 1/2(2.2 × fSCL) | _                           | S    |

SCL frequency is given by SCL = BRGCLK\_frequency/((BRG register + 3) × pre\_scalar × 2). The ratio SYNCCLK/(BRGCLK/pre\_scalar) must be greater than or equal to 4/1.

Figure 64 shows the  $I^2C$  bus timing.

#### **FEC Electrical Characteristics**

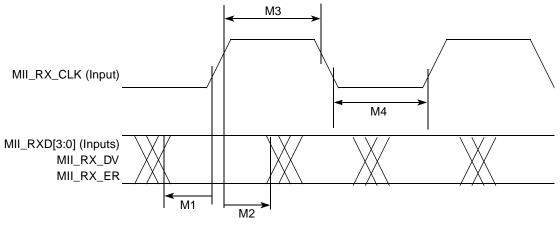

Figure 65 shows MII receive signal timing.

Figure 65. MII Receive Signal Timing Diagram

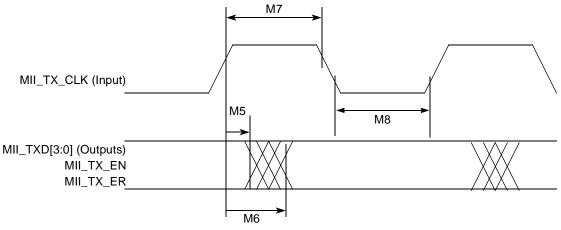

### 15.2 MII and Reduced MII Transmit Signal Timing

The transmitter functions correctly up to a MII\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_TX\_CLK frequency -1%.

Table 32 provides information on the MII transmit signal timing.

| Table 32. M | III Transmit | Signal Timing |

|-------------|--------------|---------------|

|-------------|--------------|---------------|

| Num      | Characteristic                                                   | Min | Max | Unit              |

|----------|------------------------------------------------------------------|-----|-----|-------------------|

| M5       | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER invalid         | 5   | _   | ns                |

| M6       | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER valid           |     | 25  | ns                |

| M7       | MII_TX_CLK pulse width high                                      | 35% | 65% | MII_TX_CLK period |

| M8       | MII_TX_CLK pulse width low                                       | 35% | 65% | MII_TX_CLK period |

| M20_RMII | RMII_TXD[1:0], RMII_TX_EN to RMII_REFCLK setup                   | 4   | _   | ns                |

| M21_RMII | RMII_TXD[1:0], RMII_TX_EN data hold from RMII_REFCLK rising edge | 2   | _   | ns                |

Figure 66 shows the MII transmit signal timing diagram.

Figure 66. MII Transmit Signal Timing Diagram

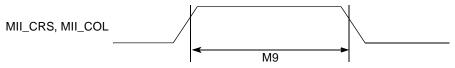

### 15.3 MII Async Inputs Signal Timing (MII\_CRS, MII\_COL)

Table 33 provides information on the MII async inputs signal timing.

#### Table 33. MII Async Inputs Signal Timing

| Nu | Characteristic                       | Min | Max | Unit              |

|----|--------------------------------------|-----|-----|-------------------|

| M  | MII_CRS, MII_COL minimum pulse width | 1.5 | —   | MII_TX_CLK period |

Figure 67 shows the MII asynchronous inputs signal timing diagram.

Figure 67. MII Async Inputs Timing Diagram

### 15.4 MII Serial Management Channel Timing (MII\_MDIO, MII\_MDC)

Table 34 provides information on the MII serial management channel signal timing. The FEC functions correctly with a maximum MDC frequency in excess of 2.5 MHz.

| Table 34. MII Serial Management Channel Tir | ning |

|---------------------------------------------|------|

|---------------------------------------------|------|

| Num | Characteristic                                                              | Min | Мах | Unit           |

|-----|-----------------------------------------------------------------------------|-----|-----|----------------|

| M10 | MII_MDC falling edge to MII_MDIO output invalid (minimum propagation delay) | 0   | —   | ns             |

| M11 | MII_MDC falling edge to MII_MDIO output valid (max prop delay)              | _   | 25  | ns             |

| M12 | MII_MDIO (input) to MII_MDC rising edge setup                               | 10  | —   | ns             |

| M13 | MII_MDIO (input) to MII_MDC rising edge hold                                | 0   | —   | ns             |

| M14 | MII_MDC pulse width high                                                    | 40% | 60% | MII_MDC period |

| M15 | MII_MDC pulse width low                                                     | 40% | 60% | MII_MDC period |

#### MPC875/MPC870 PowerQUICC™ Hardware Specifications, Rev. 4

| Name                                             | Pin Number | Туре                                    |

|--------------------------------------------------|------------|-----------------------------------------|

| PE29, MII2-CRS                                   | U7         | Bidirectional<br>(Optional: open-drain) |

| PE28, TOUT3, MII2-COL                            | R7         | Bidirectional<br>(Optional: open-drain) |

| PE27, L1RQB, MII2-RXERR,<br>RMII2-RXERR          | Т6         | Bidirectional<br>(Optional: open-drain) |

| PE26, L1CLKOB,<br>MII2-RXDV, RMII2-CRS_DV        | T2         | Bidirectional<br>(Optional: open-drain) |

| PE25, RXD4, MII2-RXD3,<br>L1ST2                  | R4         | Bidirectional<br>(Optional: open-drain) |

| PE24, SMRXD1, BRGO1,<br>MII2-RXD2                | U8         | Bidirectional<br>(Optional: open-drain) |

| PE23, TXD4, MII2-RXCLK,<br>L1ST1                 | U4         | Bidirectional<br>(Optional: open-drain) |

| PE22, TOUT2, MII2-RXD1,<br>RMII2-RXD1, SDACK1    | P4         | Bidirectional<br>(Optional: open-drain) |

| PE21, TOUT1, MII2-RXD0,<br>RMII2-RXD0            | Т9         | Bidirectional<br>(Optional: open-drain) |

| PE20, MII2-TXER                                  | U3         | Bidirectional<br>(Optional: open-drain) |

| PE19, L1TXDB, MII2-TXEN,<br>RMII2-TXEN           | R6         | Bidirectional<br>(Optional: open-drain) |

| PE18, SMTXD1, MII2-TXD3                          | M5         | Bidirectional<br>(Optional: open-drain) |

| PE17, TIN3, CLK5, BRGO3,<br>SMSYN1, MII2-TXD2    | Т8         | Bidirectional<br>(Optional: open-drain) |

| PE16, L1RCLKB, CLK6,<br>MII2-TXCLK, RMII2-REFCLK | U6         | Bidirectional<br>(Optional: open-drain) |

| PE15, TGATE1, MII2-TXD1,<br>RMII2-TXD1           | Т7         | Bidirectional                           |

| PE14, MII2-TXD0,<br>RMII2-TXD0                   | P8         | Bidirectional                           |

| TMS                                              | T14        | Input<br>(5-V tolerant)                 |

| TDI, DSDI                                        | T13        | Input<br>(5-V tolerant)                 |

| TCK, DSCK                                        | R13        | Input<br>(5-V tolerant)                 |

| TRST                                             | U14        | Input<br>(5-V tolerant)                 |

#### Table 36. Pin Assignments—JEDEC Standard (continued)

| Name                    | Pin Number                                                                               | Туре                            |

|-------------------------|------------------------------------------------------------------------------------------|---------------------------------|

| TDO, DSDO               | P13                                                                                      | Output<br>(5-V tolerant)        |

| MII1_CRS                | U10                                                                                      | Input                           |

| MII_MDIO                | M13                                                                                      | Bidirectional<br>(5-V tolerant) |

| MII1_TX_EN, RMII1_TX_EN | U5                                                                                       | Output<br>(5-V tolerant)        |

| MII1_COL                | R10                                                                                      | Input                           |

| V <sub>SSSYN</sub>      | E5                                                                                       | PLL analog GND                  |

| V <sub>SSSYN1</sub>     | F6                                                                                       | PLL analog GND                  |

| V <sub>DDSYN</sub>      | E6                                                                                       | PLL analog V <sub>DD</sub>      |

| GND                     | H8, H9, H10, H11, J8, J9, J10, J11, K8, K9, K10, K11, L8, L9, L10, L11, U15              | Power                           |

| V <sub>DDL</sub>        | F7, F8, F9, F10, F11, H6, H13, J6, J13, K6, K13, L6, L13, N7, N8, N9, N10, N11           | Power                           |

| V <sub>DDH</sub>        | G7, G8, G9, G10, G11, G12, H7, H12, J7, J12, K7, K12, L7, L12, M7, M8, M9, M10, M11, M12 | Power                           |

| N/C                     | B17, T16, U2, U17                                                                        | No connect                      |

#### Table 36. Pin Assignments—JEDEC Standard (continued)

| Revision<br>Number | Date                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.0                | 1/07/2004<br>7/19/2004 | <ul> <li>Added sentence to Spec B1A about EXTCLK and CLKOUT being in alignment for integer values.</li> <li>Added a footnote to Spec 41 specifying that EDM = 1.</li> <li>Added the thermal numbers to Table 4.</li> <li>Added RMII1_EN under M1II_EN in Table 36, Pin Assignments.</li> <li>Added a table footnote to Table 6, DC Electrical Specifications, about meeting the V<sub>IL</sub> Max of the I<sup>2</sup>C Standard.</li> <li>Put the new part numbers in the Ordering Information Section.</li> </ul>                                                                                   |

| 4                  | 08/2007                | <ul> <li>Updated template.</li> <li>On page 1, updated first paragraph and added a second paragraph.</li> <li>After Table 2, inserted a new figure showing the undershoot/overshoot voltage (Figure 3) and renumbered the rest of the figures.</li> <li>In Table 10, for reset timings B29f and B29g added footnote indicating that the formula only applies to bus operation up to 50 MHz.</li> <li>In Figure 5, changed all reference voltage measurement points from 0.2 and 0.8 V to 50% level.</li> <li>In Table 18, changed num 46 description to read, "TA assertion to rising edge"</li> </ul> |

**Document Revision History**

### THIS PAGE INTENTIONALLY LEFT BLANK