# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 133MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                   |

| RAM Controllers                 | DRAM                                                                  |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100Mbps (2)                                                        |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 (1)                                                           |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | -40°C ~ 100°C (TA)                                                    |

| Security Features               | -                                                                     |

| Package / Case                  | 256-BBGA                                                              |

| Supplier Device Package         | 256-PBGA (23x23)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc870czt133 |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Thirty-two address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to DRAM, SIMMS, SRAM, EPROMs, Flash EPROMs, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes–256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

- Two Fast Ethernet controllers (FEC)—Two 10/100 Mbps Ethernet/IEEE Std. 802.3® CDMA/CS that interface through MII and/or RMII interfaces

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Clock synthesizer

- Decrementer and time base

- Reset controller

- IEEE 1149.1<sup>™</sup> Std. test access port (JTAG)

- Security engine is optimized to handle all the algorithms associated with IPsec, SSL/TLS, SRTP, IEEE 802.11i® standard, and iSCSI processing. Available on the MPC875, the security engine contains a crypto-channel, a controller, and a set of crypto hardware accelerators (CHAs). The CHAs are:

- Data encryption standard execution unit (DEU)

- DES, 3DES

- Two key (K1, K2, K1) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rijndael symmetric key cipher

Features

- ECB, CBC, and counter modes

- 128-, 192-, and 256-bit key lengths

- Message digest execution unit (MDEU)

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Master/slave logic, with DMA

- 32-bit address/32-bit data

- Operation at MPC8xx bus frequency

- Crypto-channel supporting multi-command descriptors

- Integrated controller managing crypto-execution units

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Interrupts

- Six external interrupt request (IRQ) lines

- Twelve port pins with interrupt capability

- Twenty-three internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- 8-Kbytes of dual-port RAM

- Several serial DMA (SDMA) channels to support the CPM

- Three parallel I/O registers with open-drain capability

- On-chip  $16 \times 16$  multiply accumulate controller (MAC)

- One operation per clock (two-clock latency, one-clock blockage)

- MAC operates concurrently with other instructions

- FIR loop—Four clocks per four multiplies

- Four baud-rate generators

- Independent (can be connected to SCC or SMC)

- Allows changes during operation

- Autobaud support option

- SCC (serial communication controller)

- Ethernet/IEEE 802.3® standard, supporting full 10-Mbps operation

- HDLC/SDLC

NP

**Thermal Characteristics**

| Rating                              | Symbol              | Value | Unit |

|-------------------------------------|---------------------|-------|------|

| Temperature <sup>1</sup> (standard) | T <sub>A(min)</sub> | 0     | °C   |

|                                     | T <sub>J(max)</sub> | 95    | °C   |

| Temperature (extended)              | T <sub>A(min)</sub> | -40   | °C   |

|                                     | T <sub>J(max)</sub> | 100   | °C   |

| Table 3. Operating | Temperatures |

|--------------------|--------------|

|--------------------|--------------|

<sup>1</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>J</sub>.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DDH}$ ).

## 4 Thermal Characteristics

Table 4 shows the thermal characteristics for the MPC875/MPC870.

| Rating                               | E                                            | Environment             |                            |    | Unit |

|--------------------------------------|----------------------------------------------|-------------------------|----------------------------|----|------|

| Junction-to-ambient <sup>1</sup>     | Natural convection                           | Single-layer board (1s) | $R_{\theta JA}^2$          | 43 | °C/W |

|                                      |                                              | Four-layer board (2s2p) | $R_{\theta JMA}{}^3$       | 29 |      |

|                                      | Airflow (200 ft/min) Single-layer board (1s) |                         | $R_{\theta JMA}{}^3$       | 36 |      |

|                                      |                                              | Four-layer board (2s2p) | ${\sf R}_{\theta JMA}{}^3$ | 26 |      |

| Junction-to-board <sup>4</sup>       |                                              |                         | R <sub>θJB</sub>           | 20 |      |

| Junction-to-case <sup>5</sup>        |                                              |                         | R <sub>θJC</sub>           | 10 |      |

| Junction-to-package top <sup>6</sup> | Natural convection                           |                         | $\Psi_{JT}$                | 2  |      |

|                                      | Airflow (200 ft/min)                         |                         | $\Psi_{JT}$                | 2  |      |

Table 4. MPC875/MPC870 Thermal Resistance Data

<sup>1</sup> Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

- <sup>4</sup> Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated value from the junction to the exposed pad without contact resistance.

<sup>6</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

#### **Power Dissipation** 5

Table 5 provides information on power dissipation. The modes are 1:1, where CPU and bus speeds are equal, and 2:1, where CPU frequency is twice bus speed.

| Die Revision | Bus Mode | Frequency | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|--------------|----------|-----------|----------------------|----------------------|------|

| 0            | 1:1      | 66 MHz    | 310                  | 390                  | mW   |

|              |          | 80 MHz    | 350                  | 430                  | mW   |

|              | 2:1      | 133 MHz   | 430                  | 495                  | mW   |

### Table 5. Power Dissipation (P<sub>D</sub>)

<sup>1</sup> Typical power dissipation is measured at  $V_{DDL} = V_{DDSYN} = 1.8$  V, and  $V_{DDH}$  is at 3.3 V. <sup>2</sup> Maximum power dissipation at  $V_{DDL} = V_{DDSYN} = 1.9$  V, and  $V_{DDH}$  is at 3.5 V.

### NOTE

The values in Table 5 represent  $V_{DDL}$ -based power dissipation and do not include I/O power dissipation over  $V_{DDH}$ . I/O power dissipation varies widely by application due to buffer current, depending on external circuitry.

The V<sub>DDSYN</sub> power dissipation is negligible.

#### **DC Characteristics** 6

Table 6 provides the DC electrical characteristics for the MPC875/MPC870.

**Table 6. DC Electrical Specifications**

| Characteristic                                                                                                     | Symbol                                                           | Min                  | Мах              | Unit |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------|------------------|------|

| Operating voltage                                                                                                  | V <sub>DDH</sub> (I/O)                                           | 3.135                | 3.465            | V    |

|                                                                                                                    | V <sub>DDL</sub> (core)                                          | 1.7                  | 1.9              | V    |

|                                                                                                                    | V <sub>DDSYN</sub> 1                                             | 1.7                  | 1.9              | V    |

|                                                                                                                    | Difference<br>between V <sub>DDL</sub><br>and V <sub>DDSYN</sub> | _                    | 100              | mV   |

| Input high voltage (all inputs except EXTAL and EXTCLK) <sup>2</sup>                                               | V <sub>IH</sub>                                                  | 2.0                  | 3.465            | V    |

| Input low voltage <sup>3</sup>                                                                                     | V <sub>IL</sub>                                                  | GND                  | 0.8              | V    |

| EXTAL, EXTCLK input high voltage                                                                                   | V <sub>IHC</sub>                                                 | $0.7 \times V_{DDH}$ | V <sub>DDH</sub> | V    |

| Input leakage current, $V_{in}$ = 5.5 V (except TMS, TRST, DSCK, and DSDI pins) for 5-V tolerant pins <sup>1</sup> | l <sub>in</sub>                                                  | —                    | 100              | μA   |

| Input leakage current, $V_{in} = V_{DDH}$ (except TMS, TRST, DSCK, and DSDI)                                       | l <sub>in</sub>                                                  | —                    | 10               | μA   |

| Input leakage current, $V_{in} = 0 V$ (except TMS, TRST, DSCK, and DSDI pins)                                      | l <sub>in</sub>                                                  | _                    | 10               | μA   |

| Input capacitance <sup>4</sup>                                                                                     | C <sub>in</sub>                                                  | —                    | 20               | pF   |

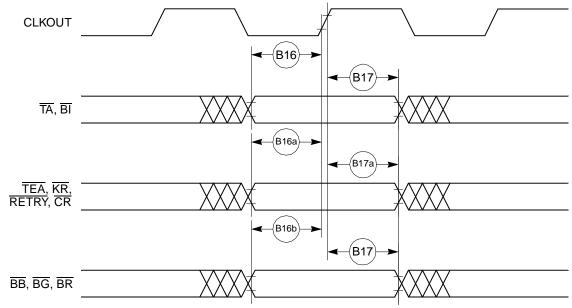

Figure 9 provides the timing for the synchronous input signals.

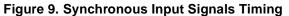

Figure 10 provides normal case timing for input data. It also applies to normal read accesses under the control of the user-programmable machine (UPM) in the memory controller.

Figure 10. Input Data Timing in Normal Case

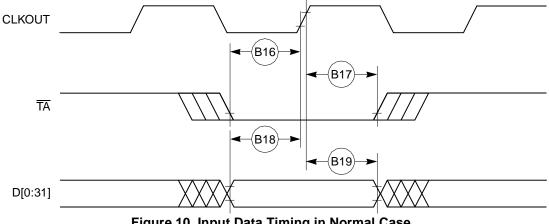

Figure 16 through Figure 18 provide the timing for the external bus write controlled by various GPCM factors.

```

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 0)

```

Bus Signal Timing

### Table 12 shows the PCMCIA timing for the MPC875/MPC870.

Table 12. PCMCIA Timing

| Num | Characteristic                                                                                                                                                   | 33 MHz 40 M |       | MHz   | MHz 66 MHz |       | 80 MHz |       | Unit  |      |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-------|------------|-------|--------|-------|-------|------|

| Num | Characteristic                                                                                                                                                   | Min         | Max   | Min   | Max        | Min   | Max    | Min   | Max   | Unit |

| P44 | A(0:31), $\overline{\text{REG}}$ valid to PCMCIA strobe<br>asserted <sup>1</sup> (MIN = 0.75 × B1 - 2.00)                                                        | 20.70       |       | 16.70 |            | 9.40  | _      | 7.40  |       | ns   |

| P45 | A(0:31), $\overline{\text{REG}}$ valid to ALE negation <sup>1</sup><br>(MIN = 1.00 × B1 - 2.00)                                                                  | 28.30       | _     | 23.00 |            | 13.20 | _      | 10.50 |       | ns   |

| P46 | CLKOUT to $\overline{\text{REG}}$ valid<br>(MAX = 0.25 × B1 + 8.00)                                                                                              | 7.60        | 15.60 | 6.30  | 14.30      | 3.80  | 11.80  | 3.13  | 11.13 | ns   |

| P47 | CLKOUT to $\overline{\text{REG}}$ invalid<br>(MIN = 0.25 × B1 + 1.00)                                                                                            | 8.60        |       | 7.30  | _          | 4.80  | _      | 4.125 | _     | ns   |

| P48 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ asserted<br>(MAX = 0.25 × B1 + 8.00)                                                                               | 7.60        | 15.60 | 6.30  | 14.30      | 3.80  | 11.80  | 3.13  | 11.13 | ns   |

| P49 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ negated<br>(MAX = 0.25 × B1 + 8.00)                                                                                | 7.60        | 15.60 | 6.30  | 14.30      | 3.80  | 11.80  | 3.13  | 11.13 | ns   |

| P50 | CLKOUT to $\overrightarrow{PCOE}$ , $\overrightarrow{IORD}$ , $\overrightarrow{PCWE}$ , $\overrightarrow{IOWR}$<br>assert time (MAX = $0.00 \times B1 + 11.00$ ) | —           | 11.00 | —     | 11.00      |       | 11.00  | _     | 11.00 | ns   |

| P51 | CLKOUT to $\overrightarrow{PCOE}$ , $\overrightarrow{IORD}$ , $\overrightarrow{PCWE}$ , $\overrightarrow{IOWR}$<br>negate time (MAX = 0.00 × B1 + 11.00)         | 2.00        | 11.00 | 2.00  | 11.00      | 2.00  | 11.00  | 2.00  | 11.00 | ns   |

| P52 | CLKOUT to ALE assert time $(MAX = 0.25 \times B1 + 6.30)$                                                                                                        | 7.60        | 13.80 | 6.30  | 12.50      | 3.80  | 10.00  | 3.13  | 9.40  | ns   |

| P53 | CLKOUT to ALE negate time<br>(MAX = 0.25 × B1 + 8.00)                                                                                                            | —           | 15.60 | —     | 14.30      |       | 11.80  | _     | 11.13 | ns   |

| P54 | $\frac{\overline{PCWE}, \overline{IOWR} \text{ negated to } D(0:31)}{invalid^1 (MIN = 0.25 \times B1 - 2.00)}$                                                   | 5.60        | _     | 4.30  | —          | 1.80  | —      | 1.125 | _     | ns   |

| P55 | $\overline{\text{WAITA}}$ and $\overline{\text{WAITB}}$ valid to CLKOUT rising edge <sup>1</sup> (MIN = 0.00 × B1 + 8.00)                                        | 8.00        |       | 8.00  | _          | 8.00  | —      | 8.00  | _     | ns   |

| P56 | CLKOUT rising edge to $\overline{WAITA}$ and $\overline{WAITB}$ invalid <sup>1</sup> (MIN = 0.00 × B1 + 2.00)                                                    | 2.00        | _     | 2.00  | _          | 2.00  | —      | 2.00  | _     | ns   |

<sup>1</sup> PSST = 1. Otherwise add PSST times cycle time.

PSHT = 0. Otherwise add PSHT times cycle time.

These synchronous timings define when the WAITA signals are detected in order to freeze (or relieve) the PCMCIA current cycle. The WAITA assertion will be effective only if it is detected 2 cycles before the PSL timer expiration. See Chapter 16, "PCMCIA Interface," in the MPC885 PowerQUICC<sup>™</sup> Family Reference Manual.

Table 13 shows the PCMCIA port timing for the MPC875/MPC870.

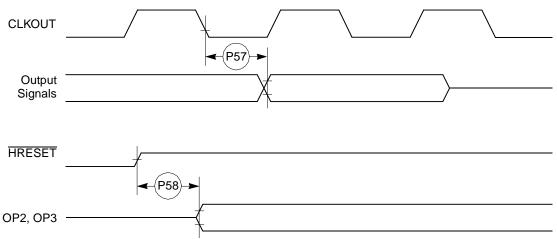

#### 33 MHz 40 MHz 66 MHz 80 MHz Num Characteristic Unit Min Max Min Max Min Max Min Max CLKOUT to OPx valid 19.00 19.00 19.00 19.00 \_\_\_\_ \_\_\_\_ \_\_\_\_ ns P57 $(MAX = 0.00 \times B1 + 19.00)$ HRESET negated to OPx drive1 25.70 21.70 14.40 12.40 ns \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ P58 $(MIN = 0.75 \times B1 + 3.00)$ IP\_Xx valid to CLKOUT rising edge 5.00 5.00 5.00 5.00 \_\_\_\_ \_\_\_\_ ns P59 $(MIN = 0.00 \times B1 + 5.00)$ CLKOUT rising edge to IP\_Xx invalid 1.00 1.00 1.00 1.00 ns \_\_\_\_ P60 $(MIN = 0.00 \times B1 + 1.00)$

### Table 13. PCMCIA Port Timing

OP2 and OP3 only.

### Figure 30 provides the PCMCIA output port timing for the MPC875/MPC870.

### Figure 30. PCMCIA Output Port Timing

Figure 31 provides the PCMCIA input port timing for the MPC875/MPC870.

Figure 31. PCMCIA Input Port Timing

**Bus Signal Timing**

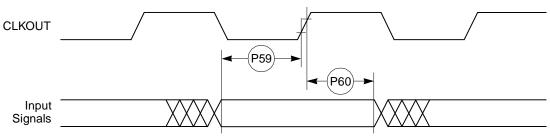

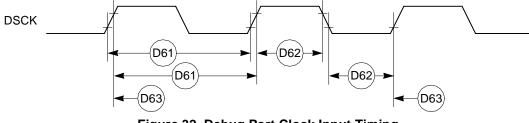

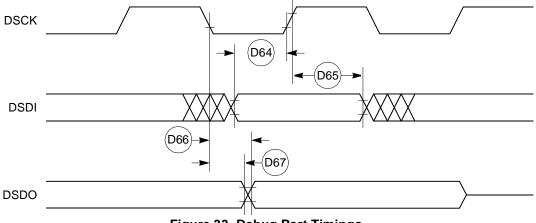

Table 14 shows the debug port timing for the MPC875/MPC870.

Table 14. Debug Port Timing

| Num | Characteristic              | All Frequ                 | Unit  |      |

|-----|-----------------------------|---------------------------|-------|------|

| Num | Cildiacteristic             | Min                       | Мах   | Unit |

| D61 | DSCK cycle time             | 3 × T <sub>CLOCKOUT</sub> |       | —    |

| D62 | DSCK clock pulse width      | $1.25 	imes T_{CLOCKOUT}$ |       | —    |

| D63 | DSCK rise and fall times    | 0.00                      | 3.00  | ns   |

| D64 | DSDI input data setup time  | 8.00                      |       | ns   |

| D65 | DSDI data hold time         | 5.00                      |       | ns   |

| D66 | DSCK low to DSDO data valid | 0.00                      | 15.00 | ns   |

| D67 | DSCK low to DSDO invalid    | 0.00                      | 2.00  | ns   |

Figure 32 provides the input timing for the debug port clock.

Figure 32. Debug Port Clock Input Timing

Figure 33 provides the timing for the debug port.

Figure 33. Debug Port Timings

**Bus Signal Timing**

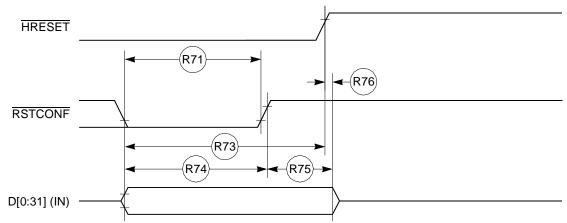

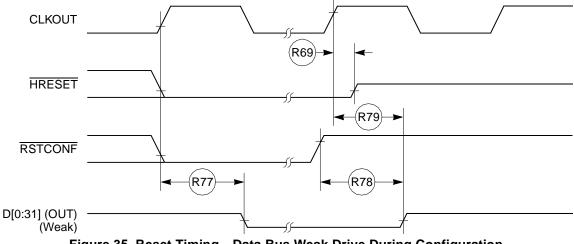

Figure 34 shows the reset timing for the data bus configuration.

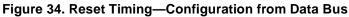

Figure 35 provides the reset timing for the data bus weak drive during configuration.

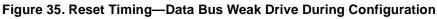

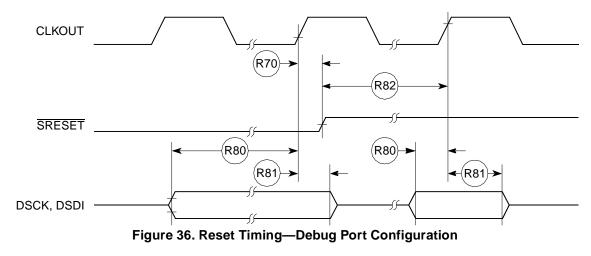

Figure 36 provides the reset timing for the debug port configuration.

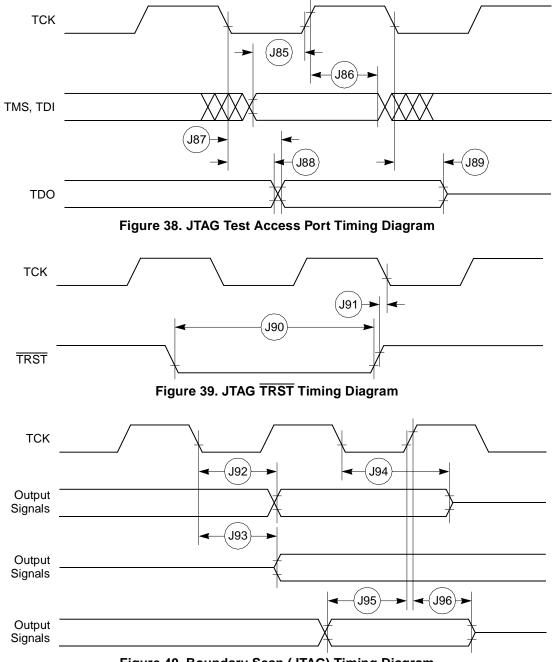

**IEEE 1149.1 Electrical Specifications**

Figure 40. Boundary Scan (JTAG) Timing Diagram

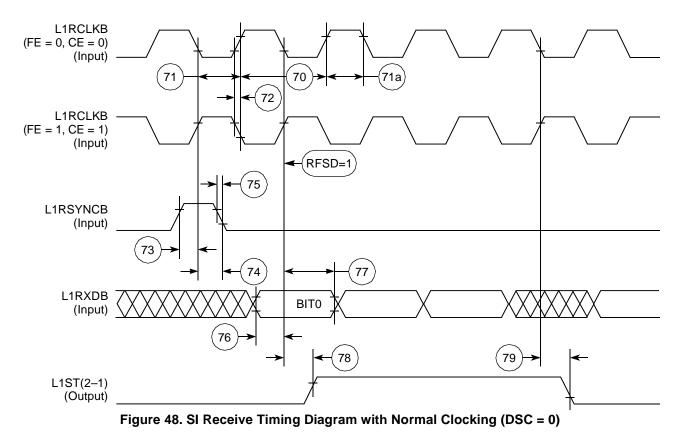

### **13 CPM Electrical Characteristics**

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC875/MPC870.

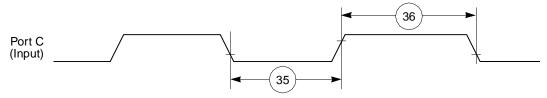

### **13.1 Port C Interrupt AC Electrical Specifications**

Table 17 provides the timings for Port C interrupts.

| Table | 17. | Port C | Interrupt | Timing |

|-------|-----|--------|-----------|--------|

|-------|-----|--------|-----------|--------|

| Num | Characteristic                                         | 33.34 MHz |     | Unit |  |

|-----|--------------------------------------------------------|-----------|-----|------|--|

| Num |                                                        | Min       | Мах | onn  |  |

| 35  | Port C interrupt pulse width low (edge-triggered mode) | 55        | _   | ns   |  |

| 36  | Port C interrupt minimum time between active edges     | 55        | _   | ns   |  |

Figure 41 shows the Port C interrupt detection timing.

Figure 41. Port C Interrupt Detection Timing

### **13.2 IDMA Controller AC Electrical Specifications**

Table 18 provides the IDMA controller timings as shown in Figure 42 through Figure 45.

### Table 18. IDMA Controller Timing

| Num | Characteristic                                                                                          |     | All Frequencies |      |  |

|-----|---------------------------------------------------------------------------------------------------------|-----|-----------------|------|--|

| num | Characteristic                                                                                          | Min | Мах             | Unit |  |

| 40  | DREQ setup time to clock high                                                                           | 7   | —               | ns   |  |

| 41  | DREQ hold time from clock high <sup>1</sup>                                                             | TBD | —               | ns   |  |

| 42  | SDACK assertion delay from clock high                                                                   | _   | 12              | ns   |  |

| 43  | SDACK negation delay from clock low                                                                     | _   | 12              | ns   |  |

| 44  | SDACK negation delay from TA low                                                                        | _   | 20              | ns   |  |

| 45  | SDACK negation delay from clock high                                                                    | _   | 15              | ns   |  |

| 46  | $\overline{TA}$ assertion to rising edge of the clock setup time (applies to external $\overline{TA}$ ) | 7   | —               | ns   |  |

<sup>1</sup> Applies to high-to-low mode (EDM = 1).

Figure 43. SDACK Timing Diagram—Peripheral Write, Externally-Generated TA

| Num | Characteristic                                                           | All Fre | Unit  |        |

|-----|--------------------------------------------------------------------------|---------|-------|--------|

| Num | Characteristic                                                           | Min     | Мах   | Unit   |

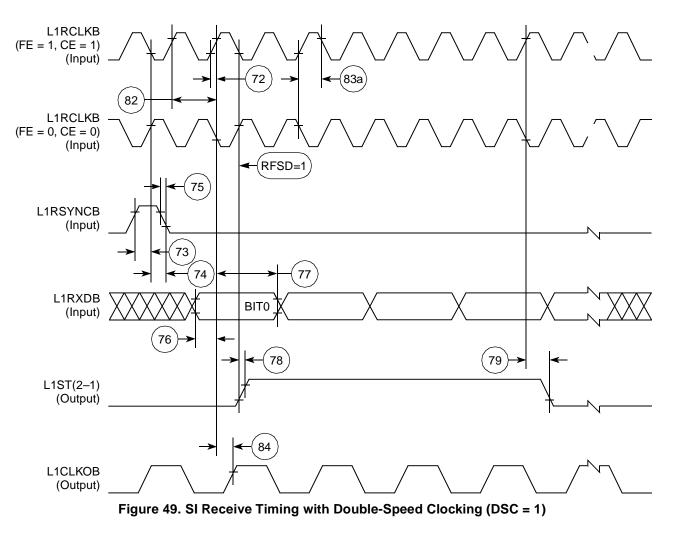

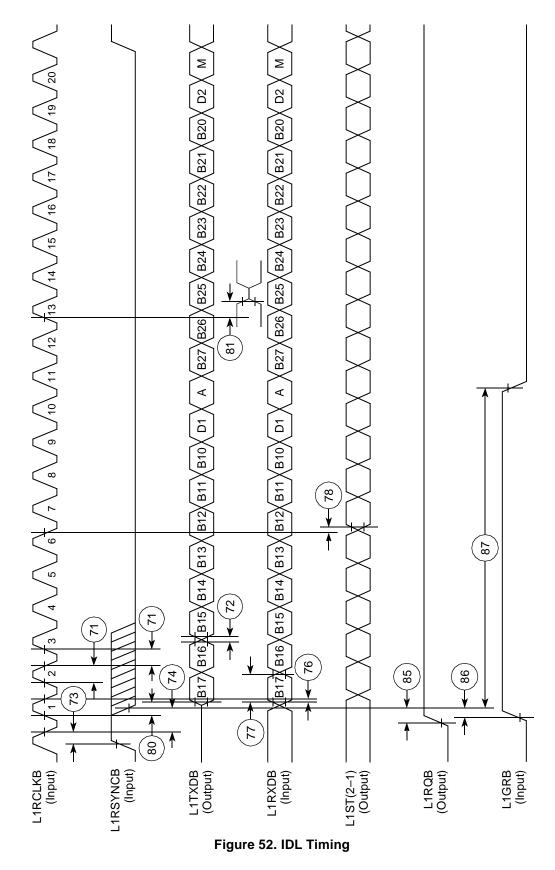

| 83a | L1RCLKB, L1TCLKB width high (DSC = $1$ ) <sup>3</sup>                    | P + 10  | _     | ns     |

| 84  | L1CLKB edge to L1CLKOB valid (DSC = 1)                                   | —       | 30.00 | ns     |

| 85  | L1RQB valid before falling edge of L1TSYNCB <sup>4</sup>                 | 1.00    | _     | L1TCLK |

| 86  | L1GRB setup time <sup>2</sup>                                            | 42.00   | _     | ns     |

| 87  | L1GRB hold time                                                          | 42.00   | _     | ns     |

| 88  | L1CLKB edge to L1SYNCB valid (FSD = 00) CNT = 0000, BYT = 0,<br>DSC = 0) | _       | 0.00  | ns     |

Table 21. SI Timing (continued)

<sup>1</sup> The ratio SYNCCLK/L1RCLKB must be greater than 2.5/1.

<sup>2</sup> These specs are valid for IDL mode only.

<sup>3</sup> Where P = 1/CLKOUT. Thus, for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after the L1CLKB edge or L1SYNCB, whichever comes later.

**CPM Electrical Characteristics**

## 13.11 I<sup>2</sup>C AC Electrical Specifications

Table 28 provides the  $I^2C$  (SCL < 100 kHz) timings.

| Table 28 | . I <sup>2</sup> C Timin | g (SCL < 100 | ) kHz) |

|----------|--------------------------|--------------|--------|

|----------|--------------------------|--------------|--------|

| Num | Characteristic                            | All Frequencies |     | Unit |

|-----|-------------------------------------------|-----------------|-----|------|

|     | Characteristic                            |                 | Мах |      |

| 200 | SCL clock frequency (slave)               | 0               | 100 | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5             | 100 | kHz  |

| 202 | Bus free time between transmissions       | 4.7             | —   | μs   |

| 203 | Low period of SCL                         | 4.7             | —   | μs   |

| 204 | High period of SCL                        | 4.0             | —   | μs   |

| 205 | Start condition setup time                | 4.7             | —   | μs   |

| 206 | Start condition hold time                 | 4.0             | _   | μs   |

| 207 | Data hold time                            | 0               | _   | μs   |

| 208 | Data setup time                           | 250             | _   | ns   |

| 209 | SDL/SCL rise time                         | _               | 1   | μs   |

### 14 USB Electrical Characteristics

This section provides the AC timings for the USB interface.

### 14.1 USB Interface AC Timing Specifications

The USB Port uses the transmit clock on SCC1. Table 30 lists the USB interface timings.

### Table 30. USB Interface AC Timing Specifications

| Name | Characteristic                                                        |         | All Frequencies |      |

|------|-----------------------------------------------------------------------|---------|-----------------|------|

| Name |                                                                       |         | Max             | Unit |

| US1  | USBCLK frequency of operation <sup>1</sup><br>Low speed<br>Full speed | 6<br>48 |                 | MHz  |

| US4  | USBCLK duty cycle (measured at 1.5 V)                                 | 45      | 55              | %    |

<sup>1</sup> USBCLK accuracy should be ±500 ppm or better. USBCLK may be stopped to conserve power.

## **15 FEC Electrical Characteristics**

This section provides the AC electrical specifications for the Fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 or 3.3 V.

### 15.1 MII and Reduced MII Receive Signal Timing

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25 MHz + 1%. The reduced MII (RMII) receiver functions correctly up to a RMII\_REFCLK maximum frequency of 50 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency -1%.

Table 31 provides information on the MII receive signal timing.

| Num     | Characteristic                                                 | Min | Мах | Unit              |

|---------|----------------------------------------------------------------|-----|-----|-------------------|

| M1      | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup         | 5   | _   | ns                |

| M2      | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold          | 5   | _   | ns                |

| M3      | MII_RX_CLK pulse width high                                    | 35% | 65% | MII_RX_CLK period |

| M4      | MII_RX_CLK pulse width low                                     | 35% | 65% | MII_RX_CLK period |

| M1_RMII | RMII_RXD[1:0], RMII_CRS_DV, RMII_RX_ERR to RMII_REFCLK setup   | 4   | _   | ns                |

| M2_RMII | RMII_REFCLK to RMII_RXD[1:0], RMII_CRS_DV, RMII_RX_ERR<br>hold | 2   |     | ns                |

Table 31. MII Receive Signal Timing

### **16.1 Pin Assignments**

Figure 69 shows the JEDEC pinout of the PBGA package as viewed from the top surface. For additional information, see the *MPC885 PowerQUICC Family User's Manual*.

### NOTE

The pin numbering starts with B2 in order to conform to the JEDEC standard for 23-mm body size using a  $16 \times 16$  array.

2 7 8 9 10 11 12 13 14 3 4 5 6 15 16 17 O O O O EXTCLK MODCK1  $\bigcup_{\mathsf{ALEA}}$ O  $\bigcirc$ CS3 O N/C в Ο O OP0  $O_{\overline{CS5}}$ MODCK2  $\bigcirc_{\overline{BB}}$  $\bigcup_{\overline{TS}}$  $\bigcup_{\overline{TA}}$  $O_{CS2}$ С  $\bigcirc$  $\cap$ О  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ CE1A RSTCONF SRESET BADDR29 OP1 ALEB IRQ2 BDIP GPLAB3 GPLA0 IPA7 D  $\bigcirc$  $\bigcirc$ Ο IPA2 WAITA PORESET XTAL EXTAL BADDR30 IPB1 BG GPLA4 GPLA5  $\overline{\mathsf{WR}}$ CE2A CS7 WE2 WE1 IPA4 Е Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$ О Ο Ο Ο Ο Ο HRESET BADDR28 IRQ4 CS1 GPLB4 CS4 GPLAB2 BSA1 BSA2 **IRQ3 WEO** D31 IPA5 IPA3 VSSSYN VDDSYN F Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $O_{CS6}$ Ο Ο O  $\bigcirc$ O Ο  $\bigcirc$  $\bigcirc$  $\odot$ Ο Ο BSAO BSA3 D30 IPA6 IPA1 VSSSYN VDDL VDDL OE TSIZ0 A31 D29 G  $\bigcirc$ Ο Ο  $\bigcirc$ Ο  $\bigcirc$ O VDDH  $\bigcirc$  $\bigcirc$ O VDDH  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$ Ο Ο D28 CLKOUT IPA0 WE3 TSI71 A22 D7 D26 A26 A18 н Ο Ο Ο Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$ Ο  $\bigcirc$ Ο Ο D22 D6 D24 D25 VDDL VDDH GND VDDH VDDL A28 A30 A25 A24 O D20 O D21 () A20 O A29 J Ο  $\bigcirc$  $\bigcirc$ Ο Ο  $\bigcirc$  $\bigcirc$ O A23 O A21 Ο Ο  $\bigcirc$ D19 D18 GND Κ Ο Ο Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο Ο Ο 0 Ο Ο  $\bigcirc$  $\bigcirc$ D15 D16 D14 VDDL GND VDDL D5 A14 A19 A27 A17 O D2 () A12 L  $\bigcirc$ Ο 0  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο D27 D0 A15 A10 A16 D3 O VDDH () A8 Μ  $\bigcirc$ Ο Ο Ο 0  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ 0  $\bigcirc$  $\bigcirc$ Ο A11 **IRQ0** MII\_MDIO A2 A13 D11 D9 D12 PE18 0 0  $\bigcirc$ 0  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$ 0 Ν  $\bigcirc$ 0 Ο  $\bigcirc$ Ο  $\bigcirc$ D13 IRQ7 PA2 VDDL VDDL PB26 PB27 A1 A6 A7 D10 D1 A9  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$ Р Ο  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$ PE14 PE31 D23 D17 PE22 PA0 PA4 PC6 PA6 PC11 TDO PA15 A3 Α5 R О O Ο Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ O PB28 O PC15  $\bigcirc_{A0}$  $\bigcirc$ PE19 PE28 PE30 PA11 MII\_COL PA7 PA10 тск PB29 PE25 PA3 D4 D8  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ т  $\bigcirc$ Ο  $\bigcirc$ PD8 PB31 PE27 PE17 PE21 PC7 PB19 PC12 N/C PB30 PE26 PA1 PE15 PB24 TDI TMS U O PE20 O PE23 MII-TX-EN PE16 O PE29 O PE24 O PC13 O MII-CRS O PC10 O PB23 O PB25 O PA14 O N/C

**NOTE:** This is the top view of the device.

Figure 69. Pinout of the PBGA Package—JEDEC Standard

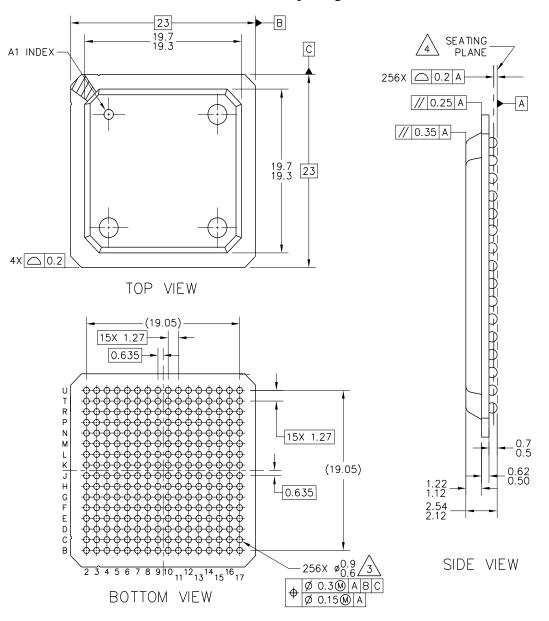

### 16.2 Mechanical Dimensions of the PBGA Package

Figure 70 shows the mechanical dimensions of the PBGA package.

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

- 4. DATUM A, THE SEATING PLANE, IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

- **Note:** Solder sphere composition is 95.5%Sn 45%Ag 0.5%Cu for MPC875/MPC870VRXXX. Solder sphere composition is 62%Sn 36%Pb 2%Ag for MPC875/MPC870ZTXXX.

### Figure 70. Mechanical Dimensions and Bottom Surface Nomenclature of the PBGA Package