# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                            |

|---------------------------------|---------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                      |

| Speed                           | 80MHz                                                               |

| Co-Processors/DSP               | Communications; CPM, Security; SEC                                  |

| RAM Controllers                 | DRAM                                                                |

| Graphics Acceleration           | No                                                                  |

| Display & Interface Controllers | -                                                                   |

| Ethernet                        | 10Mbps (1), 10/100Mbps (2)                                          |

| SATA                            | -                                                                   |

| USB                             | USB 2.0 (1)                                                         |

| Voltage - I/O                   | 3.3V                                                                |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                     |

| Security Features               | Cryptography                                                        |

| Package / Case                  | 256-BBGA                                                            |

| Supplier Device Package         | 256-PBGA (23x23)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc875vr80 |

|                                 |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Thirty-two address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to DRAM, SIMMS, SRAM, EPROMs, Flash EPROMs, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes–256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

- Two Fast Ethernet controllers (FEC)—Two 10/100 Mbps Ethernet/IEEE Std. 802.3® CDMA/CS that interface through MII and/or RMII interfaces

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Clock synthesizer

- Decrementer and time base

- Reset controller

- IEEE 1149.1<sup>™</sup> Std. test access port (JTAG)

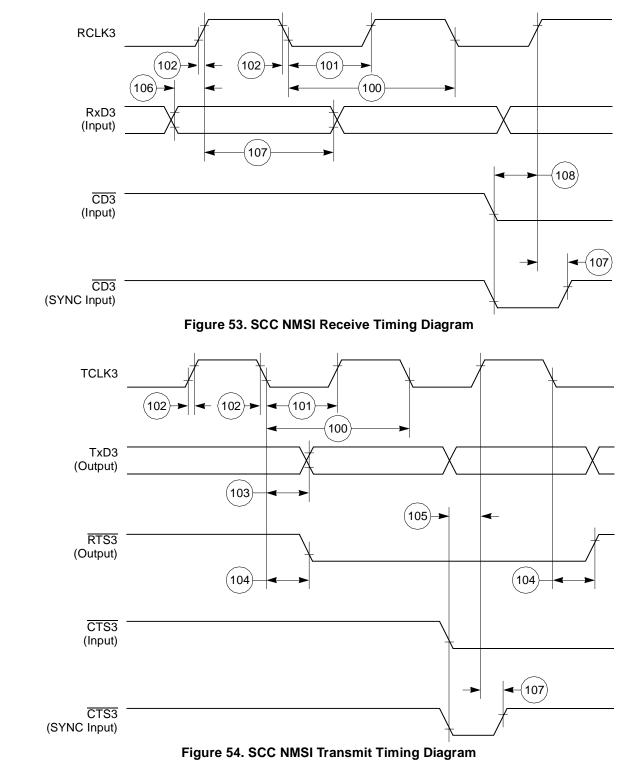

- Security engine is optimized to handle all the algorithms associated with IPsec, SSL/TLS, SRTP, IEEE 802.11i® standard, and iSCSI processing. Available on the MPC875, the security engine contains a crypto-channel, a controller, and a set of crypto hardware accelerators (CHAs). The CHAs are:

- Data encryption standard execution unit (DEU)

- DES, 3DES

- Two key (K1, K2, K1) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rijndael symmetric key cipher

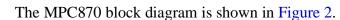

Figure 2. MPC870 Block Diagram

## 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC875/MPC870. Table 2 displays the maximum tolerated ratings and Table 3 displays the operating temperatures.

| Rating                      | Symbol                                       | Value                                                                                | Unit |

|-----------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|------|

| Supply voltage <sup>1</sup> | V <sub>DDL</sub> (core voltage)              | -0.3 to 3.4                                                                          | V    |

|                             | V <sub>DDH</sub> (I/O voltage)               | -0.3 to 4                                                                            | V    |

|                             | V <sub>DDSYN</sub>                           | -0.3 to 3.4                                                                          | V    |

|                             | Difference between $V_{DDL}$ and $V_{DDSYN}$ | <100                                                                                 | mV   |

| Input voltage <sup>2</sup>  | V <sub>in</sub>                              | $\ensuremath{GND}\xspace - 0.3$ to $\ensuremath{V}\xspace_{\ensuremath{DDH}\xspace}$ | V    |

| Storage temperature range   | T <sub>stg</sub>                             | –55 to +150                                                                          | °C   |

#### Table 2. Maximum Tolerated Ratings

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than V<sub>DDH</sub>. This restriction applies to power up and normal operation (that is, if the MPC875/MPC870 is unpowered, a voltage greater than 2.5 V must not be applied to its inputs).

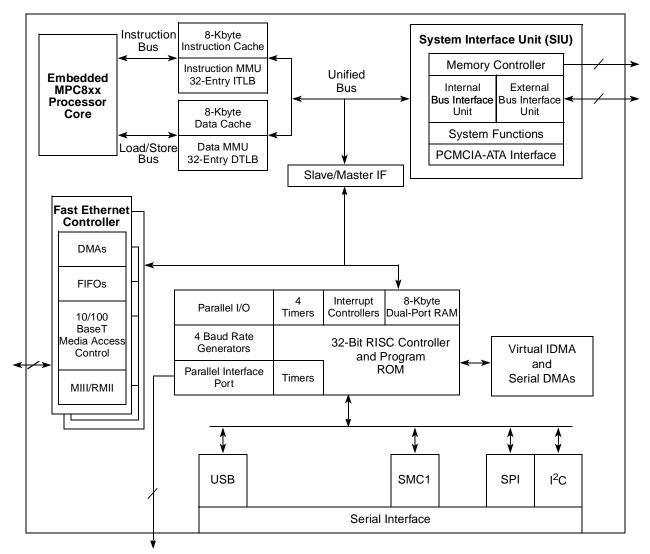

Figure 3 shows the undershoot and overshoot voltages at the interfaces of the MPC875/MPC870.

Figure 3. Undershoot/Overshoot Voltage for  $V_{\text{DDH}}$  and  $V_{\text{DDL}}$

| Nivers | Characteristic                                                                                                                                                                   | 33 MHz |       | 40 MHz |       | 66 MHz |       | 80 MHz |       | l lmi4 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|--------|

| Num    | Characteristic –                                                                                                                                                                 |        | Max   | Min    | Мах   | Min    | Max   | Min    | Мах   | Unit   |

| B15    | CLKOUT to $\overline{\text{TEA}}$ High-Z<br>(MIN = 0.00 × B1 + 2.50)                                                                                                             | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | ns     |

| B16    | TA, $\overline{BI}$ valid to CLKOUT (setup time)<br>(MIN = 0.00 × B1 + 6.00)                                                                                                     | 6.00   |       | 6.00   | —     | 6.00   | —     | 6      | —     | ns     |

| B16a   | TEA, $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid to CLKOUT (setup time) (MIN = 0.00 × B1 + 4.5)                                            | 4.50   | —     | 4.50   | —     | 4.50   | —     | 4.50   | —     | ns     |

| B16b   | $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ , valid to CLKOUT (setup time) <sup>2</sup><br>(4MIN = 0.00 × B1 + 0.00)                                                     | 4.00   | —     | 4.00   | —     | 4.00   | —     | 4.00   | —     | ns     |

| B17    | CLKOUT to $\overline{TA}$ , $\overline{TEA}$ , $\overline{BI}$ , $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ valid<br>(hold time) (MIN = 0.00 × B1 + 1.00 <sup>3</sup> ) | 1.00   | —     | 1.00   | —     | 2.00   | —     | 2.00   | —     | ns     |

| B17a   | CLKOUT to $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid (hold time)<br>(MIN = 0.00 × B1 + 2.00)                                              | 2.00   | —     | 2.00   | —     | 2.00   | —     | 2.00   | —     | ns     |

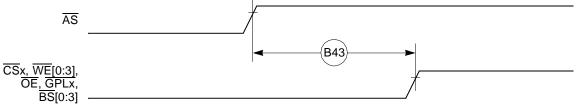

| B18    | D(0:31) valid to CLKOUT rising edge (setup time) <sup>4</sup> (MIN = $0.00 \times B1 + 6.00$ )                                                                                   | 6.00   | —     | 6.00   | —     | 6.00   | —     | 6.00   | —     | ns     |

| B19    | CLKOUT rising edge to D(0:31) valid (hold time) <sup>4</sup> (MIN = $0.00 \times B1 + 1.00^5$ )                                                                                  | 1.00   |       | 1.00   | _     | 2.00   | _     | 2.00   | —     | ns     |

| B20    | D(0:31) valid to CLKOUT falling edge (setup time) <sup>6</sup> (MIN = $0.00 \times B1 + 4.00$ )                                                                                  | 4.00   | _     | 4.00   | —     | 4.00   | _     | 4.00   | —     | ns     |

| B21    | CLKOUT falling edge to D(0:31) valid (hold time) <sup>6</sup> (MIN = $0.00 \times B1 + 2.00$ )                                                                                   | 2.00   | _     | 2.00   | —     | 2.00   | —     | 2.00   | —     | ns     |

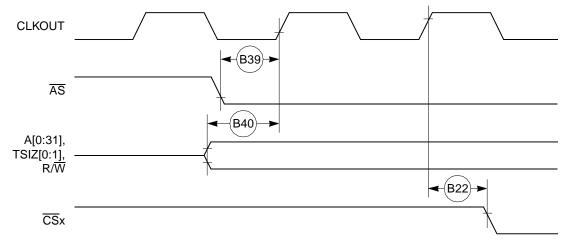

| B22    | CLKOUT rising edge to $\overline{CS}$ asserted GPCM<br>ACS = 00 (MAX = 0.25 × B1 + 6.3)                                                                                          | 7.60   | 13.80 | 6.30   | 12.50 | 3.80   | 10.00 | 3.13   | 9.43  | ns     |

| B22a   | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 10, TRLX = 0 (MAX = 0.00 × B1 + 8.00)                                                                              | _      | 8.00  | —      | 8.00  |        | 8.00  | —      | 8.00  | ns     |

| B22b   | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = 0, EBDF = 0<br>(MAX = 0.25 × B1 + 6.3)                                                                  | 7.60   | 13.80 | 6.30   | 12.50 | 3.80   | 10.00 | 3.13   | 9.43  | ns     |

| B22c   | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = 0, EBDF = 1<br>(MAX = 0.375 × B1 + 6.6)                                                                 | 10.90  | 18.00 | 10.90  | 16.00 | 5.20   | 12.30 | 4.69   | 10.93 | ns     |

| B23    | CLKOUT rising edge to $\overline{CS}$ negated GPCM<br>read access, GPCM write access ACS = 00,<br>TRLX = 0 and CSNT = 0<br>(MAX = 0.00 × B1 + 8.00)                              | 2.00   | 8.00  | 2.00   | 8.00  | 2.00   | 8.00  | 2.00   | 8.00  | ns     |

| B24    | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 0<br>(MIN = $0.25 \times B1 - 2.00$ )                                                              | 5.60   | _     | 4.30   | —     | 1.80   | —     | 1.13   | —     | ns     |

| B24a   | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 11, TRLX = 0<br>(MIN = 0.50 × B1 – 2.00)                                                                      | 13.20  |       | 10.50  | _     | 5.60   | _     | 4.25   | _     | ns     |

#### Table 10. Bus Operation Timings (continued)

**Bus Signal Timing**

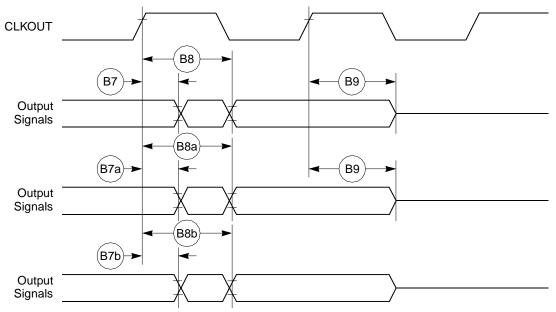

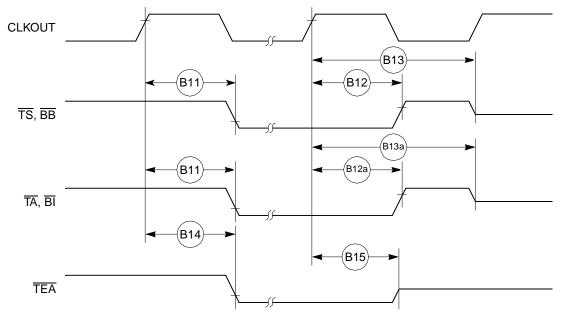

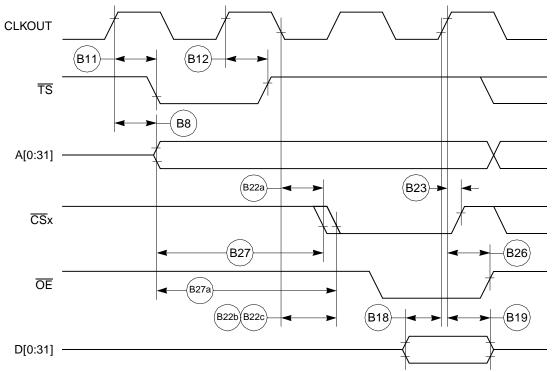

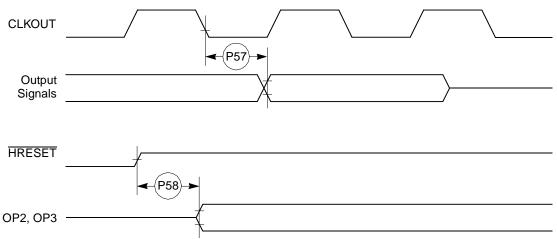

Figure 7 provides the timing for the synchronous output signals.

Figure 7. Synchronous Output Signals Timing

Figure 8 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 8. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

**Bus Signal Timing**

Figure 15. External Bus Read Timing (GPCM Controlled—TRLX = 1, ACS = 10, ACS = 11)

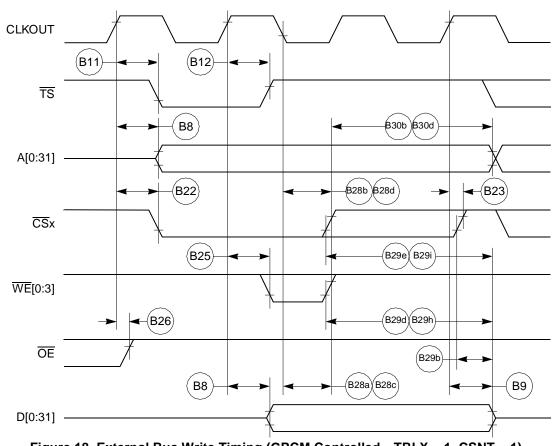

Figure 18. External Bus Write Timing (GPCM Controlled—TRLX = 1, CSNT = 1)

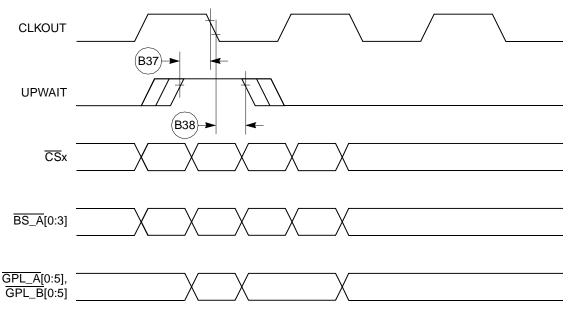

Figure 20 provides the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Figure 20. Asynchronous UPWAIT Asserted Detection in UPM Handled Cycles Timing

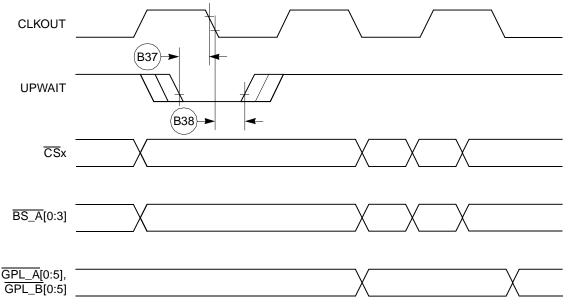

Figure 21 provides the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

Figure 21. Asynchronous UPWAIT Negated Detection in UPM Handled Cycles Timing

**Bus Signal Timing**

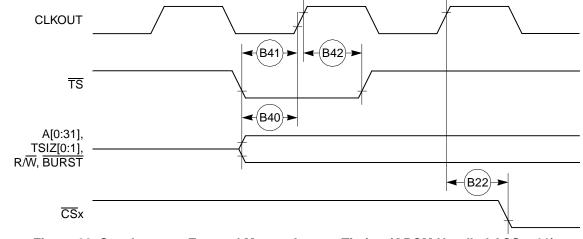

Figure 22 provides the timing for the synchronous external master access controlled by the GPCM.

Figure 22. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

Figure 23 provides the timing for the asynchronous external master memory access controlled by the GPCM.

Figure 24 provides the timing for the asynchronous external master control signals negation.

Figure 24. Asynchronous External Master—Control Signals Negation Timing

Figure 27 provides the PCMCIA access cycle timing for the external bus read.

Figure 27. PCMCIA Access Cycles Timing External Bus Read

Table 13 shows the PCMCIA port timing for the MPC875/MPC870.

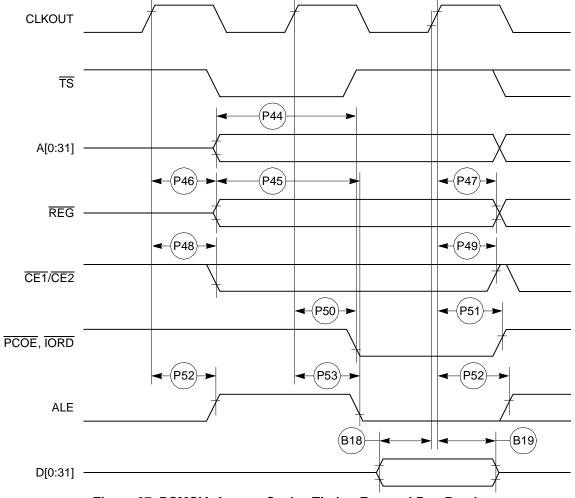

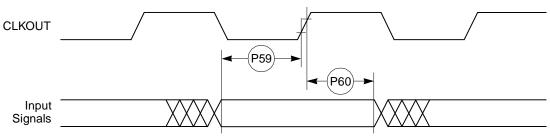

#### 33 MHz 40 MHz 66 MHz 80 MHz Num Characteristic Unit Min Max Min Max Min Max Min Max CLKOUT to OPx valid 19.00 19.00 19.00 19.00 \_\_\_\_ \_\_\_\_ \_\_\_\_ ns P57 $(MAX = 0.00 \times B1 + 19.00)$ HRESET negated to OPx drive<sup>1</sup> 25.70 21.70 14.40 12.40 ns \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ P58 $(MIN = 0.75 \times B1 + 3.00)$ IP\_Xx valid to CLKOUT rising edge 5.00 5.00 5.00 5.00 \_\_\_\_ \_\_\_\_ ns P59 $(MIN = 0.00 \times B1 + 5.00)$ CLKOUT rising edge to IP\_Xx invalid 1.00 1.00 1.00 1.00 ns \_\_\_\_ P60 $(MIN = 0.00 \times B1 + 1.00)$

#### Table 13. PCMCIA Port Timing

OP2 and OP3 only.

#### Figure 30 provides the PCMCIA output port timing for the MPC875/MPC870.

#### Figure 30. PCMCIA Output Port Timing

Figure 31 provides the PCMCIA input port timing for the MPC875/MPC870.

Figure 31. PCMCIA Input Port Timing

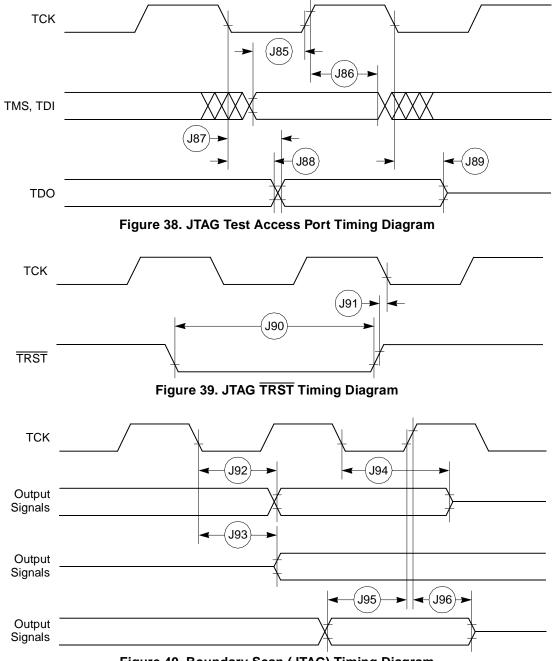

**IEEE 1149.1 Electrical Specifications**

Figure 40. Boundary Scan (JTAG) Timing Diagram

**CPM Electrical Characteristics**

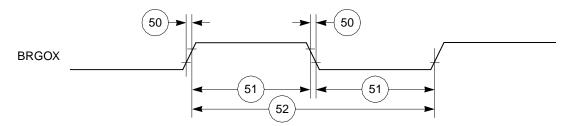

### **13.3 Baud Rate Generator AC Electrical Specifications**

Table 19 provides the baud rate generator timings as shown in Figure 46.

#### Table 19. Baud Rate Generator Timing

| Num | Characteristic          | All Freq | Unit |      |

|-----|-------------------------|----------|------|------|

| Num | Characteristic          | Min      | Мах  | Onit |

| 50  | BRGO rise and fall time | _        | 10   | ns   |

| 51  | BRGO duty cycle         | 40       | 60   | %    |

| 52  | BRGO cycle              | 40       | _    | ns   |

Figure 46. Baud Rate Generator Timing Diagram

### **13.4 Timer AC Electrical Specifications**

Table 20 provides the general-purpose timer timings as shown in Figure 47.

| Table | 20. | Timer | Timing |

|-------|-----|-------|--------|

|-------|-----|-------|--------|

| Num | Characteristic               | All Freq | Unit |      |

|-----|------------------------------|----------|------|------|

| Num |                              | Min      | Мах  | Unit |

| 61  | TIN/TGATE rise and fall time | 10       | _    | ns   |

| 62  | TIN/TGATE low time           | 1        | _    | clk  |

| 63  | TIN/TGATE high time          | 2        | _    | clk  |

| 64  | TIN/TGATE cycle time         | 3        | _    | clk  |

| 65  | CLKO low to TOUT valid       | 3        | 25   | ns   |

**CPM Electrical Characteristics**

**CPM Electrical Characteristics**

| Num | Characteristic            | All Freq | Unit |      |  |

|-----|---------------------------|----------|------|------|--|

| Num |                           | Min      | Мах  | Onit |  |

| 210 | SDL/SCL fall time         | _        | 300  | ns   |  |

| 211 | Stop condition setup time | 4.7      | _    | μs   |  |

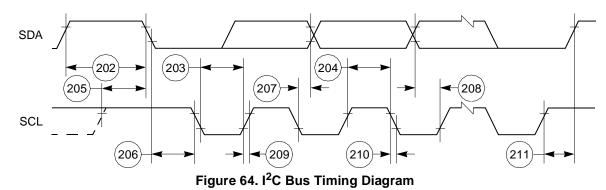

### Table 28. I<sup>2</sup>C Timing (SCL < 100 kHz) (continued)

SCL frequency is given by SCL = BRGCLK\_frequency/((BRG register + 3) × pre\_scalar × 2). The ratio SYNCCLK/(BRGCLK/pre\_scalar) must be greater than or equal to 4/1.

### Table 29 provides the $I^2C$ (SCL > 100 kHz) timings.

| Table 29. | I <sup>2</sup> C | Timing | (SCL | > | 100 | kHz) |

|-----------|------------------|--------|------|---|-----|------|

|-----------|------------------|--------|------|---|-----|------|

| Num   | Characteristic                            | Expression | All Freq        | Unit                        |      |

|-------|-------------------------------------------|------------|-----------------|-----------------------------|------|

| Nulli | Characteristic                            | Expression | Min             | Max                         | Unit |

| 200   | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48                   | Hz   |

| 200   | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48                   | Hz   |

| 202   | Bus free time between transmissions       | _          | 1/(2.2 × fSCL)  | _                           | S    |

| 203   | Low period of SCL                         | _          | 1/(2.2 × fSCL)  | _                           | S    |

| 204   | High period of SCL                        | _          | 1/(2.2 × fSCL)  | _                           | S    |

| 205   | Start condition setup time                | —          | 1/(2.2 × fSCL)  | —                           | S    |

| 206   | Start condition hold time                 | —          | 1/(2.2 × fSCL)  | —                           | S    |

| 207   | Data hold time                            | —          | 0               | —                           | S    |

| 208   | Data setup time                           | —          | 1/(40 × fSCL)   | —                           | S    |

| 209   | SDL/SCL rise time                         | —          | —               | $1/(10 \times fSCL)$        | S    |

| 210   | SDL/SCL fall time                         | —          | —               | $1/(33 \times \text{fSCL})$ | S    |

| 211   | Stop condition setup time                 | —          | 1/2(2.2 × fSCL) | _                           | S    |

SCL frequency is given by SCL = BRGCLK\_frequency/((BRG register + 3) × pre\_scalar × 2). The ratio SYNCCLK/(BRGCLK/pre\_scalar) must be greater than or equal to 4/1.

Figure 64 shows the  $I^2C$  bus timing.

### **16.1 Pin Assignments**

Figure 69 shows the JEDEC pinout of the PBGA package as viewed from the top surface. For additional information, see the *MPC885 PowerQUICC Family User's Manual*.

#### NOTE

The pin numbering starts with B2 in order to conform to the JEDEC standard for 23-mm body size using a  $16 \times 16$  array.

2 7 8 9 10 11 12 13 14 3 4 5 6 15 16 17 O O O O EXTCLK MODCK1  $\bigcup_{\mathsf{ALEA}}$ O  $O_{CS3}$ O N/C в Ο O OP0  $O_{\overline{CS5}}$ MODCK2  $\bigcirc_{\overline{BB}}$  $\bigcup_{\overline{TS}}$  $\bigcup_{\overline{TA}}$  $O_{CS2}$ С  $\bigcirc$  $\cap$ О  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ CE1A RSTCONF SRESET BADDR29 OP1 ALEB IRQ2 BDIP GPLAB3 GPLA0 IPA7 D  $\bigcirc$  $\bigcirc$ Ο IPA2 WAITA PORESET XTAL EXTAL BADDR30 IPB1 BG GPLA4 GPLA5  $\overline{\mathsf{WR}}$ CE2A CS7 WE2 WE1 IPA4 Е Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$ О Ο Ο Ο Ο Ο HRESET BADDR28 IRQ4 CS1 GPLB4 CS4 GPLAB2 BSA1 BSA2 **IRQ3 WEO** D31 IPA5 IPA3 VSSSYN VDDSYN F Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $O_{CS6}$ Ο Ο O  $\bigcirc$ O Ο  $\bigcirc$  $\bigcirc$  $\odot$ Ο Ο BSAO BSA3 D30 IPA6 IPA1 VSSSYN VDDL VDDL OE TSIZ0 A31 D29 G Ο Ο Ο  $\bigcirc$ Ο  $\bigcirc$ O VDDH  $\bigcirc$  $\bigcirc$ O VDDH  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$ Ο Ο D28 CLKOUT IPA0 WE3 TSI71 A22 D7 D26 A26 A18 н Ο Ο Ο Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$ Ο  $\bigcirc$ Ο Ο D22 D6 D24 D25 VDDL VDDH GND VDDH VDDL A28 A30 A25 A24 O D20 O D21 () A20 O A29 J Ο  $\bigcirc$  $\bigcirc$ Ο Ο  $\bigcirc$  $\bigcirc$ O A23 O A21 Ο Ο  $\bigcirc$ D19 D18 GND Κ Ο Ο Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο Ο Ο 0 Ο Ο  $\bigcirc$  $\bigcirc$ D15 D16 D14 VDDL GND VDDL D5 A14 A19 A27 A17 O D2 () A12 L  $\bigcirc$ Ο 0  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο D27 DO A15 A10 A16 D3 O VDDH () A8 Μ  $\bigcirc$ Ο Ο Ο 0  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ 0  $\bigcirc$  $\bigcirc$ Ο A11 **IRQ0** MII\_MDIO A2 A13 D11 D9 D12 PE18 0 0  $\bigcirc$ 0  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$ 0 Ν  $\bigcirc$ 0 Ο  $\bigcirc$ Ο  $\bigcirc$ D13 IRQ7 PA2 VDDL VDDL PB26 PB27 A1 A6 A7 D10 D1 A9  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$ Р Ο  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$ PE14 PE31 D23 D17 PE22 PA0 PA4 PC6 PA6 PC11 TDO PA15 A3 Α5 R О O Ο Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ O PB28 O PC15  $\bigcirc_{A0}$  $\bigcirc$ PE19 PE28 PE30 PA11 MII\_COL PA7 PA10 тск PB29 PE25 PA3 D4 D8  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$ Ο  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ т  $\bigcirc$ Ο  $\bigcirc$ PD8 PB31 PE27 PE17 PE21 PC7 PB19 PC12 N/C PB30 PE26 PA1 PE15 PB24 TDI TMS U O PE20 O PE23 MII-TX-EN PE16 O PE29 O PE24 O PC13 O MII-CRS O PC10 O PB23 O PB25 O PA14 O N/C

**NOTE:** This is the top view of the device.

Figure 69. Pinout of the PBGA Package—JEDEC Standard

| Name                                              | Pin Number | Туре                                                      |

|---------------------------------------------------|------------|-----------------------------------------------------------|

| IP_A6                                             | F4         | Input (3.3 V only)                                        |

| IP_A7                                             | C2         | Input (3.3 V only)                                        |

| ALE_B, DSCK                                       | C8         | Bidirectional<br>Three-state (3.3 V only)                 |

| IP_B[0:1], IWP[0:1],<br>VFLS[0:1]                 | B8, D9     | Bidirectional (3.3 V only)                                |

| OP0                                               | B6         | Bidirectional (3.3 V only)                                |

| OP1                                               | C6         | Output                                                    |

| OP2, MODCK1, STS                                  | B5         | Bidirectional (3.3 V only)                                |

| OP3, MODCK2, DSDO                                 | B2         | Bidirectional (3.3 V only)                                |

| BADDR[28:29]                                      | E8, C5     | Output                                                    |

| BADDR30, REG                                      | D8         | Output                                                    |

| ĀS                                                | C7         | Input (3.3 V only)                                        |

| PA15, USBRXD                                      | P14        | Bidirectional                                             |

| PA14, USBOE                                       | U16        | Bidirectional<br>(Optional: open-drain)                   |

| PA11, RXD4, MII1-TXD0,<br>RMII1-TXD0              | R9         | Bidirectional<br>(Optional: open-drain)<br>(5-V tolerant) |

| PA10, MII1-TXERR, TIN4,<br>CLK7                   | R12        | Bidirectional<br>(Optional: open-drain)<br>(5-V tolerant) |

| PA7, CLK1, BRGO1, TIN1                            | R11        | Bidirectional                                             |

| PA6, CLK2, TOUT1                                  | P11        | Bidirectional                                             |

| PA4, CTS4, MII1-TXD1,<br>RMII-TXD1                | P7         | Bidirectional                                             |

| PA3, MII1-RXER,<br>RMII1-RXER, BRGO3              | R5         | Bidirectional<br>(5-V tolerant)                           |

| PA2, MII1-RXDV,<br>RMII1-CRS_DV, TXD4             | N6         | Bidirectional<br>(5-V tolerant)                           |

| PA1, MII1-RXD0,<br>RMII1-RXD0, BRGO4              | Τ4         | Bidirectional<br>(5-V tolerant)                           |

| PA0, MII1-RXD1,<br>RMII1-RXD1, TOUT4              | P6         | Bidirectional<br>(5-V tolerant)                           |

| PB31, <u>SPISEL</u> , MII1-TXCLK,<br>RMII1-REFCLK | Т5         | Bidirectional<br>(Optional: open-drain)<br>(5-V tolerant) |

#### Table 36. Pin Assignments—JEDEC Standard (continued)

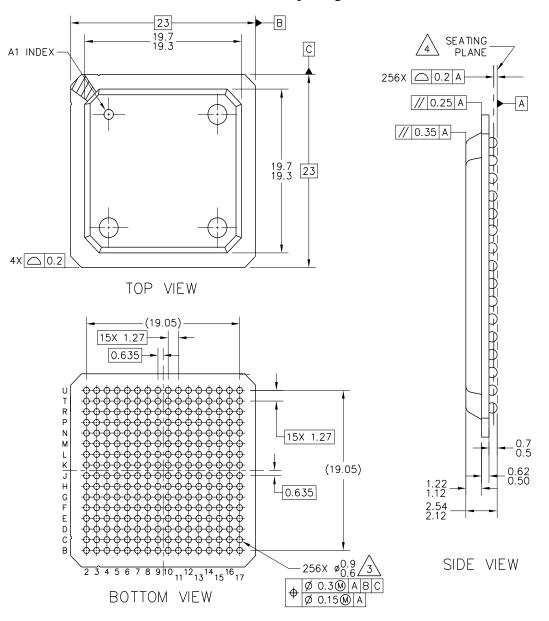

### 16.2 Mechanical Dimensions of the PBGA Package

Figure 70 shows the mechanical dimensions of the PBGA package.

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

- 4. DATUM A, THE SEATING PLANE, IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

- **Note:** Solder sphere composition is 95.5%Sn 45%Ag 0.5%Cu for MPC875/MPC870VRXXX. Solder sphere composition is 62%Sn 36%Pb 2%Ag for MPC875/MPC870ZTXXX.

#### Figure 70. Mechanical Dimensions and Bottom Surface Nomenclature of the PBGA Package

**Document Revision History**

#### THIS PAGE INTENTIONALLY LEFT BLANK

**Document Revision History**

### THIS PAGE INTENTIONALLY LEFT BLANK