#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Active                                                  |

|---------------------------------|---------------------------------------------------------|

| Core Processor                  | MPC8xx                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                          |

| Speed                           | 66MHz                                                   |

| Co-Processors/DSP               | Communications; CPM                                     |

| RAM Controllers                 | DRAM                                                    |

| Graphics Acceleration           | No                                                      |

| Display & Interface Controllers | -                                                       |

| Ethernet                        | 10/100Mbps (2)                                          |

| SATA                            | -                                                       |

| USB                             | USB 2.0 (1)                                             |

| Voltage - I/O                   | 3.3V                                                    |

| Operating Temperature           | 0°C ~ 95°C (TA)                                         |

| Security Features               | -                                                       |

| Package / Case                  | 256-BBGA                                                |

| Supplier Device Package         | 256-PBGA (23x23)                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc870zt66 |

|                                 |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- ECB, CBC, and counter modes

- 128-, 192-, and 256-bit key lengths

- Message digest execution unit (MDEU)

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Master/slave logic, with DMA

- 32-bit address/32-bit data

- Operation at MPC8xx bus frequency

- Crypto-channel supporting multi-command descriptors

- Integrated controller managing crypto-execution units

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Interrupts

- Six external interrupt request (IRQ) lines

- Twelve port pins with interrupt capability

- Twenty-three internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- 8-Kbytes of dual-port RAM

- Several serial DMA (SDMA) channels to support the CPM

- Three parallel I/O registers with open-drain capability

- On-chip  $16 \times 16$  multiply accumulate controller (MAC)

- One operation per clock (two-clock latency, one-clock blockage)

- MAC operates concurrently with other instructions

- FIR loop—Four clocks per four multiplies

- Four baud-rate generators

- Independent (can be connected to SCC or SMC)

- Allows changes during operation

- Autobaud support option

- SCC (serial communication controller)

- Ethernet/IEEE 802.3® standard, supporting full 10-Mbps operation

- HDLC/SDLC

Features

- The MPC875 has a time-slot assigner (TSA) that supports one TDM bus (TDMb)

- Allows SCC and SMC to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user-defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

- Allows dynamic changes

- Can be internally connected to two serial channels (one SCC and one SMC)

- PCMCIA interface

- Master (socket) interface, release 2.1-compliant

- Supports one independent PCMCIA socket on the MPC875/MPC870

- Eight memory or I/O windows supported

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two

operate on data

- Supports conditions: =  $\neq$  < >

- Each watchpoint can generate a break point internally

- Normal high and normal low power modes to conserve power

- 1.8-V core and 3.3-V I/O operation with 5-V TTL compatibility

- The MPC875/MPC870 comes in a 256-pin ball grid array (PBGA) package

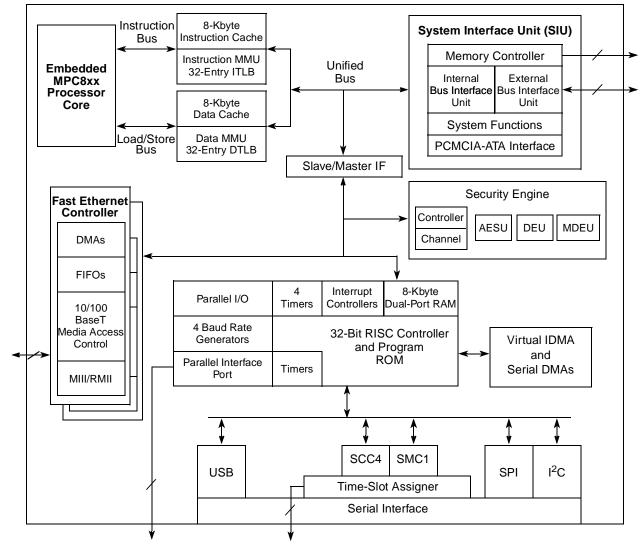

The MPC875 block diagram is shown in Figure 1.

Figure 1. MPC875 Block Diagram

# 11 Bus Signal Timing

The maximum bus speed supported by the MPC875/MPC870 is 80 MHz. Higher-speed parts must be operated in half-speed bus mode (for example, an MPC875/MPC870 used at 133 MHz must be configured for a 66 MHz bus). Table 8 shows the frequency ranges for standard part frequencies in 1:1 bus mode, and Table 9 shows the frequency ranges for standard part frequencies in 2:1 bus mode.

| Part Frequency | 66 I | MHz   | 80 MHz |     |

|----------------|------|-------|--------|-----|

| Tart requency  | Min  | Мах   | Min    | Мах |

| Core frequency | 40   | 66.67 | 40     | 80  |

| Bus frequency  | 40   | 66.67 | 40     | 80  |

### Table 8. Frequency Ranges for Standard Part Frequencies (1:1 Bus Mode)

### Table 9. Frequency Ranges for Standard Part Frequencies (2:1 Bus Mode)

| Part Frequency | 66 MHz |       | 80 MHz |     | 133 MHz |     |

|----------------|--------|-------|--------|-----|---------|-----|

| Part Frequency | Min    | Max   | Min    | Мах | Min     | Max |

| Core frequency | 40     | 66.67 | 40     | 80  | 40      | 133 |

| Bus frequency  | 20     | 33.33 | 20     | 40  | 20      | 66  |

Table 10 provides the bus operation timing for the MPC875/MPC870 at 33, 40, 66, and 80 MHz.

The timing for the MPC875/MPC870 bus shown Table 10, assumes a 50-pF load for maximum delays and a 0-pF load for minimum delays. CLKOUT assumes a 100-pF load maximum delay

Table 10. Bus Operation Timings

| Num | Characteristic                                                                                                                                                                                                                                                                                                               | 33  | 33 MHz |     | 40 MHz |     | MHz  | 80 MHz |      | Unit |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|--------|-----|------|--------|------|------|

| Num |                                                                                                                                                                                                                                                                                                                              | Min | Мах    | Min | Max    | Min | Max  | Min    | Max  | Omt  |

| B1  | Bus period (CLKOUT), see Table 8                                                                                                                                                                                                                                                                                             | _   | —      | —   | —      | _   |      | —      | —    | ns   |

| B1a | EXTCLK to CLKOUT phase skew—If<br>CLKOUT is an integer multiple of EXTCLK,<br>then the rising edge of EXTCLK is aligned with<br>the rising edge of CLKOUT. For a non-integer<br>multiple of EXTCLK, this synchronization is<br>lost, and the rising edges of EXTCLK and<br>CLKOUT have a continuously varying phase<br>skew. | -2  | +2     | -2  | +2     | -2  | +2   | -2     | +2   | ns   |

| B1b | CLKOUT frequency jitter peak-to-peak                                                                                                                                                                                                                                                                                         | _   | 1      | _   | 1      |     | 1    | _      | 1    | ns   |

| B1c | Frequency jitter on EXTCLK                                                                                                                                                                                                                                                                                                   | _   | 0.50   | _   | 0.50   | _   | 0.50 | _      | 0.50 | %    |

| B1d | CLKOUT phase jitter peak-to-peak for OSCLK $\ge$ 15 MHz                                                                                                                                                                                                                                                                      |     | 4      | —   | 4      |     | 4    | —      | 4    | ns   |

|     | CLKOUT phase jitter peak-to-peak for<br>OSCLK < 15 MHz                                                                                                                                                                                                                                                                       |     | 5      |     | 5      |     | 5    |        | 5    | ns   |

**Bus Signal Timing**

| Num  | Characteristic                                                                                                                                                                               |      | MHz   | 40 I | MHz   | 66   | 66 MHz 80 |      | MHz   | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|-----------|------|-------|------|

| num  | Characteristic                                                                                                                                                                               | Min  | Max   | Min  | Мах   | Min  | Мах       | Min  | Мах   | Unit |

| B2   | CLKOUT pulse width low (MIN = $0.4 \times B1$ , MAX = $0.6 \times B1$ )                                                                                                                      | 12.1 | 18.2  | 10.0 | 15.0  | 6.1  | 9.1       | 5.0  | 7.5   | ns   |

| B3   | CLKOUT pulse width high (MIN = $0.4 \times B1$ , MAX = $0.6 \times B1$ )                                                                                                                     | 12.1 | 18.2  | 10.0 | 15.0  | 6.1  | 9.1       | 5.0  | 7.5   | ns   |

| B4   | CLKOUT rise time                                                                                                                                                                             |      | 4.00  | —    | 4.00  | _    | 4.00      | _    | 4.00  | ns   |

| B5   | CLKOUT fall time                                                                                                                                                                             | _    | 4.00  | —    | 4.00  | _    | 4.00      | —    | 4.00  | ns   |

| B7   | CLKOUT to A(0:31), BADDR(28:30), RD/ $\overline{WR}$ , BURST, D(0:31) output hold (MIN = 0.25 × B1)                                                                                          | 7.60 | —     | 6.30 | —     | 3.80 | —         | 3.13 | —     | ns   |

| B7a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ , $\overline{\text{BDIP}}$ , PTR output hold (MIN = 0.25 × B1)                                                        | 7.60 | —     | 6.30 | —     | 3.80 | —         | 3.13 | —     | ns   |

| B7b  | $\begin{array}{l} CLKOUT to \ \overline{BR}, \ \overline{BG}, \ FRZ, \ VFLS(0:1), \ VF(0:2) \\ IWP(0:2), \ LWP(0:1), \ \overline{STS} \ output \ hold \\ (MIN = 0.25 \times B1) \end{array}$ | 7.60 | —     | 6.30 | —     | 3.80 | _         | 3.13 | —     | ns   |

| B8   | CLKOUT to A(0:31), BADDR(28:30), RD/ $\overline{WR}$ ,<br>BURST, D(0:31) valid (MAX = 0.25 × B1 + 6.3)                                                                                       | _    | 13.80 | —    | 12.50 | —    | 10.00     | —    | 9.43  | ns   |

| B8a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ , $\overline{\text{BDIP}}$ , PTR valid (MAX = 0.25 × B1 + 6.3)                                                        | _    | 13.80 | —    | 12.50 | —    | 10.00     | —    | 9.43  | ns   |

| B8b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , VFLS(0:1), VF(0:2),<br>IWP(0:2), FRZ, LWP(0:1), $\overline{STS}$ valid <sup>2</sup><br>(MAX = 0.25 × B1 + 6.3)                                 | _    | 13.80 | —    | 12.50 | —    | 10.00     | —    | 9.43  | ns   |

| B9   | CLKOUT to A(0:31), BADDR(28:30), RD/WR,<br>BURST, D(0:31), TSIZ(0:1), REG, RSV, PTR<br>High-Z (MAX = 0.25 × B1 + 6.3)                                                                        | 7.60 | 13.80 | 6.30 | 12.50 | 3.80 | 10.00     | 3.13 | 9.43  | ns   |

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion<br>(MAX = 0.25 × B1 + 6.0)                                                                                                             | 7.60 | 13.60 | 6.30 | 12.30 | 3.80 | 9.80      | 3.13 | 9.13  | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion (when driven by<br>the memory controller or PCMCIA interface)<br>(MAX = $0.00 \times B1 + 9.30^{1}$ )                                  | 2.50 | 9.30  | 2.50 | 9.30  | 2.50 | 9.80      | 2.5  | 9.3   | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation<br>(MAX = 0.25 × B1 + 4.8)                                                                                                              | 7.60 | 12.30 | 6.30 | 11.00 | 3.80 | 8.50      | 3.13 | 7.92  | ns   |

| B12a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ negation (when driven by<br>the memory controller or PCMCIA interface)<br>(MAX = $0.00 \times B1 + 9.00$ )                                       | 2.50 | 9.00  | 2.50 | 9.00  | 2.50 | 9.00      | 2.5  | 9.00  | ns   |

| B13  | CLKOUT to $\overline{\text{TS}}$ , $\overline{\text{BB}}$ High-Z (MIN = 0.25 × B1)                                                                                                           | 7.60 | 21.60 | 6.30 | 20.30 | 3.80 | 14.00     | 3.13 | 12.93 | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ High-Z (when driven by the memory controller or PCMCIA interface)<br>(MIN = $0.00 \times B1 + 2.5$ )                                             | 2.50 | 15.00 | 2.50 | 15.00 | 2.50 | 15.00     | 2.5  | 15.00 | ns   |

| B14  | CLKOUT to $\overline{\text{TEA}}$ assertion<br>(MAX = $0.00 \times \text{B1} + 9.00$ )                                                                                                       | 2.50 | 9.00  | 2.50 | 9.00  | 2.50 | 9.00      | 2.50 | 9.00  | ns   |

### Table 10. Bus Operation Timings (continued)

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33    | MHz | 40 M  | MHz | 66    | MHz | 80 MHz |     |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----|-------|-----|--------|-----|------|

| Num  | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Min   | Max | Min   | Max | Min   | Max | Min    | Max | Unit |

| B29d | $\label{eq:weight} \hline \hline WE(0:3)/BS_B[0:3] \mbox{ negated to } D(0:31) \mbox{ High-Z} \\ GPCM \mbox{ write access, } TRLX = 1, \mbox{ CSNT} = 1, \\ EBDF = 0 \mbox{ (MIN} = 1.50 \times B1 - 2.00) \\ \hline \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43.50 |     | 35.50 |     | 20.70 |     | 16.75  |     | ns   |

| B29e | $\overline{CS}$ negated to D(0:31) High-Z GPCM write<br>access, TRLX = 1, CSNT = 1, ACS = 10 or<br>ACS = 11, EBDF = 0 (MIN = 1.50 × B1 - 2.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43.50 | _   | 35.50 |     | 20.70 | _   | 16.75  | _   | ns   |

| B29f | $\label{eq:weighted_states} \hline \hline WE(0:3/BS_B[0:3]) \ \text{negated to } D(0:31) \ \text{High-Z} \\ \text{GPCM write access, } TRLX = 0, \ \text{CSNT} = 1, \\ \text{EBDF} = 1 \ (\text{MIN} = 0.375 \times \text{B1} - 6.30)^7 \\ \hline \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.00  |     | 3.00  |     | 0.00  |     | 0.00   | _   | ns   |

| B29g | $\overline{\text{CS}}$ negated to D(0:31) High-Z GPCM write<br>access, TRLX = 0, CSNT = 1 ACS = 10 or<br>ACS = 11, EBDF = 1<br>(MIN = 0.375 × B1 - 6.30) <sup>7</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.00  | _   | 3.00  | _   | 0.00  | _   | 0.00   | _   | ns   |

| B29h | $\label{eq:weighted} \hline \hline WE(0:3)/BS_B[0:3] \mbox{ negated to } D(0:31) \mbox{ High-Z} \\ GPCM \mbox{ write access, } TRLX = 1, \mbox{ CSNT = 1,} \\ EBDF = 1 \mbox{ (MIN = } 0.375 \times B1 - 3.30) \\ \hline \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38.40 | _   | 31.10 | _   | 17.50 | _   | 13.85  | _   | ns   |

| B29i | $\overline{CS}$ negated to D(0:31) (0:3) High-Z GPCM<br>write access, TRLX = 1, CSNT = 1, ACS = 10<br>or ACS = 11, EBDF = 1<br>(MIN = 0.375 × B1 - 3.30)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38.40 | _   | 31.10 | _   | 17.50 | _   | 13.85  | _   | ns   |

| B30  | $\overline{\text{CS}}$ , $\overline{\text{WE}}(0:3)/\text{BS}_{B}[0:3]$ negated to A(0:31),<br>BADDR(28:30) invalid GPCM write access <sup>8</sup><br>(MIN = 0.25 × B1 - 2.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.60  | _   | 4.30  |     | 1.80  | _   | 1.13   | _   | ns   |

| B30a | $\label{eq:weighted_states} \hline \hline WE(0:3)/BS_B[0:3] \mbox{ negated to } A(0:31), \\ BADDR(28:30) \mbox{ invalid GPCM, write access,} \\ TRLX = 0, \mbox{ CSNT = 1, } \hline CS \mbox{ negated to } A(0:31), \\ \mbox{ invalid GPCM write access } TRLX = 0, \\ CSNT = 1, \mbox{ ACS = 10 or } ACS == 11, \mbox{ EBDF = 0} \\ (MIN = 0.50 \times B1 - 2.00) \\ \hline \hline \hline \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13.20 | _   | 10.50 |     | 5.60  | _   | 4.25   | _   | ns   |

| B30b | $eq:weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_$ | 43.50 | _   | 35.50 |     | 20.70 | _   | 16.75  | _   | ns   |

| B30c | $eq:weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_$ | 8.40  | _   | 6.40  | _   | 2.70  | _   | 1.70   | _   | ns   |

### Table 10. Bus Operation Timings (continued)

**Bus Signal Timing**

| Table 10. Bus | Operation | Timings | (continued) |

|---------------|-----------|---------|-------------|

|---------------|-----------|---------|-------------|

| Num | Characteristic                                                                      | 33 MHz |     | 40 MHz |     | 66 MHz |     | 80 MHz |     | Unit |

|-----|-------------------------------------------------------------------------------------|--------|-----|--------|-----|--------|-----|--------|-----|------|

|     | Unaracteristic                                                                      | Min    | Max | Min    | Max | Min    | Max | Min    | Max | onit |

| B42 | CLKOUT rising edge to $\overline{TS}$ valid (hold time)<br>(MIN = 0.00 × B1 + 2.00) | 2.00   | —   | 2.00   | _   | 2.00   | _   | 2.00   | _   | ns   |

| B43 | AS negation to memory controller signals negation (MAX = TBD)                       | —      | TBD | _      | TBD | _      | TBD | _      | TBD | ns   |

<sup>1</sup> For part speeds above 50 MHz, use 9.80 ns for B11a.

<sup>2</sup> The timing required for BR input is relevant when the MPC875/MPC870 is selected to work with the internal bus arbiter. The timing for BG input is relevant when the MPC875/MPC870 is selected to work with the external bus arbiter.

<sup>3</sup> For part speeds above 50 MHz, use 2 ns for B17.

<sup>4</sup> The D(0:31) input timings B18 and B19 refer to the rising edge of the CLKOUT in which the TA input signal is asserted.

<sup>5</sup> For part speeds above 50 MHz, use 2 ns for B19.

<sup>6</sup> The D(0:31) input timings B20 and B21 refer to the falling edge of the CLKOUT. This timing is valid only for read accesses controlled by chip-selects under control of the user-programmable machine (UPM) in the memory controller, for data beats where DLT3 = 1 in the RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

<sup>7</sup> This formula applies to bus operation up to 50 MHz.

<sup>8</sup> The timing B30 refers to  $\overline{CS}$  when ACS = 00 and to  $\overline{WE}(0:3)$  when CSNT = 0.

<sup>9</sup> The signal UPWAIT is considered asynchronous to the CLKOUT and synchronized internally. The timings specified in B37 and B38 are specified to enable the freeze of the UPM output signals as described in Figure 20.

<sup>10</sup> The AS signal is considered asynchronous to the CLKOUT. The timing B39 is specified in order to allow the behavior specified in Figure 23.

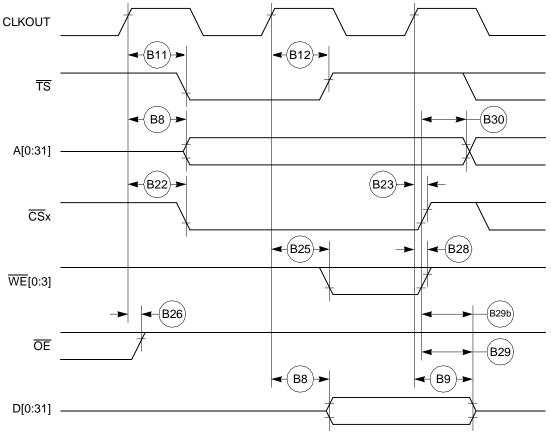

Figure 16 through Figure 18 provide the timing for the external bus write controlled by various GPCM factors.

```

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 0)

```

1

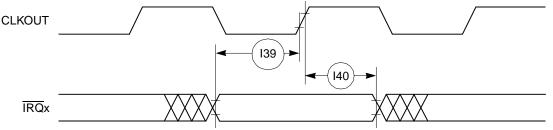

Table 11 provides the interrupt timing for the MPC875/MPC870.

| Table 11. Interrupt Timing |  |

|----------------------------|--|

|----------------------------|--|

| Num   | Characteristic <sup>1</sup>                   | All Freq                  | Unit |      |

|-------|-----------------------------------------------|---------------------------|------|------|

| Nulli | Characteristic                                | Min                       | Мах  | Unit |

| 139   | IRQx valid to CLKOUT rising edge (setup time) | 6.00                      |      | ns   |

| 140   | IRQx hold time after CLKOUT                   | 2.00                      |      | ns   |

| 141   | IRQx pulse width low                          | 3.00                      |      | ns   |

| 142   | IRQx pulse width high                         | 3.00                      |      | ns   |

| 143   | IRQx edge-to-edge time                        | 4 × T <sub>CLOCKOUT</sub> |      | —    |

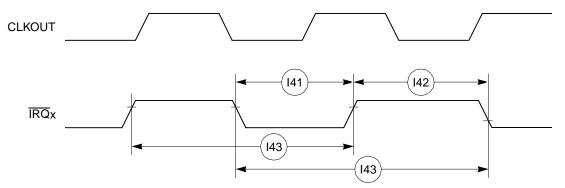

The I39 and I40 timings describe the testing conditions under which the IRQ lines are tested when being defined as level sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT. The I41, I42, and I43 timings are specified to allow correct functioning of the IRQ lines detection circuitry and have no direct relation with the total system interrupt latency that the MPC875/MPC870 is able to support.

Figure 25 provides the interrupt detection timing for the external level-sensitive lines.

Figure 25. Interrupt Detection Timing for External Level Sensitive Lines

Figure 26 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 26. Interrupt Detection Timing for External Edge-Sensitive Lines

Table 13 shows the PCMCIA port timing for the MPC875/MPC870.

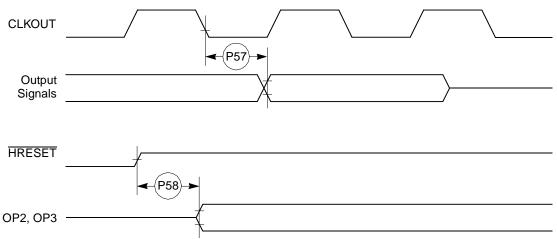

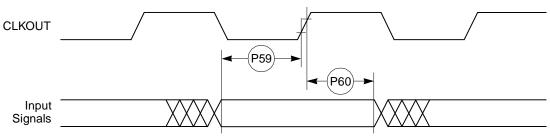

#### 33 MHz 40 MHz 66 MHz 80 MHz Num Characteristic Unit Min Max Min Max Min Max Min Max CLKOUT to OPx valid 19.00 19.00 19.00 19.00 \_\_\_\_ \_\_\_\_ \_\_\_\_ ns P57 $(MAX = 0.00 \times B1 + 19.00)$ HRESET negated to OPx drive<sup>1</sup> 25.70 21.70 14.40 12.40 ns \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ P58 $(MIN = 0.75 \times B1 + 3.00)$ IP\_Xx valid to CLKOUT rising edge 5.00 5.00 5.00 5.00 \_\_\_\_ \_\_\_\_ ns P59 $(MIN = 0.00 \times B1 + 5.00)$ CLKOUT rising edge to IP\_Xx invalid 1.00 1.00 1.00 1.00 ns \_\_\_\_ P60 $(MIN = 0.00 \times B1 + 1.00)$

### Table 13. PCMCIA Port Timing

OP2 and OP3 only.

### Figure 30 provides the PCMCIA output port timing for the MPC875/MPC870.

### Figure 30. PCMCIA Output Port Timing

Figure 31 provides the PCMCIA input port timing for the MPC875/MPC870.

Figure 31. PCMCIA Input Port Timing

# **13 CPM Electrical Characteristics**

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC875/MPC870.

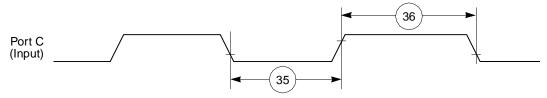

## **13.1 Port C Interrupt AC Electrical Specifications**

Table 17 provides the timings for Port C interrupts.

| Table | 17. | Port C | Interrupt | Timing |

|-------|-----|--------|-----------|--------|

|-------|-----|--------|-----------|--------|

| Num Characte | Characteristic                                         | 33.34 | MHz | Unit |

|--------------|--------------------------------------------------------|-------|-----|------|

| Num          | onaracteristic                                         | Min   | Мах | Onic |

| 35           | Port C interrupt pulse width low (edge-triggered mode) | 55    | _   | ns   |

| 36           | Port C interrupt minimum time between active edges     | 55    | _   | ns   |

Figure 41 shows the Port C interrupt detection timing.

Figure 41. Port C Interrupt Detection Timing

### 13.2 IDMA Controller AC Electrical Specifications

Table 18 provides the IDMA controller timings as shown in Figure 42 through Figure 45.

### Table 18. IDMA Controller Timing

| Num   | Characteristic                                                                                          | All Freq | uencies | s Unit |  |

|-------|---------------------------------------------------------------------------------------------------------|----------|---------|--------|--|

| Nulli | Characteristic                                                                                          | Min      | Max     | Unit   |  |

| 40    | DREQ setup time to clock high                                                                           | 7        | _       | ns     |  |

| 41    | DREQ hold time from clock high <sup>1</sup>                                                             | TBD      | _       | ns     |  |

| 42    | SDACK assertion delay from clock high                                                                   | _        | 12      | ns     |  |

| 43    | SDACK negation delay from clock low                                                                     | _        | 12      | ns     |  |

| 44    | SDACK negation delay from TA low                                                                        | _        | 20      | ns     |  |

| 45    | SDACK negation delay from clock high                                                                    | _        | 15      | ns     |  |

| 46    | $\overline{TA}$ assertion to rising edge of the clock setup time (applies to external $\overline{TA}$ ) | 7        | _       | ns     |  |

<sup>1</sup> Applies to high-to-low mode (EDM = 1).

Figure 43. SDACK Timing Diagram—Peripheral Write, Externally-Generated TA

### **13.3 Baud Rate Generator AC Electrical Specifications**

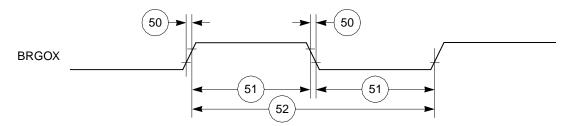

Table 19 provides the baud rate generator timings as shown in Figure 46.

### Table 19. Baud Rate Generator Timing

| Num | Characteristic          | All Frequencies |     | Unit |

|-----|-------------------------|-----------------|-----|------|

| Num | Characteristic          | Min             | Max | Onit |

| 50  | BRGO rise and fall time | _               | 10  | ns   |

| 51  | BRGO duty cycle         | 40              | 60  | %    |

| 52  | BRGO cycle              | 40              | _   | ns   |

Figure 46. Baud Rate Generator Timing Diagram

### **13.4 Timer AC Electrical Specifications**

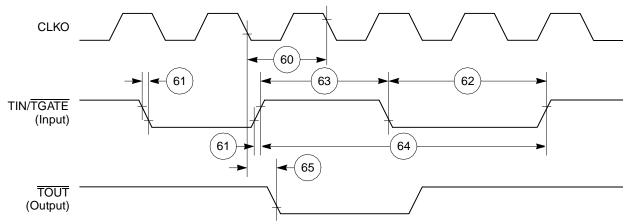

Table 20 provides the general-purpose timer timings as shown in Figure 47.

| Table | 20. | Timer | Timing |

|-------|-----|-------|--------|

|-------|-----|-------|--------|

| Num | Characteristic               | All Frequencies | Unit |      |

|-----|------------------------------|-----------------|------|------|

|     | Characteristic               | Min             | Мах  | Unit |

| 61  | TIN/TGATE rise and fall time | 10              | _    | ns   |

| 62  | TIN/TGATE low time           | 1               | _    | clk  |

| 63  | TIN/TGATE high time          | 2               | _    | clk  |

| 64  | TIN/TGATE cycle time         | 3               | —    | clk  |

| 65  | CLKO low to TOUT valid       | 3               | 25   | ns   |

Figure 47. CPM General-Purpose Timers Timing Diagram

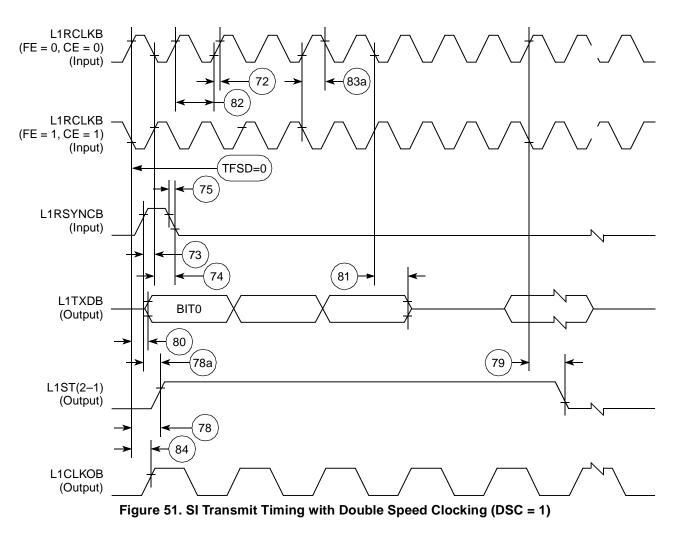

### **13.5** Serial Interface AC Electrical Specifications

Table 21 provides the serial interface (SI) timings as shown in Figure 48 through Figure 52.

| Num | Characteristic                                              | All Fre | All Frequencies       |      |

|-----|-------------------------------------------------------------|---------|-----------------------|------|

| Num | Characteristic                                              | Min     | Мах                   | Unit |

| 70  | L1RCLKB, L1TCLKB frequency (DSC = 0) <sup>1, 2</sup>        | —       | SYNCCLK/2.5           | MHz  |

| 71  | L1RCLKB, L1TCLKB width low $(DSC = 0)^2$                    | P + 10  | —                     | ns   |

| 71a | L1RCLKB, L1TCLKB width high $(DSC = 0)^3$                   | P + 10  |                       | ns   |

| 72  | L1TXDB, L1ST1 and L1ST2, L1RQ, L1CLKO rise/fall time        | _       | 15.00                 | ns   |

| 73  | L1RSYNCB, L1TSYNCB valid to L1CLKB edge (SYNC setup time)   | 20.00   |                       | ns   |

| 74  | L1CLKB edge to L1RSYNCB, L1TSYNCB, invalid (SYNC hold time) | 35.00   |                       | ns   |

| 75  | L1RSYNCB, L1TSYNCB rise/fall time                           | —       | 15.00                 | ns   |

| 76  | L1RXDB valid to L1CLKB edge (L1RXDB setup time)             | 17.00   |                       | ns   |

| 77  | L1CLKB edge to L1RXDB invalid (L1RXDB hold time)            | 13.00   | —                     | ns   |

| 78  | L1CLKB edge to L1ST1 and L1ST2 valid <sup>4</sup>           | 10.00   | 45.00                 | ns   |

| 78A | L1SYNCB valid to L1ST1 and L1ST2 valid                      | 10.00   | 45.00                 | ns   |

| 79  | L1CLKB edge to L1ST1 and L1ST2 invalid                      | 10.00   | 45.00                 | ns   |

| 80  | L1CLKB edge to L1TXDB valid                                 | 10.00   | 55.00                 | ns   |

| 80A | L1TSYNCB valid to L1TXDB valid <sup>4</sup>                 | 10.00   | 55.00                 | ns   |

| 81  | L1CLKB edge to L1TXDB high impedance                        | 0.00    | 42.00                 | ns   |

| 82  | L1RCLKB, L1TCLKB frequency (DSC = 1)                        | _       | 16.00 or<br>SYNCCLK/2 | MHz  |

| 83  | L1RCLKB, L1TCLKB width low (DSC = 1)                        | P + 10  | —                     | ns   |

### Table 21. SI Timing

**CPM Electrical Characteristics**

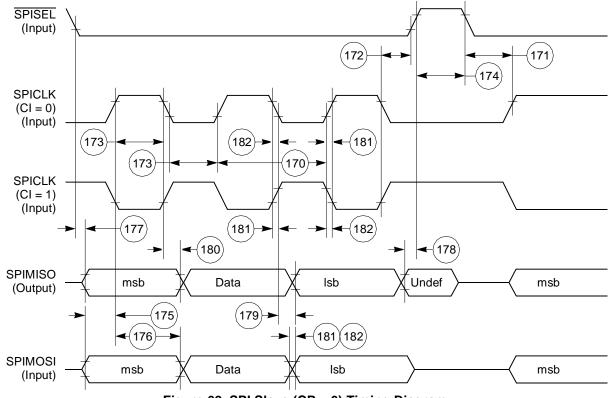

### 13.10 SPI Slave AC Electrical Specifications

Table 27 provides the SPI slave timings as shown in Figure 62 and Figure 63.

### Table 27. SPI Slave Timing

| Num | Characteristic                                              | All Frequencies |     | Unit             |

|-----|-------------------------------------------------------------|-----------------|-----|------------------|

| Num | Characteristic                                              | Min             | Мах | Unit             |

| 170 | Slave cycle time                                            | 2               | —   | t <sub>cyc</sub> |

| 171 | Slave enable lead time                                      | 15              | —   | ns               |

| 172 | Slave enable lag time                                       | 15              | —   | ns               |

| 173 | Slave clock (SPICLK) high or low time                       | 1               | —   | t <sub>cyc</sub> |

| 174 | Slave sequential transfer delay (does not require deselect) | 1               | —   | t <sub>cyc</sub> |

| 175 | Slave data setup time (inputs)                              | 20              | —   | ns               |

| 176 | Slave data hold time (inputs)                               | 20              | —   | ns               |

| 177 | Slave access time                                           | _               | 50  | ns               |

# 14 USB Electrical Characteristics

This section provides the AC timings for the USB interface.

### 14.1 USB Interface AC Timing Specifications

The USB Port uses the transmit clock on SCC1. Table 30 lists the USB interface timings.

### Table 30. USB Interface AC Timing Specifications

| Name | Characteristic                                                        | All Frequencies |     | Unit |

|------|-----------------------------------------------------------------------|-----------------|-----|------|

|      |                                                                       | Min             | Max |      |

| US1  | USBCLK frequency of operation <sup>1</sup><br>Low speed<br>Full speed | 6<br>48         |     | MHz  |

| US4  | USBCLK duty cycle (measured at 1.5 V)                                 | 45              | 55  | %    |

<sup>1</sup> USBCLK accuracy should be ±500 ppm or better. USBCLK may be stopped to conserve power.

# **15 FEC Electrical Characteristics**

This section provides the AC electrical specifications for the Fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 or 3.3 V.

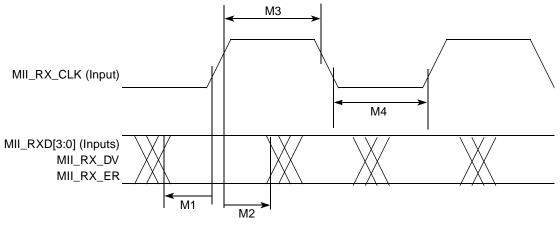

### 15.1 MII and Reduced MII Receive Signal Timing

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25 MHz + 1%. The reduced MII (RMII) receiver functions correctly up to a RMII\_REFCLK maximum frequency of 50 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency -1%.

Table 31 provides information on the MII receive signal timing.

| Num     | Characteristic                                                 | Min | Мах | Unit              |

|---------|----------------------------------------------------------------|-----|-----|-------------------|

| M1      | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup         | 5   | _   | ns                |

| M2      | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold          | 5   | _   | ns                |

| M3      | MII_RX_CLK pulse width high                                    | 35% | 65% | MII_RX_CLK period |

| M4      | MII_RX_CLK pulse width low                                     | 35% | 65% | MII_RX_CLK period |

| M1_RMII | RMII_RXD[1:0], RMII_CRS_DV, RMII_RX_ERR to RMII_REFCLK setup   | 4   |     | ns                |

| M2_RMII | RMII_REFCLK to RMII_RXD[1:0], RMII_CRS_DV, RMII_RX_ERR<br>hold | 2   |     | ns                |

Table 31. MII Receive Signal Timing

Figure 65 shows MII receive signal timing.

Figure 65. MII Receive Signal Timing Diagram

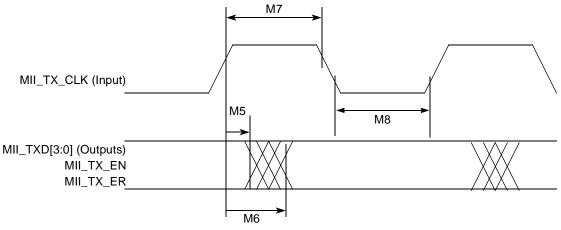

### 15.2 MII and Reduced MII Transmit Signal Timing

The transmitter functions correctly up to a MII\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_TX\_CLK frequency -1%.

Table 32 provides information on the MII transmit signal timing.

| Table 32. M | III Transmit | Signal Timing |

|-------------|--------------|---------------|

|-------------|--------------|---------------|

| Num      | Characteristic                                                   | Min | Max | Unit              |

|----------|------------------------------------------------------------------|-----|-----|-------------------|

| M5       | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER invalid         | 5   | _   | ns                |

| M6       | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER valid           |     | 25  | ns                |

| M7       | MII_TX_CLK pulse width high                                      | 35% | 65% | MII_TX_CLK period |

| M8       | MII_TX_CLK pulse width low                                       | 35% | 65% | MII_TX_CLK period |

| M20_RMII | RMII_TXD[1:0], RMII_TX_EN to RMII_REFCLK setup                   | 4   | _   | ns                |

| M21_RMII | RMII_TXD[1:0], RMII_TX_EN data hold from RMII_REFCLK rising edge | 2   | _   | ns                |

Figure 66 shows the MII transmit signal timing diagram.

Figure 66. MII Transmit Signal Timing Diagram

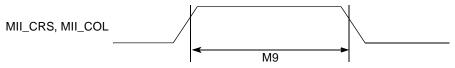

## 15.3 MII Async Inputs Signal Timing (MII\_CRS, MII\_COL)

Table 33 provides information on the MII async inputs signal timing.

### Table 33. MII Async Inputs Signal Timing

| Nu | Characteristic                       | Min | Max | Unit              |

|----|--------------------------------------|-----|-----|-------------------|

| M  | MII_CRS, MII_COL minimum pulse width | 1.5 | —   | MII_TX_CLK period |

Figure 67 shows the MII asynchronous inputs signal timing diagram.

Figure 67. MII Async Inputs Timing Diagram

### 15.4 MII Serial Management Channel Timing (MII\_MDIO, MII\_MDC)

Table 34 provides information on the MII serial management channel signal timing. The FEC functions correctly with a maximum MDC frequency in excess of 2.5 MHz.

| Table 34. MII Serial Management Channel Tir | ning |

|---------------------------------------------|------|

|---------------------------------------------|------|

| Num | Characteristic                                                              | Min | Мах | Unit           |

|-----|-----------------------------------------------------------------------------|-----|-----|----------------|

| M10 | MII_MDC falling edge to MII_MDIO output invalid (minimum propagation delay) | 0   | —   | ns             |

| M11 | MII_MDC falling edge to MII_MDIO output valid (max prop delay)              | _   | 25  | ns             |

| M12 | MII_MDIO (input) to MII_MDC rising edge setup                               | 10  | —   | ns             |

| M13 | MII_MDIO (input) to MII_MDC rising edge hold                                | 0   | —   | ns             |

| M14 | MII_MDC pulse width high                                                    | 40% | 60% | MII_MDC period |

| M15 | MII_MDC pulse width low                                                     | 40% | 60% | MII_MDC period |

| Name                                              | Pin Number | Туре                                                      |

|---------------------------------------------------|------------|-----------------------------------------------------------|

| IP_A6                                             | F4         | Input (3.3 V only)                                        |

| IP_A7                                             | C2         | Input (3.3 V only)                                        |

| ALE_B, DSCK                                       | C8         | Bidirectional<br>Three-state (3.3 V only)                 |

| IP_B[0:1], IWP[0:1],<br>VFLS[0:1]                 | B8, D9     | Bidirectional (3.3 V only)                                |

| OP0                                               | B6         | Bidirectional (3.3 V only)                                |

| OP1                                               | C6         | Output                                                    |

| OP2, MODCK1, STS                                  | B5         | Bidirectional (3.3 V only)                                |

| OP3, MODCK2, DSDO                                 | B2         | Bidirectional (3.3 V only)                                |

| BADDR[28:29]                                      | E8, C5     | Output                                                    |

| BADDR30, REG                                      | D8         | Output                                                    |

| ĀS                                                | C7         | Input (3.3 V only)                                        |

| PA15, USBRXD                                      | P14        | Bidirectional                                             |

| PA14, USBOE                                       | U16        | Bidirectional<br>(Optional: open-drain)                   |

| PA11, RXD4, MII1-TXD0,<br>RMII1-TXD0              | R9         | Bidirectional<br>(Optional: open-drain)<br>(5-V tolerant) |

| PA10, MII1-TXERR, TIN4,<br>CLK7                   | R12        | Bidirectional<br>(Optional: open-drain)<br>(5-V tolerant) |

| PA7, CLK1, BRGO1, TIN1                            | R11        | Bidirectional                                             |

| PA6, CLK2, TOUT1                                  | P11        | Bidirectional                                             |

| PA4, CTS4, MII1-TXD1,<br>RMII-TXD1                | P7         | Bidirectional                                             |

| PA3, MII1-RXER,<br>RMII1-RXER, BRGO3              | R5         | Bidirectional<br>(5-V tolerant)                           |

| PA2, MII1-RXDV,<br>RMII1-CRS_DV, TXD4             | N6         | Bidirectional<br>(5-V tolerant)                           |

| PA1, MII1-RXD0,<br>RMII1-RXD0, BRGO4              | Τ4         | Bidirectional<br>(5-V tolerant)                           |

| PA0, MII1-RXD1,<br>RMII1-RXD1, TOUT4              | P6         | Bidirectional<br>(5-V tolerant)                           |

| PB31, <u>SPISEL</u> , MII1-TXCLK,<br>RMII1-REFCLK | Т5         | Bidirectional<br>(Optional: open-drain)<br>(5-V tolerant) |

### Table 36. Pin Assignments—JEDEC Standard (continued)