#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Obsolete                                                |

|---------------------------------|---------------------------------------------------------|

| Core Processor                  | MPC8xx                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                          |

| Speed                           | 80MHz                                                   |

| Co-Processors/DSP               | Communications; CPM, Security; SEC                      |

| RAM Controllers                 | DRAM                                                    |

| Graphics Acceleration           | No                                                      |

| Display & Interface Controllers | -                                                       |

| Ethernet                        | 10Mbps (1), 10/100Mbps (2)                              |

| SATA                            | -                                                       |

| USB                             | USB 2.0 (1)                                             |

| Voltage - I/O                   | 3.3V                                                    |

| Operating Temperature           | 0°C ~ 95°C (TA)                                         |

| Security Features               | Cryptography                                            |

| Package / Case                  | 256-BBGA                                                |

| Supplier Device Package         | 256-PBGA (23x23)                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc875zt80 |

|                                 |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Thirty-two address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to DRAM, SIMMS, SRAM, EPROMs, Flash EPROMs, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes–256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

- Two Fast Ethernet controllers (FEC)—Two 10/100 Mbps Ethernet/IEEE Std. 802.3® CDMA/CS that interface through MII and/or RMII interfaces

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Clock synthesizer

- Decrementer and time base

- Reset controller

- IEEE 1149.1<sup>™</sup> Std. test access port (JTAG)

- Security engine is optimized to handle all the algorithms associated with IPsec, SSL/TLS, SRTP, IEEE 802.11i® standard, and iSCSI processing. Available on the MPC875, the security engine contains a crypto-channel, a controller, and a set of crypto hardware accelerators (CHAs). The CHAs are:

- Data encryption standard execution unit (DEU)

- DES, 3DES

- Two key (K1, K2, K1) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rijndael symmetric key cipher

Features

- ECB, CBC, and counter modes

- 128-, 192-, and 256-bit key lengths

- Message digest execution unit (MDEU)

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Master/slave logic, with DMA

- 32-bit address/32-bit data

- Operation at MPC8xx bus frequency

- Crypto-channel supporting multi-command descriptors

- Integrated controller managing crypto-execution units

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Interrupts

- Six external interrupt request (IRQ) lines

- Twelve port pins with interrupt capability

- Twenty-three internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- 8-Kbytes of dual-port RAM

- Several serial DMA (SDMA) channels to support the CPM

- Three parallel I/O registers with open-drain capability

- On-chip  $16 \times 16$  multiply accumulate controller (MAC)

- One operation per clock (two-clock latency, one-clock blockage)

- MAC operates concurrently with other instructions

- FIR loop—Four clocks per four multiplies

- Four baud-rate generators

- Independent (can be connected to SCC or SMC)

- Allows changes during operation

- Autobaud support option

- SCC (serial communication controller)

- Ethernet/IEEE 802.3® standard, supporting full 10-Mbps operation

- HDLC/SDLC

# 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC875/MPC870. Table 2 displays the maximum tolerated ratings and Table 3 displays the operating temperatures.

| Rating                      | Symbol                                       | Value                                                                                | Unit |

|-----------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|------|

| Supply voltage <sup>1</sup> | V <sub>DDL</sub> (core voltage)              | -0.3 to 3.4                                                                          | V    |

|                             | V <sub>DDH</sub> (I/O voltage)               | -0.3 to 4                                                                            | V    |

|                             | V <sub>DDSYN</sub>                           | -0.3 to 3.4                                                                          | V    |

|                             | Difference between $V_{DDL}$ and $V_{DDSYN}$ | <100                                                                                 | mV   |

| Input voltage <sup>2</sup>  | V <sub>in</sub>                              | $\ensuremath{GND}\xspace - 0.3$ to $\ensuremath{V}\xspace_{\ensuremath{DDH}\xspace}$ | V    |

| Storage temperature range   | T <sub>stg</sub>                             | –55 to +150                                                                          | °C   |

### Table 2. Maximum Tolerated Ratings

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than V<sub>DDH</sub>. This restriction applies to power up and normal operation (that is, if the MPC875/MPC870 is unpowered, a voltage greater than 2.5 V must not be applied to its inputs).

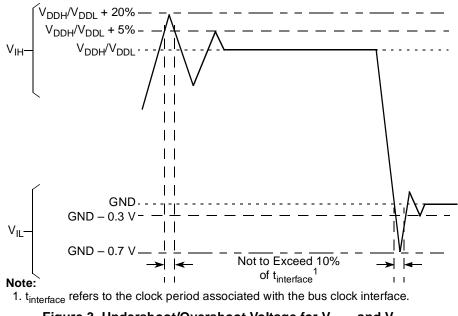

Figure 3 shows the undershoot and overshoot voltages at the interfaces of the MPC875/MPC870.

Figure 3. Undershoot/Overshoot Voltage for  $V_{\text{DDH}}$  and  $V_{\text{DDL}}$

Power Supply and Power Sequencing

## 7.5 Experimental Determination

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$\Psi_{JT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per the JESD51-2 specification published by JEDEC using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by the cooling effects of the thermocouple wire.

## 7.6 References

| Semiconductor Equipment and Materials International<br>805 East Middlefield Rd | (415) 964-5111       |

|--------------------------------------------------------------------------------|----------------------|

| Mountain View, CA 94043                                                        |                      |

| MIL-SPEC and EIA/JESD (JEDEC) specifications                                   | 800-854-7179 or      |

| (Available from Global Engineering Documents)                                  | 303-397-7956         |

| JEDEC Specifications                                                           | http://www.jedec.org |

- 1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 8 Power Supply and Power Sequencing

This section provides design considerations for the MPC875/MPC870 power supply. The MPC875/MPC870 has a core voltage ( $V_{DDL}$ ) and PLL voltage ( $V_{DDSYN}$ ), which both operate at a lower voltage than the I/O voltage ( $V_{DDH}$ ). The I/O section of the MPC875/MPC870 is supplied with 3.3 V across  $V_{DDH}$  and  $V_{SS}$  (GND).

The signals PA[0:3], PA[8:11], PB15, PB[24:25], PB[28:31], PC[4:7], PC[12:13], PC15, PD[3:15], TDI, TDO, TCK, TRST, TMS, MII\_TXEN, and MII\_MDIO are 5 V tolerant. No input can be more than 2.5 V greater than V<sub>DDH</sub>. In addition, 5-V tolerant pins cannot exceed 5.5 V, and remaining input pins cannot exceed 3.465 V. This restriction applies to power up, power down, and normal operation.

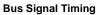

**Bus Signal Timing**

| Num  | Characteristic                                                                                                                                                                                           | 33    | MHz   | 40    | MHz   | 66    | MHz   | 80 MHz |       | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                                                                           | Min   | Max   | Min   | Max   | Min   | Max   | Min    | Max   | Unit |

| B30d | WE(0:3)/BS_B[0:3] negated to A(0:31),<br>BADDR(28:30) invalid GPCM write access<br>TRLX = 1, CSNT =1, CS negated to A(0:31)<br>invalid GPCM write access TRLX = 1,<br>CSNT = 1, ACS = 10 or 11, EBDF = 1 | 38.67 |       | 31.38 |       | 17.83 |       | 14.19  |       | ns   |

| B31  | CLKOUT falling edge to $\overline{CS}$ valid as requested<br>by control bit CST4 in the corresponding word<br>in the UPM (MAX = $0.00 \times B1 + 6.00$ )                                                | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50   | 6.00  | ns   |

| B31a | CLKOUT falling edge to $\overline{CS}$ valid as requested<br>by control bit CST1 in the corresponding word<br>in the UPM (MAX = $0.25 \times B1 + 6.80$ )                                                | 7.60  | 14.30 | 6.30  | 13.00 | 3.80  | 10.50 | 3.13   | 10.00 | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid, as requested<br>by control bit CST2 in the corresponding word<br>in the UPM (MAX = $0.00 \times B1 + 8.00$ )                                                | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50   | 8.00  | ns   |

| B31c | CLKOUT rising edge to $\overline{CS}$ valid, as requested<br>by control bit CST3 in the corresponding word<br>in the UPM (MAX = $0.25 \times B1 + 6.30$ )                                                | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13   | 9.40  | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$ valid as requested<br>by control bit CST1 in the corresponding word<br>in the UPM EBDF = 1<br>(MAX = 0.375 × B1 + 6.6)                                            | 13.30 | 18.00 | 11.30 | 16.00 | 7.60  | 12.30 | 4.69   | 11.30 | ns   |

| B32  | CLKOUT falling edge to $\overline{\text{BS}}$ valid as requested<br>by control bit BST4 in the corresponding word<br>in the UPM (MAX = 0.00 × B1 + 6.00)                                                 | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50   | 6.00  | ns   |

| B32a | CLKOUT falling edge to $\overline{BS}$ valid as requested<br>by control bit BST1 in the corresponding word<br>in the UPM, EBDF = 0<br>(MAX = 0.25 × B1 + 6.80)                                           | 7.60  | 14.30 | 6.30  | 13.00 | 3.80  | 10.50 | 3.13   | 10.00 | ns   |

| B32b | CLKOUT rising edge to $\overline{\text{BS}}$ valid, as requested<br>by control bit BST2 in the corresponding word<br>in the UPM (MAX = $0.00 \times \text{B1} + 8.00$ )                                  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50   | 8.00  | ns   |

| B32c | CLKOUT rising edge to $\overline{\text{BS}}$ valid, as requested<br>by control bit BST3 in the corresponding word<br>in the UPM (MAX = $0.25 \times \text{B1} + 6.80$ )                                  | 7.60  | 14.30 | 6.30  | 13.00 | 3.80  | 10.50 | 3.13   | 10.00 | ns   |

| B32d | CLKOUT falling edge to $\overline{BS}$ valid as requested<br>by control bit BST1 in the corresponding word<br>in the UPM, EBDF = 1<br>(MAX = 0.375 × B1 + 6.60)                                          | 13.30 | 18.00 | 11.30 | 16.00 | 7.60  | 12.30 | 4.49   | 11.30 | ns   |

| B33  | CLKOUT falling edge to $\overline{\text{GPL}}$ valid as<br>requested by control bit GxT4 in the<br>corresponding word in the UPM<br>(MAX = 0.00 × B1 + 6.00)                                             | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50   | 6.00  | ns   |

## Table 10. Bus Operation Timings (continued)

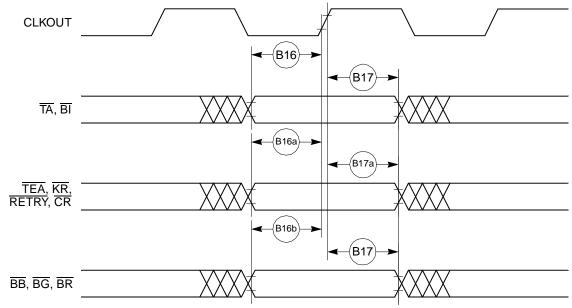

Figure 9 provides the timing for the synchronous input signals.

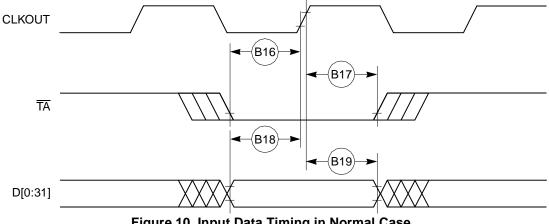

Figure 10 provides normal case timing for input data. It also applies to normal read accesses under the control of the user-programmable machine (UPM) in the memory controller.

Figure 10. Input Data Timing in Normal Case

**Bus Signal Timing**

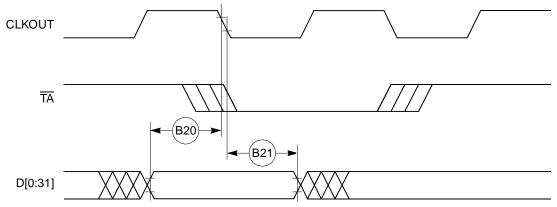

Figure 11 provides the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

Figure 11. Input Data Timing when Controlled by UPM in the Memory Controller and DLT3 = 1

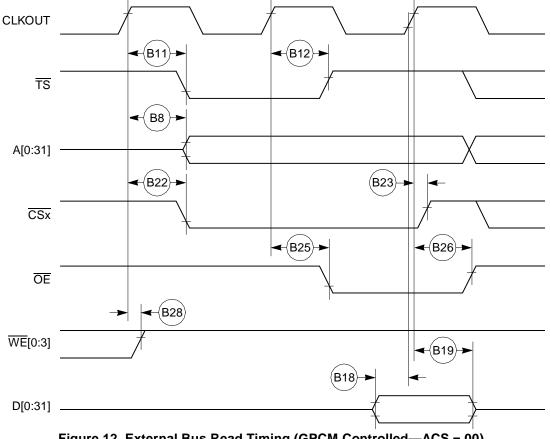

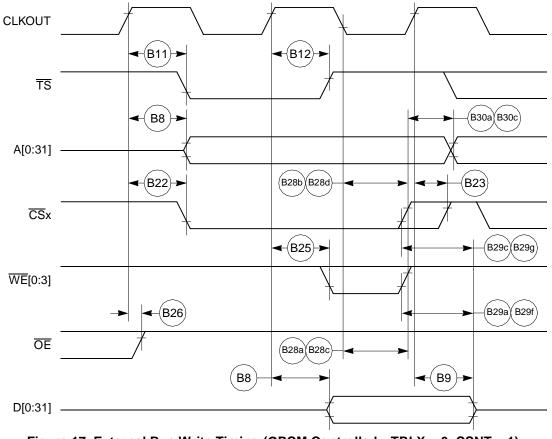

Figure 12 through Figure 15 provide the timing for the external bus read controlled by various GPCM factors.

Figure 12. External Bus Read Timing (GPCM Controlled—ACS = 00)

**Bus Signal Timing**

Figure 17. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 1)

Figure 18. External Bus Write Timing (GPCM Controlled—TRLX = 1, CSNT = 1)

1

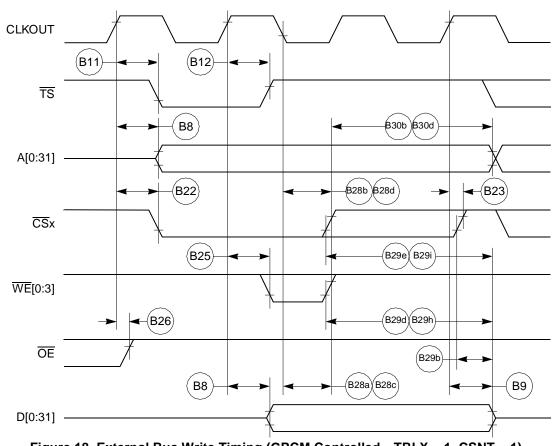

Table 11 provides the interrupt timing for the MPC875/MPC870.

| Table 11. Interrupt Timing |  |

|----------------------------|--|

|----------------------------|--|

| Num | Characteristic <sup>1</sup>                   | All Freq                  | Unit |      |

|-----|-----------------------------------------------|---------------------------|------|------|

|     |                                               | Min                       | Мах  | Unit |

| 139 | IRQx valid to CLKOUT rising edge (setup time) | 6.00                      |      | ns   |

| 140 | IRQx hold time after CLKOUT                   | 2.00                      |      | ns   |

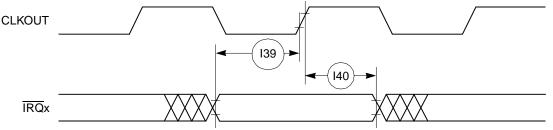

| 141 | IRQx pulse width low                          | 3.00                      |      | ns   |

| 142 | IRQx pulse width high                         | 3.00                      |      | ns   |

| 143 | IRQx edge-to-edge time                        | 4 × T <sub>CLOCKOUT</sub> |      | —    |

The I39 and I40 timings describe the testing conditions under which the IRQ lines are tested when being defined as level sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT. The I41, I42, and I43 timings are specified to allow correct functioning of the IRQ lines detection circuitry and have no direct relation with the total system interrupt latency that the MPC875/MPC870 is able to support.

Figure 25 provides the interrupt detection timing for the external level-sensitive lines.

Figure 25. Interrupt Detection Timing for External Level Sensitive Lines

Figure 26 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 26. Interrupt Detection Timing for External Edge-Sensitive Lines

# 12 IEEE 1149.1 Electrical Specifications

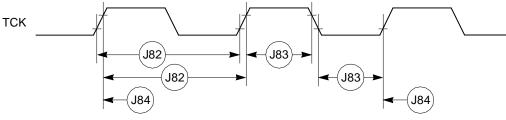

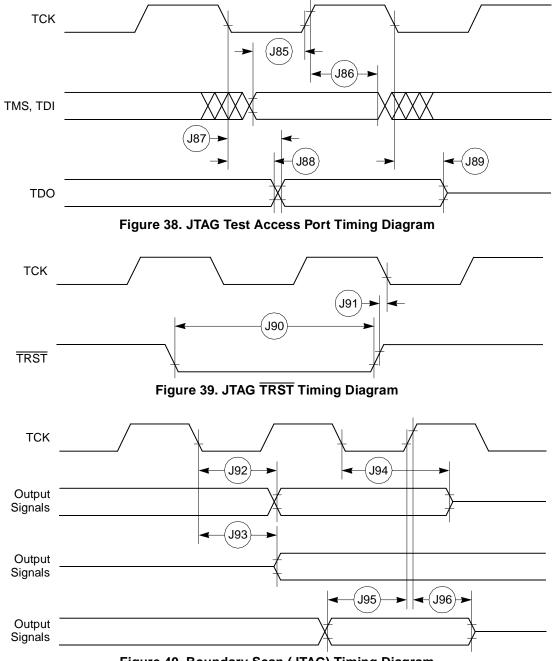

Table 16 provides the JTAG timings for the MPC875/MPC870 shown in Figure 37 through Figure 40.

## Table 16. JTAG Timing

| Num | Characteristic                                         | All Freq | uencies | Unit |

|-----|--------------------------------------------------------|----------|---------|------|

| Num |                                                        | Min      | Мах     | Unit |

| J82 | TCK cycle time                                         | 100.00   | —       | ns   |

| J83 | TCK clock pulse width measured at 1.5 V                | 40.00    | —       | ns   |

| J84 | TCK rise and fall times                                | 0.00     | 10.00   | ns   |

| J85 | TMS, TDI data setup time                               | 5.00     | —       | ns   |

| J86 | TMS, TDI data hold time                                | 25.00    | —       | ns   |

| J87 | TCK low to TDO data valid                              | _        | 27.00   | ns   |

| J88 | TCK low to TDO data invalid                            | 0.00     | —       | ns   |

| J89 | TCK low to TDO high impedance                          | _        | 20.00   | ns   |

| J90 | TRST assert time                                       | 100.00   | —       | ns   |

| J91 | TRST setup time to TCK low                             | 40.00    | —       | ns   |

| J92 | TCK falling edge to output valid                       | _        | 50.00   | ns   |

| J93 | TCK falling edge to output valid out of high impedance | _        | 50.00   | ns   |

| J94 | TCK falling edge to output high impedance              | _        | 50.00   | ns   |

| J95 | Boundary scan input valid to TCK rising edge           | 50.00    | —       | ns   |

| J96 | TCK rising edge to boundary scan input invalid         | 50.00    |         | ns   |

Figure 37. JTAG Test Clock Input Timing

**IEEE 1149.1 Electrical Specifications**

Figure 40. Boundary Scan (JTAG) Timing Diagram

# **13 CPM Electrical Characteristics**

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC875/MPC870.

# **13.1 Port C Interrupt AC Electrical Specifications**

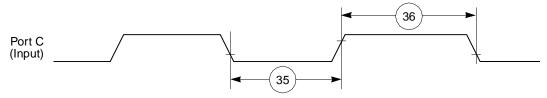

Table 17 provides the timings for Port C interrupts.

| Table | 17. | Port C | Interrupt | Timing |

|-------|-----|--------|-----------|--------|

|-------|-----|--------|-----------|--------|

| Num | um Characteristic -                                    | 33.34 | Unit |      |

|-----|--------------------------------------------------------|-------|------|------|

| Num |                                                        | Min   | Мах  | onit |

| 35  | Port C interrupt pulse width low (edge-triggered mode) | 55    | _    | ns   |

| 36  | Port C interrupt minimum time between active edges     | 55    | _    | ns   |

Figure 41 shows the Port C interrupt detection timing.

Figure 41. Port C Interrupt Detection Timing

## **13.2 IDMA Controller AC Electrical Specifications**

Table 18 provides the IDMA controller timings as shown in Figure 42 through Figure 45.

### Table 18. IDMA Controller Timing

| Num | Characteristic                                                                                          | All Freq | l lmit |      |

|-----|---------------------------------------------------------------------------------------------------------|----------|--------|------|

| num | Characteristic                                                                                          |          | Мах    | Unit |

| 40  | DREQ setup time to clock high                                                                           | 7        | —      | ns   |

| 41  | DREQ hold time from clock high <sup>1</sup>                                                             | TBD      | —      | ns   |

| 42  | SDACK assertion delay from clock high                                                                   | _        | 12     | ns   |

| 43  | SDACK negation delay from clock low                                                                     | _        | 12     | ns   |

| 44  | SDACK negation delay from TA low                                                                        | _        | 20     | ns   |

| 45  | SDACK negation delay from clock high                                                                    | _        | 15     | ns   |

| 46  | $\overline{TA}$ assertion to rising edge of the clock setup time (applies to external $\overline{TA}$ ) | 7        | —      | ns   |

<sup>1</sup> Applies to high-to-low mode (EDM = 1).

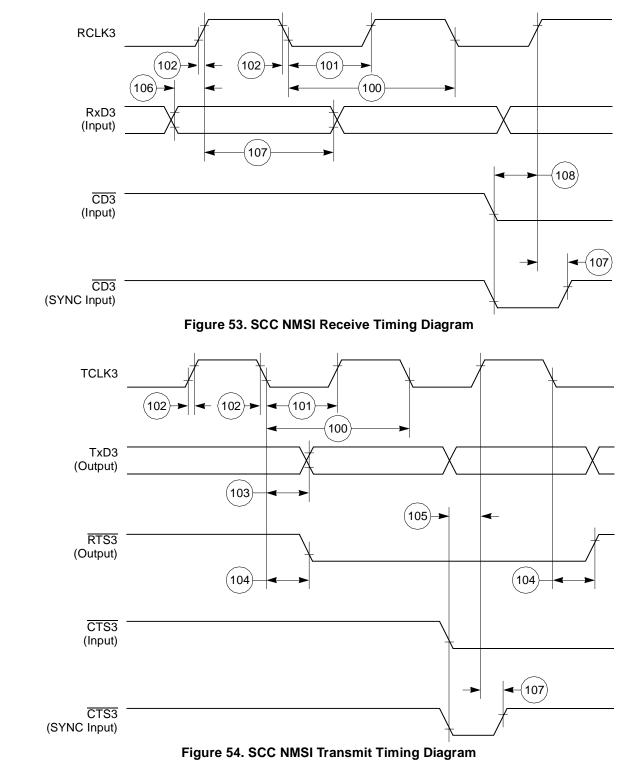

#### SCC in NMSI Mode Electrical Specifications 13.6

Table 22 provides the NMSI external clock timing.

| Num | Characteristic                                       | All Freque    | Unit  |      |

|-----|------------------------------------------------------|---------------|-------|------|

| Num | Characteristic                                       | Min           | Мах   | Onit |

| 100 | RCLK3 and TCLK3 width high <sup>1</sup>              | 1/SYNCCLK     | _     | ns   |

| 101 | RCLK3 and TCLK3 width low                            | 1/SYNCCLK + 5 | —     | ns   |

| 102 | RCLK3 and TCLK3 rise/fall time                       | _             | 15.00 | ns   |

| 103 | TXD3 active delay (from TCLK3 falling edge)          | 0.00          | 50.00 | ns   |

| 104 | RTS3 active/inactive delay (from TCLK3 falling edge) | 0.00          | 50.00 | ns   |

| 105 | CTS3 setup time to TCLK3 rising edge                 | 5.00          | _     | ns   |

| 106 | RXD3 setup time to RCLK3 rising edge                 | 5.00          | _     | ns   |

| 107 | RXD3 hold time from RCLK3 rising edge <sup>2</sup>   | 5.00          | —     | ns   |

| 108 | CD3 setup time to RCLK3 rising edge                  | 5.00          | —     | ns   |

<sup>1</sup> The ratios SYNCCLK/RCLK3 and SYNCCLK/TCLK3 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to CD and CTS hold time when they are used as external SYNC signals.

### Table 23 provides the NMSI internal clock timing.

## Table 23. NMSI Internal Clock Timing

| Num | Characteristic                                       | All Free | Unit      |      |

|-----|------------------------------------------------------|----------|-----------|------|

|     |                                                      | Min      | Мах       | Unit |

| 100 | RCLK3 and TCLK3 frequency <sup>1</sup>               | 0.00     | SYNCCLK/3 | MHz  |

| 102 | RCLK3 and TCLK3 rise/fall time                       | —        | _         | ns   |

| 103 | TXD3 active delay (from TCLK3 falling edge)          | 0.00     | 30.00     | ns   |

| 104 | RTS3 active/inactive delay (from TCLK3 falling edge) | 0.00     | 30.00     | ns   |

| 105 | CTS3 setup time to TCLK3 rising edge                 | 40.00    | _         | ns   |

| 106 | RXD3 setup time to RCLK3 rising edge                 | 40.00    | _         | ns   |

| 107 | RXD3 hold time from RCLK3 rising edge <sup>2</sup>   | 0.00     | —         | ns   |

| 108 | CD3 setup time to RCLK3 rising edge                  | 40.00    | _         | ns   |

The ratios SYNCCLK/RCLK3 and SYNCCLK/TCLK3 must be greater or equal to 3/1.

Also applies to CD and CTS hold time when they are used as external SYNC signals.

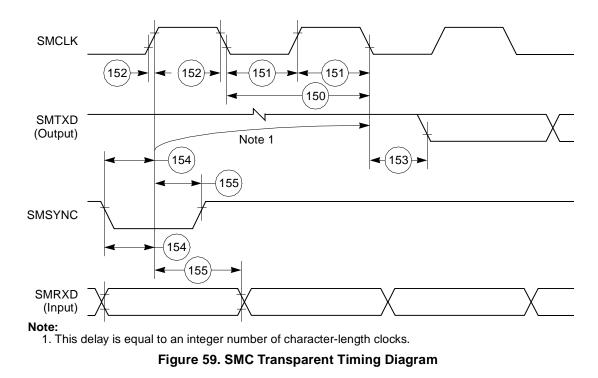

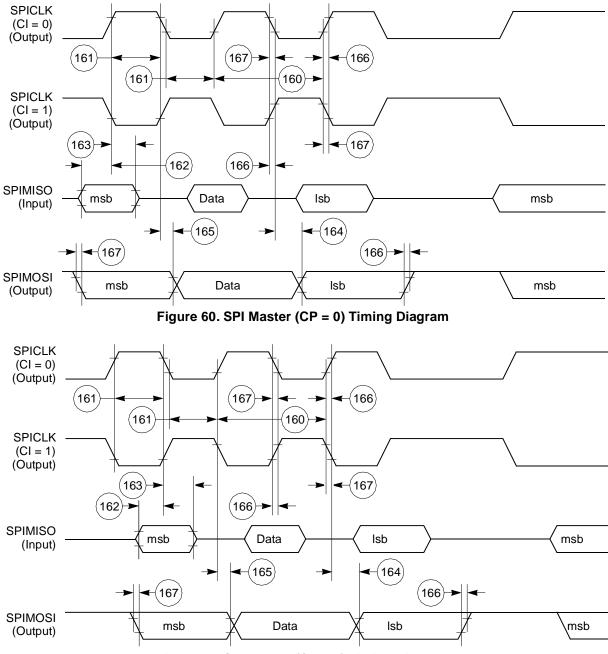

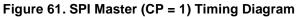

# **13.9 SPI Master AC Electrical Specifications**

Table 26 provides the SPI master timings as shown in Figure 60 and Figure 61.

## Table 26. SPI Master Timing

| Num | Characteristic                      | All Frequencies |      | 11               |

|-----|-------------------------------------|-----------------|------|------------------|

|     |                                     | Min             | Мах  | Unit             |

| 160 | Master cycle time                   | 4               | 1024 | t <sub>cyc</sub> |

| 161 | Master clock (SCK) high or low time | 2               | 512  | t <sub>cyc</sub> |

| 162 | Master data setup time (inputs)     | 15              | —    | ns               |

| 163 | Master data hold time (inputs)      | 0               | —    | ns               |

| 164 | Master data valid (after SCK edge)  | _               | 10   | ns               |

| 165 | Master data hold time (outputs)     | 0               | —    | ns               |

| 166 | Rise time output                    | _               | 15   | ns               |

| 167 | Fall time output                    | -               | 15   | ns               |

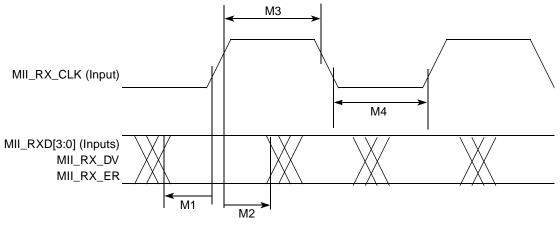

Figure 65 shows MII receive signal timing.

Figure 65. MII Receive Signal Timing Diagram

## 15.2 MII and Reduced MII Transmit Signal Timing

The transmitter functions correctly up to a MII\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_TX\_CLK frequency -1%.

Table 32 provides information on the MII transmit signal timing.

| Table 32. M | III Transmit | Signal Timing |

|-------------|--------------|---------------|

|-------------|--------------|---------------|

| Num      | Characteristic                                                   | Min | Max | Unit              |

|----------|------------------------------------------------------------------|-----|-----|-------------------|

| M5       | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER invalid         | 5   | _   | ns                |

| M6       | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER valid           |     | 25  | ns                |

| M7       | MII_TX_CLK pulse width high                                      | 35% | 65% | MII_TX_CLK period |

| M8       | MII_TX_CLK pulse width low                                       | 35% | 65% | MII_TX_CLK period |

| M20_RMII | RMII_TXD[1:0], RMII_TX_EN to RMII_REFCLK setup                   | 4   | _   | ns                |

| M21_RMII | RMII_TXD[1:0], RMII_TX_EN data hold from RMII_REFCLK rising edge | 2   | _   | ns                |

# **16 Mechanical Data and Ordering Information**

Table 35 identifies the packages and operating frequencies available for the MPC875/MPC870.

| Package Type                                                                                 | Temperature (T <sub>J</sub> ) | Frequency (MHz) | Order Number                                                   |

|----------------------------------------------------------------------------------------------|-------------------------------|-----------------|----------------------------------------------------------------|

| Plastic ball grid array<br>ZT suffix—Leaded<br>VR suffix—Lead-Free are available as needed   | 0°C to 95°C                   | 66              | KMPC875ZT66<br>KMPC870ZT66<br>MPC875ZT66<br>MPC870ZT66         |

|                                                                                              |                               | 80              | KMPC875ZT80<br>KMPC870ZT80<br>MPC875ZT80<br>MPC870ZT80         |

|                                                                                              |                               | 133             | KMPC875ZT133<br>KMPC870ZT133<br>MPC875ZT133<br>MPC870ZT133     |

| Plastic ball grid array<br>CZT suffix—Leaded<br>CVR suffix—Lead-Free are available as needed | -40°C to 100°C                | 66              | KMPC875CZT66<br>KMPC870CZT66<br>MPC875CZT66<br>MPC870CZT66     |

|                                                                                              |                               | 133             | KMPC875CZT133<br>KMPC870CZT133<br>MPC875CZT133<br>MPC870CZT133 |

### Table 35. Available MPC875/MPC870 Packages/Frequencies

Table 36 contains a list of the MPC875/MPC870 input and output signals and shows multiplexing and pin assignments.

| Name                        | Pin Number                                                                                                                                                           | Туре                                         |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| A[0:31]                     | R16, N14, M14, P15, P17, P16, N15, N16, M15, N17, L14, M16,<br>L15, M17, K14, L16, L17, K17, G17, K15, J16, J15, G16, J14, H17,<br>H16, G15, K16, H14, J17, H15, F17 | Bidirectional<br>Three-state (3.3 V only)    |

| TSIZO, REG                  | F16                                                                                                                                                                  | Bidirectional<br>Three-state (3.3 V only)    |

| TSIZ1                       | G14                                                                                                                                                                  | Bidirectional<br>Three-state (3.3 V only)    |

| RD/WR                       | D13                                                                                                                                                                  | Bidirectional<br>Three-state (3.3 V only)    |

| BURST                       | B9                                                                                                                                                                   | Bidirectional<br>Three-state (3.3 V only)    |

| BDIP, GPL_B5                | C13                                                                                                                                                                  | Output                                       |

| TS                          | C11                                                                                                                                                                  | Bidirectional<br>Active pull-up (3.3 V only) |

| TA                          | C12                                                                                                                                                                  | Bidirectional<br>Active pull-up (3.3 V only) |

| TEA                         | B12                                                                                                                                                                  | Open-drain                                   |

| BI                          | B13                                                                                                                                                                  | Bidirectional<br>Active pull-up (3.3 V only) |

| IRQ2, RSV                   | C9                                                                                                                                                                   | Bidirectional<br>Three-state (3.3 V only)    |

| IRQ4, KR, RETRY,<br>SPKROUT | E9                                                                                                                                                                   | Bidirectional<br>Three-state (3.3 V only)    |

| D[0:31]                     | L5, N3, L3, L2, R2, K2, H3, G2, R3, M3, N2, M2, M4, N4, K5, K3, K4, P3, J2, J3, J4, J5, H2, P2, H4, H5, G5, L4, G3, F2, F3, E2                                       | Bidirectional<br>Three-state (3.3 V only)    |

| CR, IRQ3                    | E10                                                                                                                                                                  | Input                                        |

| FRZ, IRQ6                   | B10                                                                                                                                                                  | Bidirectional<br>Three-state (3.3 V only)    |

| BR                          | B11                                                                                                                                                                  | Bidirectional (3.3 V only)                   |

| BG                          | D10                                                                                                                                                                  | Bidirectional (3.3 V only)                   |

| BB                          | C10                                                                                                                                                                  | Bidirectional<br>Active pull-up (3.3 V only) |

| ĪRQ0                        | M6                                                                                                                                                                   | Input (3.3 V only)                           |

| ĪRQ1                        | P5                                                                                                                                                                   | Input (3.3 V only)                           |

| ĪRQ7                        | N5                                                                                                                                                                   | Input (3.3 V only)                           |

| <u>CS</u> [0:5]             | B14, E11, C14, B15, E13, B16                                                                                                                                         | Output                                       |

#### Table 36. Pin Assignments—JEDEC Standard