Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | ARM® Cortex®-M3                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 20MHz                                                                           |

| Connectivity               | CSIO, I²C, UART/USART                                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 37                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 6x12b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | 48-LQFP (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/rochester-electronics/mb9af132kbpmc-g-sne2 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

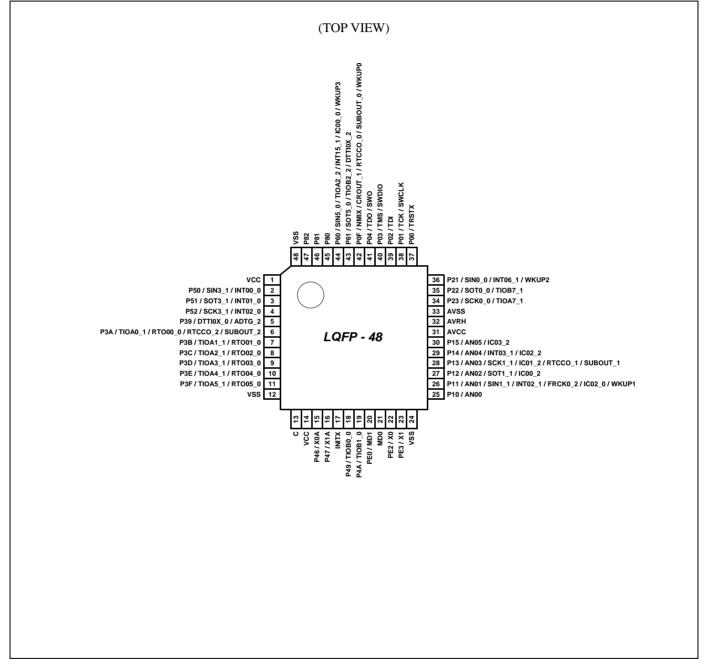

## 3. Pin Assignment

#### FPT-48P-M49

#### Note:

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

|                   | in No             |                    | I/O circuit | Pin state |  |

|-------------------|-------------------|--------------------|-------------|-----------|--|

| LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | Pin name           | type        | type      |  |

|                   |                   | P4C                |             |           |  |

| 25                | -                 | TIOB3_0            | E           | н         |  |

|                   |                   | SCK7_1             |             |           |  |

|                   |                   | (SCL7_1)           |             |           |  |

|                   |                   | P4D                |             |           |  |

| 26                | -                 | TIOB4_0            | E           | Н         |  |

|                   |                   | SOT7_1<br>(SDA7_1) |             |           |  |

|                   |                   | P4E                |             |           |  |

|                   |                   | TIOB5_0            |             |           |  |

| 27                | -                 | <br>INT06_2        | E           | F         |  |

|                   |                   | <br>SIN7_1         |             |           |  |

|                   |                   | <br>PE0            |             |           |  |

| 28                | 20                | MD1                | C           | Р         |  |

| 29                | 21                | MD0                | Н           | D         |  |

|                   |                   | PE2                |             |           |  |

| 30                | 22                | X0                 | Α           | A         |  |

|                   |                   | PE3                |             | 5         |  |

| 31                | 23                | X1                 | — A         | В         |  |

| 32                | 24                | VSS                | -           |           |  |

| 33                | -                 | VCC                | -           |           |  |

| 34                | 25                | P10                | F           | J         |  |

| 54                | 25                | AN00               | Г           | J         |  |

|                   |                   | P11                |             |           |  |

|                   |                   | AN01               |             |           |  |

|                   |                   | SIN1_1             |             |           |  |

| 35                | 26                | INT02_1            | F           | L         |  |

|                   |                   | FRCK0_2            |             |           |  |

|                   |                   | IC02_0             |             |           |  |

|                   |                   | WKUP1              |             |           |  |

|                   |                   | P12                |             |           |  |

|                   |                   | AN02               |             |           |  |

| 36                | 27                | SOT1_1             | F           | J         |  |

|                   |                   | (SDA1_1)           |             |           |  |

|                   |                   | IC00_2             |             |           |  |

|                   |                   | P13                |             |           |  |

|                   |                   | AN03<br>SCK1_1     |             |           |  |

| 37                | 28                | (SCL1_1)           | F           | J         |  |

|                   |                   | IC01_2             | —   ·       | J         |  |

|                   |                   | RTCCO_1            |             |           |  |

|                   |                   | SUBOUT_1           |             |           |  |

| L                 |                   |                    |             |           |  |

| Dim             |          |                            |                   | Pin No            |  |  |

|-----------------|----------|----------------------------|-------------------|-------------------|--|--|

| Pin<br>function | Pin name | Function description       | LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 |  |  |

| GPIO            | P30      |                            | 5                 | -                 |  |  |

|                 | P31      |                            | 6                 | -                 |  |  |

|                 | P32      |                            | 7                 | -                 |  |  |

|                 | P33      |                            | 8                 | -                 |  |  |

|                 | P39      |                            | 9                 | 5                 |  |  |

|                 | P3A      | General-purpose I/O port 3 | 10                | 6                 |  |  |

|                 | P3B      |                            | 11                | 7                 |  |  |

|                 | P3C      |                            | 12                | 8                 |  |  |

|                 | P3D      |                            | 13                | 9                 |  |  |

|                 | P3E      |                            | 14                | 10                |  |  |

|                 | P3F      |                            | 15                | 11                |  |  |

|                 | P46      |                            | 19                | 15                |  |  |

|                 | P47      |                            | 20                | 16                |  |  |

|                 | P49      |                            | 22                | 18                |  |  |

|                 | P4A      | Constal purpase I/O part 4 | 23                | 19                |  |  |

|                 | P4B      | General-purpose I/O port 4 | 24                | -                 |  |  |

|                 | P4C      |                            | 25                | -                 |  |  |

|                 | P4D      |                            | 26                | -                 |  |  |

|                 | P4E      |                            | 27                | -                 |  |  |

|                 | P50      |                            | 2                 | 2                 |  |  |

|                 | P51      | General-purpose I/O port 5 | 3                 | 3                 |  |  |

|                 | P52      |                            | 4                 | 4                 |  |  |

|                 | P60      |                            | 60                | 44                |  |  |

|                 | P61      | General-purpose I/O port 6 | 59                | 43                |  |  |

|                 | P62      |                            | 58                | -                 |  |  |

|                 | P80      |                            | 61                | 45                |  |  |

|                 | P81      | General-purpose I/O port 8 | 62                | 46                |  |  |

|                 | P82      |                            | 63                | 47                |  |  |

|                 | PE0      |                            | 28                | 20                |  |  |

|                 | PE2      | General-purpose I/O port E | 30                | 22                |  |  |

|                 | PE3      |                            | 31                | 23                |  |  |

# 7. Handling Devices

#### Power supply pins

In products with multiple VCC and VSS pins, respective pins at the same potential are interconnected within the device in order to prevent malfunctions such as latch-up. However, all of these pins should be connected externally to the power supply or ground lines in order to reduce electromagnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with each Power supply pins and GND pins of this device at low impedance. It is also advisable that a ceramic capacitor of approximately 0.1  $\mu$ F be connected as a bypass capacitor between each Power supply pins and GND pins, between AVCC pin and AVSS pin near this device.

#### Stabilizing power supply voltage

A malfunction may occur when the power supply voltage fluctuates rapidly even though the fluctuation is within the recommended operating conditions of the VCC power supply voltage. As a rule, with voltage stabilization, suppress the voltage fluctuation so that the fluctuation in VCC ripple (peak-to-peak value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the VCC value in the recommended operating conditions, and the transient fluctuation rate does not exceed 0.1 V/µs when there is a momentary fluctuation on switching the power supply.

#### Crystal oscillator circuit

Noise near the X0/X1 and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1, X0A/X1A pins, the crystal oscillator, and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0/X1 and X0A/X1A pins are surrounded by ground plane as this is expected to produce stable operation.

Evaluate oscillation of your using crystal oscillator by your mount board.

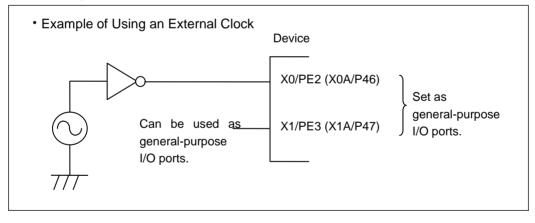

#### Using an external clock

To use the external clock, set general-purpose I/O ports to input the clock to X0/PE2 and X0A/P46 pins.

#### Handling when using Multi-function serial pin as I<sup>2</sup>C pin

If it is using the Multi-function serial pin as I<sup>2</sup>C pins, P-ch transistor of digital output is always disable. However, I<sup>2</sup>C pins need to keep the electrical characteristic like other pins and not to connect to external I<sup>2</sup>C bus system with power OFF.

## 11. Pin Status in Each CPU State

The terms used for pin status have the following meanings.

$\blacksquare INITX = 0$

This is the period when the INITX pin is the L level.

■INITX = 1

This is the period when the INITX pin is the H level.

■SPL = 0

This is the status that standby pin level setting bit (SPL) in standby mode control register (STB\_CTL) is set to 0.

■SPL=1

This is the status that standby pin level setting bit (SPL) in standby mode control register (STB\_CTL) is set to 1.

■Input enabled

Indicates that the input function can be used.

■Internal input fixed at 0

This is the status that the input function cannot be used. Internal input is fixed at L.

■Hi-Z

Indicates that the pin drive transistor is disabled and the pin is put in the Hi-Z state.

Setting disabled

Indicates that the setting is disabled.

■Maintain previous state

Maintains the state that was immediately prior to entering the current mode. If a built-in peripheral function is operating, the output follows the peripheral function. If the pin is being used as a port, that output is maintained.

■Analog input is enabled

Indicates that the analog input is enabled.

■Trace output

Indicates that the trace function can be used.

■GPIO selected

In Deep Standby mode, pins switch to the general-purpose I/O port.

| Pin status type | Function<br>group                            | Power-o<br>n reset or<br>low<br>voltage<br>detection<br>state | INITX<br>input<br>state                               | Device<br>internal<br>reset<br>state                  | ernal Sleep RTC mode, mode or Deep state state state  |                                                                                                                                                                |                                                                                                                          |                                                                                                                                                                | or Deep<br>Stop mode                                                                                                     | Return<br>from<br>Deep<br>Standby<br>mode<br>state                                                                 |

|-----------------|----------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Pin sta         | group                                        | Power<br>supply<br>unstable                                   | Power<br>sta                                          | ble                                                   | Power<br>supply<br>stable                             | sta                                                                                                                                                            | supply<br>ble                                                                                                            | Power supply stable                                                                                                                                            |                                                                                                                          | Power<br>supply<br>stable                                                                                          |

|                 |                                              | -                                                             | INITX = 0                                             | INITX = 1                                             | INITX = 1                                             | INIT<br>SPL = 0                                                                                                                                                | X = 1<br>SPL = 1                                                                                                         | INITX<br>SPL = 0                                                                                                                                               | X = 1<br>SPL = 1                                                                                                         | INITX = 1                                                                                                          |

|                 | Analog<br>input<br>selected                  | Hi-Z                                                          | Hi-Z /<br>Internal<br>input fixed<br>at 0 /<br>Analog                                                                                                          | Hi-Z /<br>Internal                                                                                                       | Hi-Z /<br>Internal                                                                                                                                             | Hi-Z /<br>Internal<br>input fixed<br>at 0 /<br>Analog                                                                    | Hi-Z /<br>Internal<br>input fixed<br>at 0 /<br>Analog                                                              |

|                 |                                              |                                                               | input<br>enabled                                      | input<br>enabled                                      | input<br>enabled                                      | input<br>enabled                                                                                                                                               | input<br>enabled<br>Hi-Z /                                                                                               | input<br>enabled                                                                                                                                               | input<br>enabled<br>Hi-Z /                                                                                               | input<br>enabled                                                                                                   |

| L               | WKUP<br>enabled                              |                                                               |                                                       |                                                       |                                                       |                                                                                                                                                                | Internal<br>input fixed<br>at 0                                                                                          | WKUP<br>input<br>enabled                                                                                                                                       | WKUP<br>input<br>enabled                                                                                                 |                                                                                                                    |

|                 | External<br>interrupt<br>enabled<br>selected | disabled disabled disabled previous previ                     | Maintain<br>previous                                  | Maintain<br>previous<br>state                         | GPIO                                                  | Hi-Z /                                                                                                                                                         | GPIO<br>selected                                                                                                         |                                                                                                                                                                |                                                                                                                          |                                                                                                                    |

|                 | Resource<br>other than<br>above<br>selected  | alcabioa                                                      | alcabioa                                              | state state state                                     | state                                                 | Hi-Z /<br>Internal<br>input fixed                                                                                                                              | selected                                                                                                                 | Internal<br>input fixed<br>at 0                                                                                                                                |                                                                                                                          |                                                                                                                    |

|                 | GPIO<br>selected                             |                                                               |                                                       |                                                       |                                                       |                                                                                                                                                                | at 0                                                                                                                     | Maintain<br>previous<br>state                                                                                                                                  |                                                                                                                          | Maintain<br>previous<br>state                                                                                      |

|                 | Sub<br>crystal<br>oscillator<br>input pin    | Input<br>enabled                                              | Input<br>enabled                                      | Input<br>enabled                                      | Input<br>enabled                                      | Input<br>enabled                                                                                                                                               | Input<br>enabled                                                                                                         | Input<br>enabled                                                                                                                                               | Input<br>enabled                                                                                                         | Input<br>enabled                                                                                                   |

| М               | External<br>sub clock<br>input<br>selected   | Setting<br>disabled                                           | Setting<br>disabled                                   | Setting<br>disabled                                   | Maintain<br>previous<br>state                         | Maintain<br>previous<br>state /<br>When<br>oscillation<br>stop* <sup>2</sup> ,<br>output<br>maintain<br>previous<br>state /<br>Internal<br>input fixed<br>at 0 | Hi-Z /<br>Input<br>enabled /<br>When<br>oscillation<br>stop* <sup>2</sup> ,<br>Hi-Z /<br>Internal<br>input fixed<br>at 0 | Maintain<br>previous<br>state /<br>When<br>oscillation<br>stop* <sup>2</sup> ,<br>output<br>maintain<br>previous<br>state /<br>Internal<br>input fixed<br>at 0 | Hi-Z /<br>Input<br>enabled /<br>When<br>oscillation<br>stop* <sup>2</sup> ,<br>Hi-Z /<br>Internal<br>input fixed<br>at 0 | Maintain<br>previous<br>state /<br>When<br>Return<br>from<br>Deep<br>Stand-by<br>STOP<br>mode,<br>GPIO<br>selected |

|                 | GPIO<br>selected                             | Setting<br>disabled                                           | Setting<br>disabled                                   | Setting<br>disabled                                   | Maintain<br>previous<br>state                         | Output<br>maintain<br>previous<br>state /<br>Internal<br>input fixed<br>at 0                                                                                   | Hi-Z /<br>Internal<br>input fixed<br>at 0                                                                                | Output<br>maintain<br>previous<br>state /<br>Internal<br>input fixed<br>at 0                                                                                   | Hi-Z /<br>Internal<br>input fixed<br>at 0                                                                                | Maintain<br>previous<br>state                                                                                      |

# **12. Electrical Characteristics**

## 12.1 Absolute Maximum Ratings

| Parameter                              | Symbol             | F                     | Rating                              | Unit | Remarks     |

|----------------------------------------|--------------------|-----------------------|-------------------------------------|------|-------------|

|                                        | Symbol             | Min                   | Max                                 | Unit | Rellia KS   |

| Power supply voltage*1,*2              | V <sub>cc</sub>    | V <sub>SS</sub> - 0.5 | V <sub>SS</sub> + 6.5               | V    |             |

| Analog power supply voltage*1,*3       | AV <sub>CC</sub>   | V <sub>SS</sub> - 0.5 | V <sub>SS</sub> + 6.5               | V    |             |

| Analog reference voltage*1,*3          | AVRH               | V <sub>SS</sub> - 0.5 | V <sub>SS</sub> + 6.5               | V    |             |

| Input voltage*1                        | VI                 | V <sub>SS</sub> - 0.5 | V <sub>CC</sub> + 0.5<br>(≤ 6.5 V)  | V    |             |

|                                        |                    | V <sub>SS</sub> - 0.5 | V <sub>SS</sub> + 6.5               | V    | 5V tolerant |

| Analog pin input voltage*1             | VIA                | V <sub>SS</sub> - 0.5 | AV <sub>CC</sub> + 0.5<br>(≤ 6.5 V) | V    |             |

| Output voltage*1                       | Vo                 | V <sub>SS</sub> - 0.5 | V <sub>CC</sub> + 0.5<br>(≤ 6.5 V)  | V    |             |

| L level maximum output current*4       | IOL                | -                     | 10                                  | mA   |             |

| L level average output current*5       | I <sub>OLAV</sub>  | -                     | 4                                   | mA   |             |

| L level total maximum output current   | ∑I <sub>OL</sub>   | -                     | 60                                  | mA   |             |

| L level total average output current*6 | ∑I <sub>OLAV</sub> | -                     | 30                                  | mA   |             |

| H level maximum output current*4       | I <sub>OH</sub>    | -                     | -10                                 | mA   |             |

| H level average output current*5       | I <sub>OHAV</sub>  | -                     | - 4                                 | mA   |             |

| H level total maximum output current   | ∑I <sub>ОН</sub>   | -                     | -60                                 | mA   |             |

| H level total average output current*6 | ∑I <sub>OHAV</sub> | -                     | -30                                 | mA   |             |

| Power consumption                      | PD                 | -                     | 400                                 | mW   |             |

| Storage temperature                    | T <sub>STG</sub>   | - 55                  | + 150                               | °C   |             |

\*1: These parameters are based on the condition that  $V_{SS} = AV_{SS} = 0.0$  V.

\*2: V<sub>CC</sub> must not drop below V<sub>SS</sub> - 0.5 V.

- \*3: Be careful not to exceed  $V_{CC}$  + 0.5 V, for example, when the power is turned on.

- \*4: The maximum output current is defined as the value of the peak current flowing through any one of the corresponding pins.

- \*5: The average output current is defined as the average current value flowing through any one of the corresponding pins for a 100 ms period.

- \*6: The total average output current is defined as the average current value flowing through all of corresponding pins for a 100 ms.

#### WARNING

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## **12.4 AC Characteristics**

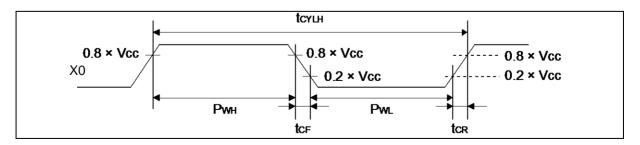

#### 12.4.1 Main Clock Input Characteristics

$(V_{CC} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 85^{\circ}C)$

| Deremeter                              | Symbol                               | Pin  | Conditions              | Va   | lue | Unit | Domorko                      |

|----------------------------------------|--------------------------------------|------|-------------------------|------|-----|------|------------------------------|

| Parameter                              | Symbol                               | name | Conditions              | Min  | Max | Unit | Remarks                      |

|                                        |                                      |      | V <sub>CC</sub> ≥ 2.0 V | 4    | 20  | MHz  | When crystal oscillator is   |

| 1                                      | 4                                    |      | V <sub>CC</sub> < 2.0 V | 4    | 4   | MHz  | connected                    |

| Input frequency                        | f <sub>CH</sub>                      |      | V <sub>CC</sub> ≥ 4.5 V | 4    | 20  | MHz  | When using external          |

|                                        |                                      |      | $V_{CC} < 4.5 V$        | 4    | 16  | MHz  | clock                        |

|                                        | 4                                    | X0,  | V <sub>CC</sub> ≥ 4.5 V | 50   | 250 | ns   | When using external          |

| Input clock cycle                      | t <sub>CYLH</sub>                    | X1   | V <sub>CC</sub> < 4.5 V | 62.5 | 250 | ns   | clock                        |

| Input clock pulse width                | -                                    |      | Рwн/tсү∟н,<br>Рw∟/tсү∟н | 45   | 55  | %    | When using external<br>clock |

| Input clock rise<br>time and fall time | t <sub>CF</sub> ,<br>t <sub>CR</sub> |      | -                       | -    | 5   | ns   | When using external<br>clock |

|                                        | f <sub>CM</sub>                      | -    | -                       | -    | 20  | MHz  | Master clock                 |

|                                        | f <sub>CC</sub>                      | -    | -                       | -    | 20  | MHz  | Base clock (HCLK/FCLK)       |

| Internal operating clock*1             | f <sub>CP0</sub>                     | -    | -                       | -    | 20  | MHz  | APB0 bus clock* <sup>2</sup> |

| frequency                              | f <sub>CP1</sub>                     | -    | -                       | -    | 20  | MHz  | APB1 bus clock*2             |

|                                        | f <sub>CP2</sub>                     | -    | -                       | -    | 20  | MHz  | APB2 bus clock*2             |

|                                        | t <sub>cycc</sub>                    | -    | -                       | 50   | -   | ns   | Base clock (HCLK/FCLK)       |

| Internal operating                     | t <sub>CYCP0</sub>                   | -    | -                       | 50   | -   | ns   | APB0 bus clock*2             |

| clock* <sup>1</sup><br>cycle time      | t <sub>CYCP1</sub>                   | -    | -                       | 50   | -   | ns   | APB1 bus clock*2             |

|                                        | t <sub>CYCP2</sub>                   | -    | -                       | 50   | -   | ns   | APB2 bus clock*2             |

\*1: For more information about each internal operating clock, see Chapter 2-1: Clock in FM3 Family Peripheral Manual.

\*2: For about each APB bus which each peripheral is connected to, see Block Diagram in this data sheet.

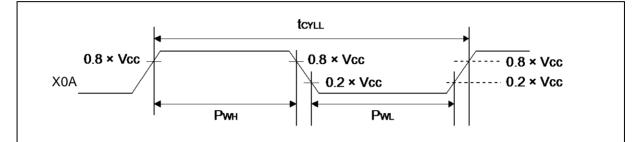

12.4.2 Sub Clock Input Characteristics

|                            |                        |                       |                         |         |        | (V <sub>CC</sub> | = 1.8V | to 5.5V, $V_{SS} = 0V$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$ ) |

|----------------------------|------------------------|-----------------------|-------------------------|---------|--------|------------------|--------|-------------------------------------------------------------------|

| Parameter Symbol           | Symbol                 | Pin                   | Condition               |         | Value  |                  | Unit   | Demeska                                                           |

|                            | name                   | me s Min Typ Max Onit |                         | Remarks |        |                  |        |                                                                   |

| Input fraguanay            | land the supervisit of |                       | -                       | -       | 32.768 | -                | kHz    | When crystal oscillator is connected                              |

| Input frequency            | f <sub>CL</sub>        |                       | -                       | 32      | -      | 100              | kHz    | When using external clock                                         |

| Input clock cycle          | t <sub>CYLL</sub>      | X0A,<br>X1A           | -                       | 10      | -      | 31.25            | μs     | When using external clock                                         |

| Input clock pulse<br>width | -                      |                       | Pwh/tcyll,<br>Pwl/tcyll | 45      | -      | 55               | %      | When using external clock                                         |

#### **Built-in High-speed CR**

$(V_{CC} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 85^{\circ}C)$

| Parameter                       | Symbol            |                            | Conditions —                         |      | Value |      | Unit | Remarks                     |  |

|---------------------------------|-------------------|----------------------------|--------------------------------------|------|-------|------|------|-----------------------------|--|

| Farameter                       | Symbol            |                            |                                      |      | Тур   | Max  | Unit |                             |  |

|                                 |                   | V <sub>CC</sub> ≥<br>2.2 V | T <sub>A</sub> = + 25°C              | 3.92 | 4     | 4.08 |      |                             |  |

|                                 |                   |                            | T <sub>A</sub> =<br>- 40°C to + 85°C | 3.8  | 4     | 4.2  | MHz  | When trimming* <sup>1</sup> |  |

|                                 | 4                 |                            | T <sub>A</sub> =<br>- 40°C to + 85°C | 2.3  | -     | 7.03 |      | When not trimming           |  |

| Clock frequency                 | f <sub>CRH</sub>  | V <sub>CC</sub> <<br>2.2 V | $T_{A} = + 25^{\circ}C$              | 3.4  | 4     | 4.6  |      | When trimming* <sup>1</sup> |  |

|                                 |                   |                            | T <sub>A</sub> =<br>- 40°C to + 85°C | 3.16 | 4     | 4.84 | MHz  |                             |  |

|                                 |                   |                            | T <sub>A</sub> =<br>- 40°C to + 85°C | 2.3  | -     | 7.03 |      | When not trimming           |  |

| Frequency<br>stabilization time | t <sub>CRWT</sub> | -                          |                                      | -    | -     | 10   | μs   | *2                          |  |

\*1: In the case of using the values in CR trimming area of Flash memory at shipment for frequency trimming.

\*2: This is the time to stabilize the frequency of High-speed CR clock after setting trimming value. This period is able to use High-speed CR clock as source clock.

## **Built-in Low-speed CR**

## (V\_{CC} = 1.8V to 5.5V, V\_{SS} = 0V, T\_A = -40^{\circ}C to + 85°C)

| Parameter       | Symbol           | Conditions |     | Value |     | Unit | Remarks  |  |

|-----------------|------------------|------------|-----|-------|-----|------|----------|--|

| Farameter       | Symbol           | Conditions | Min | Тур   | Max | Unit | Reliains |  |

| Clock frequency | f <sub>CRL</sub> | -          | 50  | 100   | 150 | kHz  |          |  |

#### 12.4.6 Reset Input Characteristics

$(V_{CC} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 85^{\circ}C)$

| Parameter                           | Symbol Pin               |      | Conditions | Va  | alue | Unit                       | Remarks                |  |

|-------------------------------------|--------------------------|------|------------|-----|------|----------------------------|------------------------|--|

| Parameter Symbol                    |                          | name |            | Min | Max  |                            |                        |  |

| Reset input time t <sub>INITX</sub> | t <sub>INITX</sub> INITX |      |            | 500 | -    | ns                         |                        |  |

|                                     |                          | -    | 1.5        | -   | ms   | When RTC mode or Stop mode |                        |  |

|                                     |                          |      |            | 1.5 | -    | ms                         | When Deep Standby mode |  |

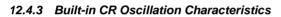

### 12.4.7 Power-on Reset Timing

$(V_{CC} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 85^{\circ}C)$

| Parameter                              | Symbol            | Pin  | Value |      |      | Unit | Remarks            |

|----------------------------------------|-------------------|------|-------|------|------|------|--------------------|

| Faialletei                             | Symbol            | name | Min   | Тур  | Мах  | onit | Kemarks            |

| Power supply rising time               | dV/dt             |      | 0.1   | -    | -    | V/ms |                    |

| Power supply shut down time            | t <sub>OFF</sub>  |      | 1     | -    | -    | ms   |                    |

| Reset release voltage                  | Vdeth             |      | 1.44  | 1.60 | 1.76 | V    | When voltage rises |

| Reset detection voltage                | V <sub>DETL</sub> | VCC  | 1.39  | 1.55 | 1.71 | V    | When voltage drops |

| Time until releasing<br>Power-on reset | t <sub>PRT</sub>  |      | 0.46  | -    | 11.4 | ms   | dV/dt ≥ 0.1mV/µs   |

| Reset detection delay time             | t <sub>OFFD</sub> |      | -     | -    | 0.4  | ms   | dV/dt ≥ -0.04mV/µs |

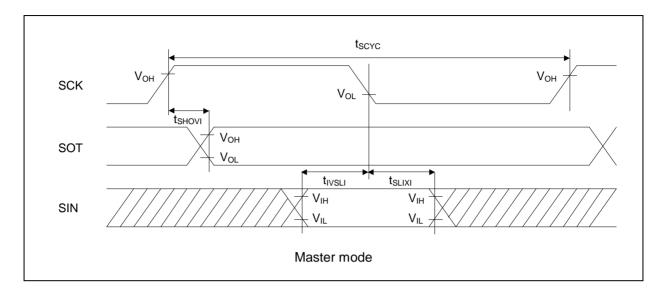

## 12.4.9 CSIO/UART Timing

### CSIO (SPI = 0, SCINV = 0)

|                                    | $\lambda = - \lambda = - \lambda$        | 4000 ( 0500)                        |

|------------------------------------|------------------------------------------|-------------------------------------|

| $(V_{CC} = 1.8V \text{ to } 5.5V)$ | , V <sub>SS</sub> = OV, T <sub>A</sub> = | $-40^{\circ}$ C to $+85^{\circ}$ C) |

|                                                                                                |                    | Dim           |               | V (27)                    |     | 2.7 V ≤                   |     | N SAEN                  |                                      |      |

|------------------------------------------------------------------------------------------------|--------------------|---------------|---------------|---------------------------|-----|---------------------------|-----|-------------------------|--------------------------------------|------|

| Parameter                                                                                      | Symbol             | Pin<br>name   | Conditions    | V <sub>CC</sub> < 2.7 V   |     | V <sub>CC</sub> < 4.5 V   |     | V <sub>cc</sub> ≥ 4.5 V |                                      | Unit |

|                                                                                                |                    |               |               | Min                       | Max | Min                       | Max | Min                     | Max                                  |      |

| Serial clock cycle<br>time                                                                     | tscyc              | SCKx          |               | 4t <sub>CYCP</sub>        | -   | 4t <sub>CYCP</sub>        | -   | 4t <sub>CYCP</sub>      | -                                    | ns   |

| $\begin{array}{l} SCK \downarrow \to SOT \\ delay time \end{array}$                            | t <sub>SLOVI</sub> | SCKx,<br>SOTx | Masterressele | -40                       | +40 | -30                       | +30 | -20                     | +20                                  | ns   |

| $\begin{array}{l} \text{SIN} \rightarrow \text{SCK} \uparrow \\ \text{setup time} \end{array}$ | tıvs∺ı             | SCKx,<br>SINx | Master mode   | 75                        | -   | 50                        | -   | 30                      | -                                    | ns   |

| $\begin{array}{l} SCK \uparrow \to SIN \\ hold time \end{array}$                               | t <sub>SHIXI</sub> | SCKx,<br>SINx |               | 0                         | -   | 0                         | -   | 0                       | -                                    | ns   |

| Serial clock L<br>pulse width                                                                  | t <sub>SLSH</sub>  | SCKx          |               | 2t <sub>CYCP</sub> - 10   | -   | 2t <sub>CYCP</sub> - 10   | -   | 2t <sub>CYCP</sub> - 10 | -                                    | ns   |

| Serial clock H<br>pulse width                                                                  | t <sub>SHSL</sub>  | SCKx          |               | t <sub>CYCP</sub> +<br>10 | -   | t <sub>CYCP</sub> +<br>10 | -   | t <sub>CYCP</sub> + 10  | -                                    | ns   |

| $\begin{array}{l} SCK \downarrow \to SOT \\ delay \ time \end{array}$                          | t <sub>SLOVE</sub> | SCKx,<br>SOTx |               | -                         | 75  | -                         | 50  | -                       | 30* <sup>1</sup><br>40* <sup>2</sup> | ns   |

| $\begin{array}{l} \text{SIN} \rightarrow \text{SCK} \uparrow \\ \text{setup time} \end{array}$ | t <sub>IVSHE</sub> | SCKx,<br>SINx | Slave mode    | 10                        | -   | 10                        | -   | 10                      | -                                    | ns   |

| $\begin{array}{l} SCK \uparrow \to SIN \\ hold time \end{array}$                               | t <sub>SHIXE</sub> | SCKx,<br>SINx |               | 20                        | -   | 20                        | -   | 20                      | -                                    | ns   |

| SCK falling time                                                                               | t <sub>F</sub>     | SCKx          |               | -                         | 5   | -                         | 5   | -                       | 5                                    | ns   |

| SCK rising time                                                                                | t <sub>R</sub>     | SCKx          |               | -                         | 5   | -                         | 5   | -                       | 5                                    | ns   |

\*1 When PZR = 0.

\*2 When PZR = 1.

Notes:

- The above characteristics apply to clock synchronous mode.

- $t_{CYCP}$  indicates the APB bus clock cycle time. About the APB bus number which Multi-function serial is connected to, see Block Diagram in this data sheet.

- These characteristics only guarantee the same relocate port number. For example, the combination of SCKx\_0 and SOTx\_1 is not guaranteed.

- When the external load capacitance  $C_L = 50 \text{ pF}$ .

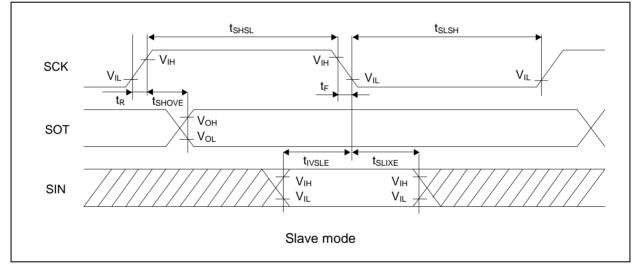

## CSIO (SPI = 0, SCINV = 1)

| Parameter                                                                                        | Symbol             | Pin<br>name   | Conditions  | V <sub>cc</sub> < 2.7 V    |     | 2.7 V ≤<br>V <sub>CC</sub> < 4.5 V |     | V <sub>CC</sub> ≥ 4.5 V    |                                      | Unit |

|--------------------------------------------------------------------------------------------------|--------------------|---------------|-------------|----------------------------|-----|------------------------------------|-----|----------------------------|--------------------------------------|------|

|                                                                                                  | _                  | name          |             | Min                        | Max | Min                                | Max | Min                        | Max                                  |      |

| Serial clock cycle time                                                                          | t <sub>SCYC</sub>  | SCKx          |             | 4t <sub>CYCP</sub>         | -   | 4t <sub>CYCP</sub>                 | -   | 4t <sub>CYCP</sub>         | -                                    | ns   |

| $\begin{array}{l} SCK \uparrow \to SOT \\ delay time \end{array}$                                | t <sub>SHOVI</sub> | SCKx,<br>SOTx |             | -40                        | +40 | -30                                | +30 | -20                        | +20                                  | ns   |

| $\begin{array}{l} \text{SIN} \rightarrow \text{SCK} \downarrow \\ \text{setup time} \end{array}$ | t <sub>IVSLI</sub> | SCKx,<br>SINx | Master mode | 75                         | -   | 50                                 | -   | 30                         | -                                    | ns   |

| $SCK \downarrow \rightarrow SIN$<br>hold time                                                    | t <sub>SLIXI</sub> | SCKx,<br>SINx |             | 0                          | -   | 0                                  | -   | 0                          | -                                    | ns   |

| Serial clock L<br>pulse width                                                                    | t <sub>SLSH</sub>  | SCKx          |             | 2t <sub>CYCP</sub><br>- 10 | -   | 2t <sub>CYCP</sub><br>- 10         | -   | 2t <sub>CYCP</sub><br>- 10 | -                                    | ns   |

| Serial clock H<br>pulse width                                                                    | t <sub>SHSL</sub>  | SCKx          |             | t <sub>СҮСР</sub> +<br>10  | -   | t <sub>СҮСР</sub><br>+ 10          | -   | t <sub>CYCP</sub><br>+ 10  | -                                    | ns   |

| $\begin{array}{l} SCK \uparrow \to SOT \\ delay time \end{array}$                                | t <sub>SHOVE</sub> | SCKx,<br>SOTx |             | -                          | 75  | -                                  | 50  | -                          | 30* <sup>1</sup><br>40* <sup>2</sup> | ns   |

| $\begin{array}{l} \text{SIN} \rightarrow \text{SCK} \downarrow \\ \text{setup time} \end{array}$ | t <sub>IVSLE</sub> | SCKx,<br>SINx | Slave mode  | 10                         | -   | 10                                 | -   | 10                         | -                                    | ns   |

| $\begin{array}{l} SCK \downarrow \to SIN \\ hold time \end{array}$                               | t <sub>SLIXE</sub> | SCKx,<br>SINx |             | 20                         | -   | 20                                 | -   | 20                         | -                                    | ns   |

| SCK falling time                                                                                 | t <sub>F</sub>     | SCKx          |             | -                          | 5   | -                                  | 5   | -                          | 5                                    | ns   |

| SCK rising time                                                                                  | t <sub>R</sub>     | SCKx          |             | -                          | 5   | -                                  | 5   | -                          | 5                                    | ns   |

$(V_{CC} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 85^{\circ}C)$

\*1 When PZR = 0.

\*2 When PZR = 1.

Notes:

• The above characteristics apply to clock synchronous mode.

t<sub>CYCP</sub> indicates the APB bus clock cycle time.

About the APB bus number which Multi-function serial is connected to, see Block Diagram in this data sheet

- These characteristics only guarantee the same relocate port number. For example, the combination of SCKx\_0 and SOTx\_1 is not guaranteed.

- When the external load capacitance  $C_L = 50 \text{ pF}$ .

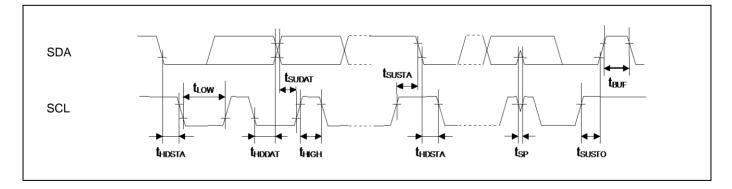

## 12.4.11 <sup>2</sup>C Timing

|                                                                                    |                    | 1                         |                        | (100 = 1.01 to 0.01, 19 |                        |                   |      |         |  |

|------------------------------------------------------------------------------------|--------------------|---------------------------|------------------------|-------------------------|------------------------|-------------------|------|---------|--|

| Parameter                                                                          | Symbol             | Conditions                | Standard-mode          |                         | Fast-mode              |                   | Unit | Remarks |  |

| i di dificici                                                                      |                    |                           | Min                    | Max                     | Min                    | Max               | Onic | Remarko |  |

| SCL clock frequency                                                                | f <sub>SCL</sub>   |                           | 0                      | 100                     | 0                      | 400               | kHz  |         |  |

| (Repeated) START condition hold time SDA $\downarrow \rightarrow$ SCL $\downarrow$ | t <sub>HDSTA</sub> |                           | 4.0                    | -                       | 0.6                    | -                 | μs   |         |  |

| SCL clock L width                                                                  | t <sub>LOW</sub>   |                           | 4.7                    | -                       | 1.3                    | -                 | μs   |         |  |

| SCL clock H width                                                                  | t <sub>HIGH</sub>  |                           | 4.0                    | -                       | 0.6                    | -                 | μs   |         |  |

| (Repeated) START condition setup time SCL $\uparrow \rightarrow$ SDA $\downarrow$  | t <sub>susta</sub> | C <sub>L</sub> = 50 pF,   | 4.7                    | -                       | 0.6                    | -                 | μs   |         |  |

| Data hold time SCL $\downarrow \rightarrow$ SDA $\downarrow \uparrow$              | t <sub>HDDAT</sub> | $R = (V_{P}/I_{OL})^{*1}$ | 0                      | 3.45* <sup>2</sup>      | 0                      | 0.9* <sup>3</sup> | μs   |         |  |

| Data setup time SDA $\downarrow \uparrow \rightarrow$ SCL $\uparrow$               | t <sub>sudat</sub> |                           | 250                    | -                       | 100                    | -                 | ns   |         |  |

| STOP condition setup time SCL $\uparrow \rightarrow$ SDA $\uparrow$                | t <sub>susto</sub> |                           | 4.0                    | -                       | 0.6                    | -                 | μs   |         |  |

| Bus free time between<br>STOP condition and<br>START condition                     | t <sub>BUF</sub>   |                           | 4.7                    | -                       | 1.3                    | -                 | μs   |         |  |

| Noise filter                                                                       | t <sub>SP</sub>    | -                         | 2 t <sub>CYCP</sub> *4 | -                       | 2 t <sub>CYCP</sub> *4 | -                 | ns   |         |  |

\*1: R and C<sub>L</sub> represent the pull-up resistor and load capacitance of the SCL and SDA lines, respectively. V<sub>P</sub> indicates the power supply voltage of the pull-up resistor and I<sub>OL</sub> indicates V<sub>OL</sub> guaranteed current.

\*2: The maximum t<sub>HDDAT</sub> must satisfy that it does not extend at least L period (t<sub>LOW</sub>) of device's SCL signal.

- \*3: A Fast-mode I<sup>2</sup>C bus device can be used on a Standard-mode I<sup>2</sup>C bus system as long as the device satisfies the requirement of  $t_{SUDAT} \ge 250$  ns.

- \*4: t<sub>CYCP</sub> is the APB bus clock cycle time.

About the APB bus number which  $I^2C$  is connected to, see Block Diagram in this data sheet. To use Standard-mode, set the APB bus clock at 2 MHz or more.

To use Fast-mode, set the APB bus clock at 8 MHz or more.

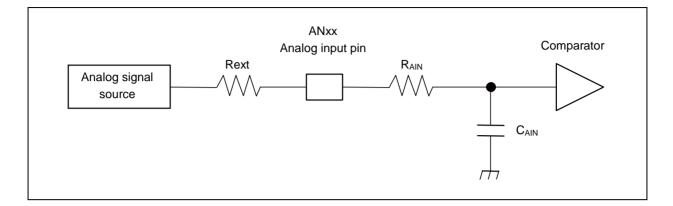

## (Equation 1) $t_S \ge (R_{AIN} + R_{EXT}) \times C_{AIN} \times 9$

- ts : Sampling time

- $\label{eq:RAIN} \begin{array}{l} \mbox{: Input resistor of A/D = 0.9 k\Omega at 4.5 V \leq AV_{CC} \leq 5.5 V} \\ \mbox{Input resistor of A/D = 1.6 k\Omega at 2.7 V \leq AV_{CC} < 4.5 V} \\ \mbox{Input resistor of A/D = 4.0 k\Omega at 1.8 V \leq AV_{CC} < 2.7 V} \end{array}$

- $C_{AIN}~$  : Input capacity of A/D = 15 pF at 1.8 V  $\leq$  AV\_{CC}  $\leq$  5.5 V

- R<sub>EXT</sub> : Output impedance of external circuit

#### (Equation 2) $t_c = t_{CCK} \times 14$

- t<sub>C</sub> : Compare time

- $t_{CCK}$  : Compare clock cycle

## 12.7 Flash Memory Write/Erase Characteristics

## 12.7.1 Write / Erase time

#### $(V_{CC} = 2.0V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } + 85^{\circ}C)$

| Parameter                        |                        | Value |                                             | Unit | Remarks                                     |  |  |

|----------------------------------|------------------------|-------|---------------------------------------------|------|---------------------------------------------|--|--|

|                                  |                        | Typ*  | Max*                                        | Onit | i/cilidik5                                  |  |  |

| Sector erase                     | e Large Sector 1.6 7.5 |       | Includes write time prior to internal erase |      |                                             |  |  |

| time                             | Small Sector           | 0.4   | 2.1                                         | S    | includes while time phot to internal erase  |  |  |

| Half word (16-bit)<br>write time |                        | 25    | 400                                         | μs   | Not including system-level overhead time.   |  |  |

| Chip erase time                  |                        | 4     | 19.2                                        | s    | Includes write time prior to internal erase |  |  |

\*: The typical value is immediately after shipment, the maximam value is guarantee value under 100,000 cycle of erase/write.

#### 12.7.2 Write cycles and data hold time

| Erase/write cycles (cycle) | Data hold time (year) | Remarks |

|----------------------------|-----------------------|---------|

| 1,000                      | 20*                   |         |

| 10,000                     | 10*                   |         |

| 100,000                    | 5*                    |         |

\*: At average + 85°C

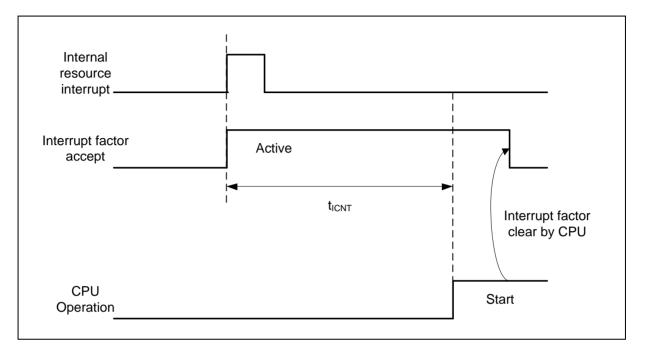

## Operation example of return from Low-Power consumption mode (by internal resource interrupt\*)

\*: Internal resource interrupt is not included in return factor by the kind of Low-Power consumption mode.

- **Notes:** The return factor is different in each Low-Power consumption modes. See Chapter 6: Low Power Consumption Mode and Operations of Standby Modes in FM3 Family Peripheral Manual.

- When interrupt recoveries, the operation mode that CPU recoveries depend on the state before the Low-Power consumption mode transition. See Chapter 6: Low Power Consumption Mode in FM3 Family Peripheral Manual.

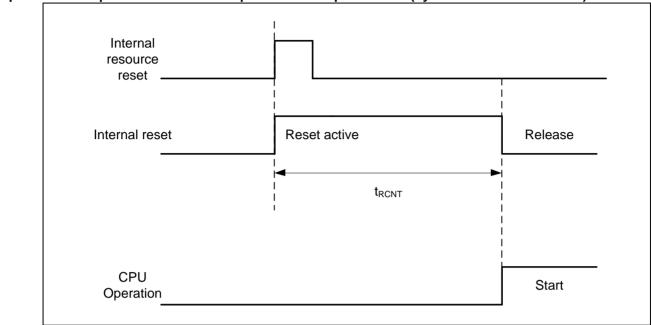

#### Operation example of return from low power consumption mode (by internal resource reset\*)

\*: Internal resource reset is not included in return factor by the kind of Low-Power consumption mode.

- **Notes:** The return factor is different in each Low-Power consumption modes. See Chapter 6: Low Power Consumption Mode and Operations of Standby Modes in FM3 Family Peripheral Manual.

- When interrupt recoveries, the operation mode that CPU recoveries depend on the state before the Low-Power consumption mode transition. See Chapter 6: Low Power Consumption Mode in FM3 Family Peripheral Manual.

- The time during the power-on reset/low-voltage detection reset is excluded. See (6) Power-on Reset Timing in 12.4 AC Characteristics in Electrical Characteristics for the detail on the time during the power-on reset/low-voltage detection reset.

- When in recovery from reset, CPU changes to the High-speed CR Run mode. When using the main clock or the PLL clock, it is necessary to add the main clock oscillation stabilization wait time or the Main PLL clock stabilization wait time.

- The internal resource reset means the watchdog reset and the CSV reset.

# **13. Ordering Information**

| Part number           | On-chip<br>Flash<br>memory | On-chip<br>SRAM | Package                                 | Packing |

|-----------------------|----------------------------|-----------------|-----------------------------------------|---------|

| MB9AF131KBPMC-G-SNE2  | 64 Kbyte                   | 8 Kbyte         |                                         | Tray    |

| MB9AF132KBPMC-G-SNE2  | 128 Kbyte                  | 8 Kbyte         | (0.5mm pitch), 48-pin<br>(FPT-48P-M49)  |         |

| MB9AF131KBQN-G-AVE2   | 64 Kbyte                   | 8 Kbyte         |                                         |         |

| MB9AF132KBQN-G-AVE2   | 128 Kbyte                  | 8 Kbyte         | (0.5mm pitch), 48-pin<br>(LCC-48P-M73)  |         |

| MB9AF131LBPMC1-G-SNE2 | 64 Kbyte                   | 8 Kbyte         | Plastic • LQFP                          |         |

| MB9AF132LBPMC1-G-SNE2 | 128 Kbyte                  | 8 Kbyte         | (0.5mm pitch), 64-pin<br>(FPT-64P-M38)  |         |

| MB9AF131LBPMC-G-SNE2  | 64 Kbyte                   | 8 Kbyte         | Plastic • LQFP                          |         |

| MB9AF132LBPMC-G-SNE2  | 128 Kbyte                  | 8 Kbyte         | (0.65mm pitch), 64-pin<br>(FPT-64P-M39) |         |

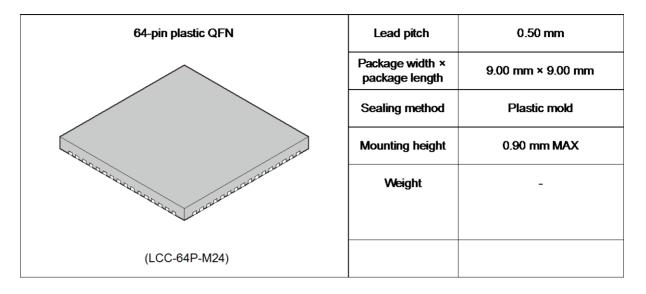

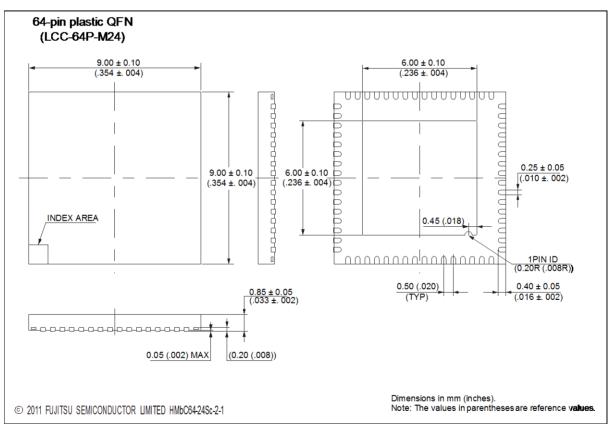

| MB9AF131LBQN-G-AVE2   | 64 Kbyte                   | 8 Kbyte         |                                         | ]       |

| MB9AF132LBQN-G-AVE2   | 128 Kbyte                  | 8 Kbyte         | (0.5mm pitch), 64-pin<br>(LCC-64P-M24)  |         |