# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                       |

| Speed                      | 216MHz                                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                             |

| Number of I/O              | 82                                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 256K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                    |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 100-LQFP                                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f730v8t6                    |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

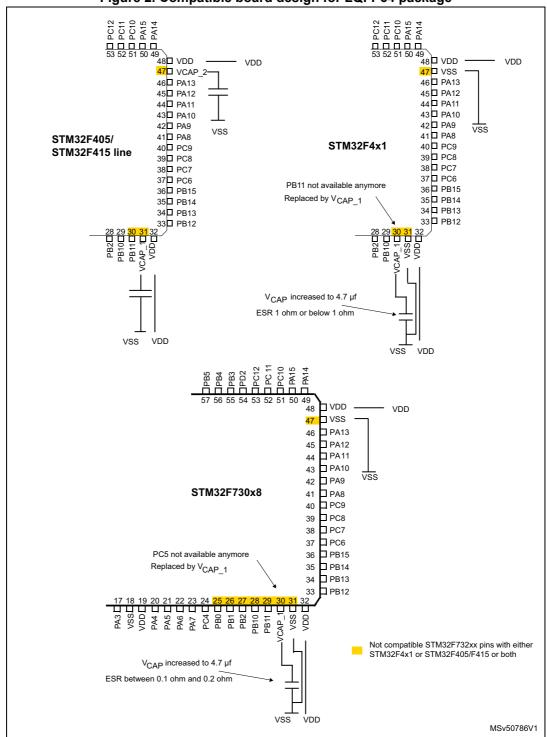

Figure 2. Compatible board design for LQFP64 package

DS12536 Rev 1

# 3.7 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support a circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. The configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDMMC

- ADC

- SAI

- Quad-SPI

# 3.13 Boot modes

At startup, the boot memory space is selected by the BOOT pin and BOOT\_ADDx option bytes, allowing to program any boot memory address from 0x0000 0000 to 0x3FFF FFFF which includes:

- All Flash address space mapped on ITCM or AXIM interface

- All RAM address space: ITCM, DTCM RAMs and SRAMs mapped on AXIM interface

- The System memory bootloader

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface.

# 3.14 Power supply schemes

- V<sub>DD</sub> = 1.7 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Note: The  $V_{DD}/V_{DDA}$  minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 3.15.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

- The V<sub>DDSDMMC</sub> can be connected either to V<sub>DD</sub> or an external independent power supply (1.8 to 3.6V) for the SDMMC2 pins (clock, command, and 4-bit data). For example, when the device is powered at 1.8V, an independent power supply 2.7V can be connected to V<sub>DDSDMMC</sub>. When the V<sub>DDSDMMC</sub> is connected to a separated power supply, it is independent from V<sub>DD</sub> or V<sub>DDA</sub> but it must be the last supply to be provided and the first to disappear. The following conditions V<sub>DDSDMMC</sub> must be respected:

- During the power-on phase ( $V_{DD} < V_{DD\_MIN}$ ),  $V_{DDSDMMC}$  should be always lower than  $V_{DD}$

- During the power-down phase (V<sub>DD</sub> < V<sub>DD\_MIN</sub>), V<sub>DDSDMMC</sub> should be always lower than V<sub>DD</sub>

- The V<sub>DDSDMMC</sub> rising and falling time rate specifications must be respected

- In the operating mode phase, V<sub>DDSDMMC</sub> could be lower or higher than V<sub>DD</sub>.

All associated GPIOs powered by V<sub>DDSDMMC</sub> are operating between

V<sub>DDSDMMC\_MIN</sub> and V<sub>DDSDMMC\_MAX</sub>.

- The V<sub>DDUSB</sub> can be connected either to V<sub>DD</sub> or an external independent power supply (3.0 to 3.6V) for USB transceivers (refer to *Figure 6* and *Figure 7*). For example, when the device is powered at 1.8V, an independent power supply 3.3V can be connected to the V<sub>DDUSB</sub>. When the V<sub>DDUSB</sub> is connected to a separated power supply, it is independent from V<sub>DD</sub> or V<sub>DDA</sub> but it must be the last supply to be provided and the first to disappear. The following conditions V<sub>DDUSB</sub> must be respected:

- During the power-on phase ( $V_{DD} < V_{DD\_MIN}$ ),  $V_{DDUSB}$  should be always lower than  $V_{DD}$

- During the power-down phase (V\_{DD} < V\_{DD\\_MIN}), V\_{DDUSB} should be always lower than V\_{DD}

# 3.20.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

The TIM1 and TIM8 support independent DMA request generation.

### 3.20.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F730x8 devices (see *Table 6* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F730x8 include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

### 3.20.3 Basic timers TIM6 and TIM7

These timers are mainly used for the DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

The TIM6 and TIM7 support independent DMA request generation.

DS12536 Rev 1

| Pin Number |         |         |          |                                                   | - •-     |               | i ball definition (continued) |                                                                                                  |                         |

|------------|---------|---------|----------|---------------------------------------------------|----------|---------------|-------------------------------|--------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64     | LQFP100 | LQFP144 | UFBGA176 | Pin name (function<br>after reset) <sup>(1)</sup> | Pin type | I/O structure | Notes                         | Alternate functions                                                                              | Additional<br>functions |

| -          | -       | 78      | R15      | PB15                                              | I/O      | FT            | -                             | OTG_HS_DP                                                                                        | -                       |

| _          | 55      | 79      | P15      | PD8                                               | I/O      | FT            | -                             | USART3_TX, FMC_D13,<br>EVENTOUT                                                                  | -                       |

| -          | 56      | 80      | P14      | PD9                                               | I/O      | FT            | -                             | USART3_RX, FMC_D14,<br>EVENTOUT                                                                  | -                       |

| -          | 57      | 81      | N15      | PD10                                              | I/O      | FT            | -                             | USART3_CK, FMC_D15,<br>EVENTOUT                                                                  | -                       |

| -          | 58      | 82      | N14      | PD11                                              | I/O      | FT            | -                             | USART3_CTS,<br>QUADSPI_BK1_IO0, SAI2_SD_A,<br>FMC_A16/FMC_CLE, EVENTOUT                          | -                       |

| -          | 59      | 83      | N13      | PD12                                              | I/O      | FT            | -                             | TIM4_CH1, LPTIM1_IN1,<br>USART3_RTS,<br>QUADSPI_BK1_IO1, SAI2_FS_A,<br>FMC_A17/FMC_ALE, EVENTOUT | -                       |

| -          | 60      | 84      | M15      | PD13                                              | I/O      | FT            | -                             | TIM4_CH2, LPTIM1_OUT,<br>QUADSPI_BK1_IO3,<br>SAI2_SCK_A, FMC_A18,<br>EVENTOUT                    | -                       |

| -          | -       | 85      | -        | VSS                                               | S        | -             | -                             | -                                                                                                | -                       |

| -          | -       | 86      | J13      | VDD                                               | S        | -             | -                             | -                                                                                                | -                       |

| -          | 61      | 87      | M14      | PD14                                              | I/O      | FT            | -                             | TIM4_CH3, UART8_CTS,<br>FMC_D0, EVENTOUT                                                         | -                       |

| -          | 62      | 88      | L14      | PD15                                              | I/O      | FT            | -                             | TIM4_CH4, UART8_RTS,<br>FMC_D1, EVENTOUT                                                         | -                       |

| -          | -       | 89      | L15      | PG2                                               | I/O      | FT            | -                             | FMC_A12, EVENTOUT                                                                                | -                       |

| -          | -       | 90      | K15      | PG3                                               | I/O      | FT            | -                             | FMC_A13, EVENTOUT                                                                                | -                       |

| -          | -       | 91      | K14      | PG4                                               | I/O      | FT            | -                             | FMC_A14/FMC_BA0, EVENTOUT                                                                        | -                       |

| -          | -       | 92      | K13      | PG5                                               | I/O      | FT            | -                             | FMC_A15/FMC_BA1, EVENTOUT                                                                        | -                       |

| -          | -       | -       | -        | PG6                                               | I/O      | FT            | -                             | EVENTOUT                                                                                         | -                       |

| -          | -       | -       | -        | PG7                                               | I/O      | FT            | -                             | USART6_CK, FMC_INT,<br>EVENTOUT                                                                  | -                       |

Table 10. STM32F730x8 pin and ball definition (continued)

80/201

DS12536 Rev 1

|        |      | AF0 | AF1    | AF2      | AF3                     | AF4                 | AF5                                              | AF6                                                      | AF7                                              | AF8                                     | AF9                                                  | AF10                                                | AF11          | AF12                                 | AF15         |

|--------|------|-----|--------|----------|-------------------------|---------------------|--------------------------------------------------|----------------------------------------------------------|--------------------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------------------------------------|---------------|--------------------------------------|--------------|

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/1<br>1/LPTIM1 | I2C1/2/3/U<br>SART1 | SPI1/I2S1/<br>SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/5 | SPI2/I2S2/<br>SPI3/I2S3/<br>SPI3/I2S3/<br>SAI1/<br>UART4 | SPI2/I2S2/S<br>PI3/I2S3/US<br>ART1/2/3/UA<br>RT5 | SAI2/USART<br>6/UART4/5/7/<br>8/OTG1_FS | CAN1/TIM1<br>2/13/14/QU<br>ADSPI/<br>FMC/<br>OTG2_HS | SAI2/QUAD<br>SPI/SDMM<br>C2/OTG2_<br>HS/OTG1_<br>FS | SDMMC2        | UART7/F<br>MC/SDM<br>MC1/<br>OTG2_FS | SYS          |

|        | PG0  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A10                              | EVEN<br>TOUT |

|        | PG1  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A11                              | EVEN<br>TOUT |

|        | PG2  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A12                              | EVEN<br>TOU  |

|        | PG3  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A13                              | EVEI<br>TOU  |

|        | PG4  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A14/<br>FMC_BA0                  | EVEN<br>TOU  |

| Port G | PG5  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A15/<br>FMC_BA1                  | EVEN<br>TOU  |

|        | PG6  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | -                                    | EVEN<br>TOU  |

|        | PG7  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | USART6_CK                               | -                                                    | -                                                   | -             | FMC_INT                              | EVEN<br>TOUT |

|        | PG8  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | USART6_RT<br>S                          | -                                                    | -                                                   | -             | FMC_SDC<br>LK                        | EVEN<br>TOU  |

|        | PG9  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | USART6_RX                               | QUADSPI_<br>BK2_IO2                                  | SAI2_FS_B                                           | SDMMC2<br>_D0 | FMC_NE2<br>/FMC_NC<br>E              | EVEI<br>TOU  |

|        | PG10 | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | SAI2_SD_B                                           | SDMMC2<br>_D1 | FMC_NE3                              | EVE<br>TOU   |

Table 12. STM32F730x8 alternate function mapping (continued)

5

1. When bypassing the voltage regulator, the two 2.2  $\mu$ F V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

| Symbol | Parameter                         | Conditions                            |

|--------|-----------------------------------|---------------------------------------|

| CEXT   | Capacitance of external capacitor | 4.7 µF                                |

| ESR    | ESR of external capacitor         | between 0.1 $\Omega$ and 0.2 $\Omega$ |

#### Table 19. VCAP1 operating conditions in the LQFP64 package<sup>(1)</sup>

When bypassing the voltage regulator, the 4.7 μF V<sub>CAP</sub> capacitor is not required and should be replaced by two 100 nF decoupling capacitors.

# 6.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for T<sub>A</sub>.

| Table 20. Operating conditions at power-up / | power-down (regulator ON) |

|----------------------------------------------|---------------------------|

|----------------------------------------------|---------------------------|

| Symbol           | Parameter                      | Min | Мах | Unit  |

|------------------|--------------------------------|-----|-----|-------|

| 1                | V <sub>DD</sub> rise time rate | 20  | ∞   | µs/V  |

| <sup>I</sup> VDD | V <sub>DD</sub> fall time rate | 20  | 8   | μ5/ ν |

# 6.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for T<sub>A</sub>.

| Table 21. Operating conditions at power-up / | power-down (regulator OFF) <sup>(1)</sup> |

|----------------------------------------------|-------------------------------------------|

|                                              |                                           |

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit  |

|-------------------|----------------------------------------------|------------|-----|-----|-------|

| +                 | V <sub>DD</sub> rise time rate               | Power-up   | 20  | ~   |       |

| tvdd              | V <sub>DD</sub> fall time rate               | Power-down | 20  | 8   | μs/V  |

| +                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | 8   | μ5/ ν |

| t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | 8   |       |

1. To reset the internal logic at power-down, a reset must be applied on pin PA0 when  $V_{\text{DD}}$  reach below 1.08 V.

# 6.3.5 Reset and power control block characteristics

The parameters given in *Table 22* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*.

|          | Parameter                 |                                                                 |                            | Typ <sup>(1)</sup>         |                            |                           |                           |                            |      |  |

|----------|---------------------------|-----------------------------------------------------------------|----------------------------|----------------------------|----------------------------|---------------------------|---------------------------|----------------------------|------|--|

| Symbol   |                           | Conditions                                                      | Т                          | <sub>A</sub> = 25 °        | С                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

|          |                           |                                                                 | V <sub>DD</sub> =<br>1.7 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | ~                         | / <sub>DD</sub> = 3.3     | V                          |      |  |

|          |                           | Backup SRAM OFF, RTC and LSE OFF                                | 1.09                       | 1.13                       | 1.4                        | 4                         | 27                        | 55                         |      |  |

|          |                           | Backup SRAM ON, RTC and LSE OFF                                 | 1.85                       | 1.88                       | 2.17                       | 5                         | 30                        | 60                         |      |  |

|          |                           | Backup SRAM OFF, RTC ON and LSE in low drive mode               | 1.65                       | 1.86                       | 2.43                       | 7                         | 47                        | 95.5                       | μA   |  |

|          |                           | Backup SRAM OFF, RTC ON<br>and LSE in medium low drive<br>mode  | 1.67                       | 1.88                       | 2.46                       | 7                         | 47.5                      | 97                         |      |  |

|          | Supply current in Standby | Backup SRAM OFF, RTC ON<br>and LSE in medium high drive<br>mode | 1.8                        | 2.01                       | 2.61                       | 7.5                       | 50.5                      | 102.5                      |      |  |

| IDD_STBY | mode                      | Backup SRAM OFF, RTC ON<br>and LSE in high drive mode           | 1.92                       | 2.13                       | 2.73                       | 8                         | 53                        | 107                        |      |  |

|          |                           | Backup SRAM ON, RTC ON<br>and LSE in low drive mode             | 2.39                       | 2.6                        | 3.23                       | 9                         | 62                        | 127                        |      |  |

|          |                           | Backup SRAM ON, RTC ON<br>and LSE in Medium low drive<br>mode   | 2.41                       | 2.64                       | 3.25                       | 9                         | 63                        | 128                        |      |  |

|          |                           | Backup SRAM ON, RTC ON<br>and LSE in Medium high drive<br>mode  | 2.67                       | 2.89                       | 2.53                       | 10                        | 68                        | 139                        |      |  |

|          |                           | Backup SRAM ON, RTC ON<br>and LSE in High drive mode            | 2.68                       | 2.9                        | 3.51                       | 10                        | 68                        | 138                        |      |  |

| Table 32. Typical and maximum current | consumptions in Standby mode |

|---------------------------------------|------------------------------|

|---------------------------------------|------------------------------|

1. PDR is OFF for  $V_{DD}$ =1.7V. When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2  $\mu$ A.

| _       |                                  |              | It consumption | (,      |        |

|---------|----------------------------------|--------------|----------------|---------|--------|

| P       | eripheral                        | Scale 1      | Scale 2        | Scale 3 | – Unit |

|         | TIM2                             | 19.3         | 18.2           | 15.6    |        |

| Γ       | TIM3                             | 15           | 14             | 12.2    |        |

| T       | TIM4                             | 15.7         | 15.1           | 12.8    |        |

| T       | TIM5                             | 18           | 16.9           | 14.4    |        |

| Ī       | TIM6                             | 3.7          | 3.1            | 2.8     |        |

|         | TIM7                             | 3.5          | 2.9            | 2.5     |        |

|         | TIM12                            | 8.1          | 7.8            | 6.4     |        |

|         | TIM13                            | 6.1          | 5.1            | 4.7     |        |

|         | TIM14                            | 6.3          | 5.6            | 4.7     |        |

|         | LPTIM1                           | 9.4          | 9.8            | 8.3     |        |

|         | WWDG<br>SPI2/I2S2 <sup>(3)</sup> | 2.4          | 1.3            | 1.4     |        |

| APB1    |                                  | 6.7          | 6              | 5.3     |        |

| (up to  | SPI3/I2S3 <sup>(3)</sup>         | 4.8          | 3.8            | 3.3     | µA/MHz |

| 54 MHz) | USART2                           | 13.3         | 12             | 10.6    |        |

|         | USART3                           | 12.8         | 12             | 10.3    |        |

|         | UART4                            | 11.7         | 10.7           | 9.2     |        |

|         | UART5                            | 11.7         | 10.2           | 8.9     |        |

|         | I2C1                             | 10.6         | 9.6            | 8.3     |        |

|         | I2C2                             | 10.6         | 9.6            | 8.3     |        |

| F       | I2C3                             | 10.7         | 9.8            | 8.3     | 1      |

| F       | CAN1                             | 8.9          | 8              | 6.9     | 1      |

| F       | PWR                              | PWR 11.3 11. | 11.3           | 8.9     | 1      |

| F       | DAC <sup>(4)</sup>               | 6.1          | 5.1            | 4.4     | 1      |

| F       | UART7                            | 13.3         | 12             | 10.3    | 1      |

| F       | UART8                            | 12.6         | 11.6           | 9.7     | 1      |

Table 35. Peripheral current consumption (continued)

# 6.3.10 Internal clock source characteristics

The parameters given in *Table 42* and *Table 43* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*.

# High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |

|                                     | HSI user trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |

| ACC <sub>HSI</sub>                  | Accuracy of the HSI oscillator        | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |

|                                     |                                       | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | - 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4   | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                    | -   | 60  | 80  | μA   |

| Table 42. HSI oscillator | <sup>,</sup> characteristics <sup>(1)</sup> |

|--------------------------|---------------------------------------------|

|--------------------------|---------------------------------------------|

1. V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = –40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Factory calibrated, parts not soldered.

#### Figure 32. ACCHSI versus temperature

| Symbol            | Parameter           | Conditions                                  | Min <sup>(1)</sup> | ,<br>Тур | Max <sup>(1)</sup> | Unit |  |

|-------------------|---------------------|---------------------------------------------|--------------------|----------|--------------------|------|--|

| <i>cy</i>         |                     |                                             |                    | -76      | шах                | •    |  |

| t <sub>ME</sub>   | Mass erase time     | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 7718     | 9883               |      |  |

|                   |                     | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 4869     | 6379               | ms   |  |

|                   |                     | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 3503     | 5180               |      |  |

| V <sub>prog</sub> | Programming voltage | 32-bit program operation                    | 2.7                | -        | 3                  | V    |  |

|                   |                     | 16-bit program operation                    | 2.1                | -        | 3.6                | V    |  |

|                   |                     | 8-bit program operation                     | 1.7                | -        | 3.6                | V    |  |

Table 53. Flash memory programming (continued)

1. Guaranteed by characterization results.

2. The maximum programming time is measured after 10 K erase operations.

|                                 | Table 54. Flash me                               | emory programming            | with v <sub>F</sub> | P                  |                    |      |

|---------------------------------|--------------------------------------------------|------------------------------|---------------------|--------------------|--------------------|------|

| Symbol                          | Parameter Conditions Min <sup>(1)</sup>          |                              | Тур                 | Max <sup>(1)</sup> | Unit               |      |

| t <sub>prog</sub>               | Double word programming                          |                              | -                   | 16                 | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                   | 180                | -                  |      |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>DD</sub> = 3.3 V      | -                   | 900                | -                  | ms   |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>PP</sub> = 8.5 V      | -                   | 450                | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                   | 6.9                | -                  | s    |

| V <sub>prog</sub>               | Programming voltage                              | -                            | 2.7                 | -                  | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range -                  |                              | 7                   | -                  | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                            | 10                  | -                  | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                            | -                   | -                  | 1                  | hour |

1. Guaranteed by design.

2. The maximum programming time is measured after 10 K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions <sup>(1)</sup>                                                               | Value<br>Min <sup>(2)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(3)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(3)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(3)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

| Symbol                | Ratings                                               | Conditions                                                                                             | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | T <sub>A</sub> = +25 °C conforming to<br>ANSI/ESDA/JEDEC JS-001-2012                                   | 2     | 2000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C conforming to ANSI/ESD<br>STM5.3.1-2009, all the packages<br>excepted WLCSP100 | 3     | 250                             | V    |

#### Table 58. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### **Static latchup**

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

#### Table 59. Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A$ = +105 °C conforming to JESD78A | II level A |

#### 6.3.19 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of – 5  $\mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in *Table 60*.

Unless otherwise specified, the parameters given in *Table 63* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min                                             | Тур                                             | Мах                | Unit  |      |  |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------------------|-------|------|--|

|                                               |                                                  |                                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$             | -                                               | -                                               | 4                  | MHz   |      |  |

|                                               |                                                  |                                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 1.7 \text{ V}$             | -                                               | -                                               | 2                  |       |      |  |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | $C_L$ = 10 pF, $V_{DD}$ ≥ 2.7 V                             | -                                               | -                                               | 8                  |       |      |  |

| 00                                            |                                                  |                                                                                 | $C_L$ = 10 pF, $V_{DD}$ ≥ 1.8 V                             | -                                               | -                                               | 4                  |       |      |  |

|                                               |                                                  |                                                                                 | $C_L$ = 10 pF, $V_{DD}$ ≥ 1.7 V                             | -                                               | -                                               | 3                  |       |      |  |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.7 V to<br>3.6 V | -                                               | -                                               | 100                | ns    |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -                                               | 25                 |       |      |  |

|                                               |                                                  | f <sub>max(IO)out</sub> Maximum frequency <sup>(3)</sup>                        | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.8 V             | -                                               | -                                               | 12.5               | - MHz |      |  |

|                                               | f <sub>max(IO)out</sub>                          |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -                                               | 10                 |       |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -                                               | 50                 |       |      |  |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V             | -                                               | -                                               | 20                 |       |      |  |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -                                               | 12.5               |       |      |  |

|                                               |                                                  |                                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$             | -                                               | -                                               | 10                 |       |      |  |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | <sup>t</sup> f(IO)out/ time and c                                               | Output high to low level fall time and output low to high   | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -                  | 6     | - ns |  |

|                                               |                                                  |                                                                                 | level rise time                                             | $C_L = 50 \text{ pF}, V_{DD} \ge 1.7 \text{ V}$ | -                                               | -                  | 20    |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -                                               | 10                 | 1     |      |  |

|                                               |                                                  |                                                                                 | $C_L$ = 40 pF, $V_{DD} \ge 2.7 V$                           | -                                               | -                                               | 50 <sup>(4)</sup>  |       |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -                                               | 100 <sup>(4)</sup> |       |      |  |

| 10                                            | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -                                               | 25                 | MHz   |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V             | -                                               | -                                               | 50                 |       |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -                                               | 42.5               |       |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥2.7 V              | -                                               | -                                               | 6                  | - ns  |      |  |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -                                               | 4                  |       |      |  |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | $C_L$ = 40 pF, $V_{DD} \ge 1.7 V$                           | -                                               | -                                               | 10                 |       |      |  |

|                                               |                                                  |                                                                                 |                                                             |                                                 | $C_L = 10 \text{ pF}, V_{DD} \ge 1.7 \text{ V}$ | -                  | -     | 6    |  |

| Table 63. I | /O AC | characteristics <sup>(1)(2)</sup> |

|-------------|-------|-----------------------------------|

|-------------|-------|-----------------------------------|

#### **Electrical characteristics**

|                                      | Table 78. DAC characteristics (continued)                                                                                                                          |     |     |      |      |                                                                                                              |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                               | Parameter                                                                                                                                                          | Min | Тур | Мах  | Unit | Comments                                                                                                     |  |  |  |

| I <sub>VREF+</sub> <sup>(4)</sup>    | DAC DC V <sub>REF</sub> current consumption in quiescent                                                                                                           | -   | 170 | 240  | μA   | With no load, worst code (0x800) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs |  |  |  |

| 'VREF+`´                             | mode (Standby mode)                                                                                                                                                | -   | 50  | 75   | μΑ   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs |  |  |  |

|                                      | DAC DC V <sub>DDA</sub> current                                                                                                                                    | -   | 280 | 380  | μA   | With no load, middle code (0x800) on the inputs                                                              |  |  |  |

| I <sub>DDA</sub> <sup>(4)</sup>      | consumption in quiescent<br>mode <sup>(3)</sup>                                                                                                                    | -   | 475 | 625  | μA   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs |  |  |  |

| DNL <sup>(4)</sup>                   | Differential non linearity<br>Difference between two                                                                                                               | -   | -   | ±0.5 | LSB  | Given for the DAC in 10-bit configuration.                                                                   |  |  |  |

|                                      | consecutive code-1LSB)                                                                                                                                             | -   | -   | ±2   | LSB  | Given for the DAC in 12-bit configuration.                                                                   |  |  |  |

|                                      | Integral non linearity<br>(difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023)      | -   | -   | ±1   | LSB  | Given for the DAC in 10-bit configuration.                                                                   |  |  |  |

| INL <sup>(4)</sup>                   |                                                                                                                                                                    | -   | -   | ±4   | LSB  | Given for the DAC in 12-bit configuration.                                                                   |  |  |  |

|                                      | Offset error                                                                                                                                                       | -   | -   | ±10  | mV   | Given for the DAC in 12-bit configuration                                                                    |  |  |  |

| Offset <sup>(4)</sup>                | (difference between<br>measured value at Code<br>(0x800) and the ideal value =<br>$V_{REF+}/2$ )                                                                   | -   | -   | ±3   | LSB  | Given for the DAC in 10-bit at V <sub>REF+</sub> =<br>3.6 V                                                  |  |  |  |

|                                      |                                                                                                                                                                    | -   | -   | ±12  | LSB  | Given for the DAC in 12-bit at $V_{REF+}$ = 3.6 V                                                            |  |  |  |

| Gain<br>error <sup>(4)</sup>         | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                                    |  |  |  |

| t <sub>SETTLING</sub> <sup>(4)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±4LSB | -   | 3   | 6    | μs   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                            |  |  |  |

| THD <sup>(4)</sup>                   | Total Harmonic Distortion<br>Buffer ON                                                                                                                             | -   | -   | -    | dB   | $\begin{array}{l} C_{LOAD} \leq 50 \text{ pF,} \\ R_{LOAD} \geq 5  k\Omega \end{array}$                      |  |  |  |

| Update<br>rate <sup>(2)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                            |  |  |  |

| Symbol    | Parameter           | Con            | dition                     | Min  | Unit |

|-----------|---------------------|----------------|----------------------------|------|------|

|           |                     | Standard-mode  | -                          | 2    | MHz  |

|           | I2CCLK<br>frequency | Fast-mode      | Analog Filter ON<br>DNF=0  | 10   |      |

| f(I2CCLK) |                     |                | Analog Filter OFF<br>DNF=1 | 9    |      |

|           |                     | Fast-mode Plus | Analog Filter ON<br>DNF=0  | 22.5 |      |

|           |                     | rast-mode rius | Analog Filter OFF<br>DNF=1 | 16   |      |

Table 79. Minimum I2CCLK frequency in all I2C modes

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present.

The 20mA output drive requirement in Fast-mode Plus is not supported. This limits the maximum load Cload supported in Fm+, which is given by these formulas:

- Tr(SDA/SCL)=0.8473xRpxCload

- $R_p(min) = (VDD-V_{OL}(max))/I_{OL}(max)$

Where Rp is the I2C lines pull-up. Refer to *Section 6.3.20: I/O port characteristics* for the I2C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

1. Guaranteed by characterization results.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

| Symbol                      | Parameter                                       | Min          | Max | Unit |

|-----------------------------|-------------------------------------------------|--------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                                  | 2Thclk - 0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)               | -            | 2   |      |

| t <sub>d(CLKH_NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)            | Thclk + 0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                     | -            | 1   |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high                    | 0            | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)            | -            | 3   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)         | Thclk        | -   |      |

| t <sub>d(CLKL-NOEL)</sub>   | FMC_CLK low to FMC_NOE low                      | -            | 2   | ns   |

| t <sub>d(CLKH-NOEH)</sub>   | FMC_CLK high to FMC_NOE high                    | Thclk - 0.5  | -   |      |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid               | -            | 2   |      |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid             | 0            | -   |      |

| t <sub>su(ADV-CLKH)</sub>   | FMC_A/D[15:0] valid data before FMC_CLK<br>high | 0.5          | -   |      |

| t <sub>h(CLKH-ADV)</sub>    | FMC_A/D[15:0] valid data after FMC_CLK high     | 4            | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high             | 2            | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high              | 3            | -   |      |

Table 101. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)</sup>

| Symbol                      | Parameter                                  | Min          | Мах | Unit |

|-----------------------------|--------------------------------------------|--------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                             | 2Thclk - 0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -            | 2   | ]    |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)       | Thclk +0.5   | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                | -            | 1   |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high               | 0            | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)       | -            | 3   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)    | Thclk        | -   |      |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                 | -            | 1.5 |      |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high               | Thclk +0.5   | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid          | -            | 3   |      |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid        | 0            | -   | 1    |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low | -            | 3   |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                 | -            | 2   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high               | Thclk +0.5   | -   | ]    |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high        | 2            | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high         | 3            | -   |      |

Table 102. Synchronous multiplexed PSRAM write timings<sup>(1)</sup>

| Symbol                        | Parameter              | Min         | Мах         | Unit |

|-------------------------------|------------------------|-------------|-------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2Thclk -0.5 | 2Thclk +0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time  | 1.5         | -           |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 2           | -           |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -           | 1.5         |      |

| t <sub>d</sub> (SDCLKL- SDNE) | Chip select valid time | -           | 1.5         | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0.5         | -           | 113  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -           | 1           |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0.5         | -           |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -           | 1.5         |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0           | -           |      |

# Table 107. SDRAM read timings<sup>(1)</sup>

1. Guaranteed by characterization results.

# Table 108. LPSDR SDRAM read timings<sup>(1)</sup>

| Symbol                        | Parameter              | Min         | Мах         | Unit |

|-------------------------------|------------------------|-------------|-------------|------|

| t <sub>W(SDCLK)</sub>         | FMC_SDCLK period       | 2Thclk -0.5 | 2Thclk +0.5 |      |

| t <sub>su(SDCLKH_Data)</sub>  | Data input setup time  | 0           | -           |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 4.5         | -           |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -           | 1.5         |      |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -           | 1.5         | ns   |

| $t_{h(SDCLKL\_SDNE)}$         | Chip select hold time  | 0           | -           | 115  |

| t <sub>d(SDCLKL_SDNRAS</sub>  | SDNRAS valid time      | -           | 0.5         |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0           | -           |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -           | 1.5         |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0           | -           |      |

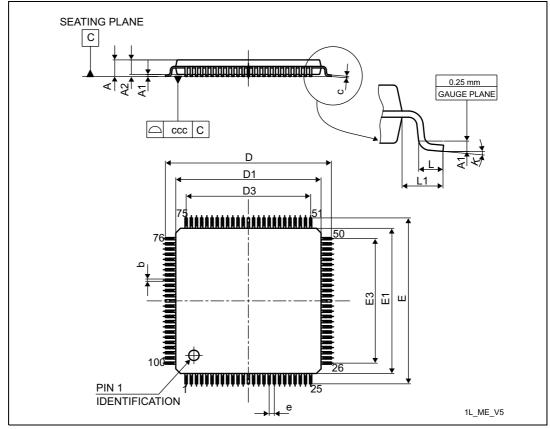

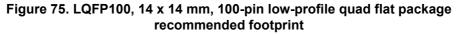

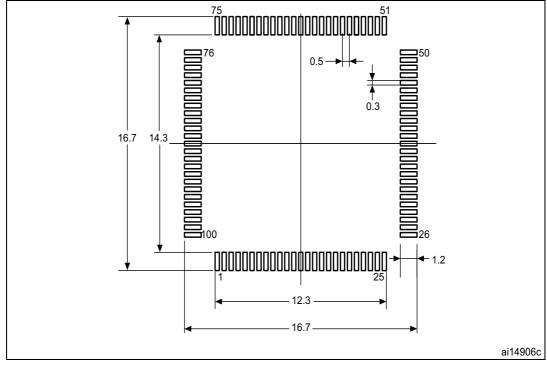

# 7.2 LQFP100, 14 x 14 mm low-profile quad flat package information

Figure 74. LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур    | Max    | Min                   | Тур    | Max    |  |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| E      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| Cumhal | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур    | Мах    | Min                   | Тур    | Мах    |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |  |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |  |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

# Table 116. LQPF100, 14 x 14 mm 100-pin low-profile quad flat package mechanicaldata (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.