# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

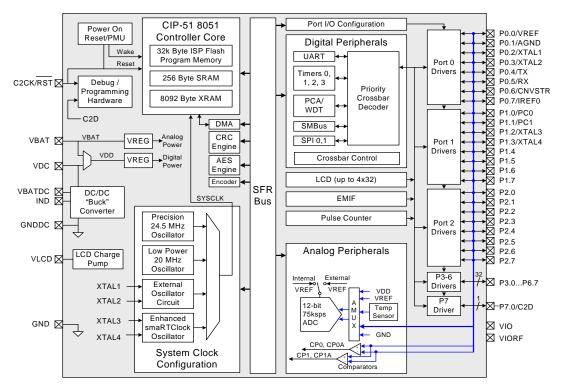

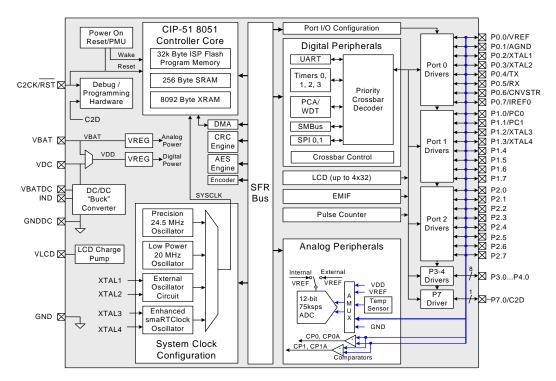

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                         |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | DMA, POR, PWM, WDT                                               |

| Number of I/O              | 57                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                 |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 8.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                      |

| Data Converters            | A/D 16x10b/12b                                                   |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 76-VFQFN Dual Rows, Exposed Pad                                  |

| Supplier Device Package    | 76-DQFN (6x6)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f962-a-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F96x

| 11.2.1. DMA0 Memory Access Arbitration                |     |

|-------------------------------------------------------|-----|

| 11.2.2. DMA0 Channel Arbitration                      |     |

| 11.3. DMA0 Operation in Low Power Modes               | 148 |

| 11.4. Transfer Configuration                          |     |

| 12. Cyclic Redundancy Check Unit (CRC0)               | 160 |

| 12.1. 16-bit CRC Algorithm                            | 160 |

| 12.3. Preparing for a CRC Calculation                 | 163 |

| 12.4. Performing a CRC Calculation                    | 163 |

| 12.5. Accessing the CRC0 Result                       |     |

| 12.6. CRC0 Bit Reverse Feature                        |     |

| 13. DMA-Enabled Cyclic Redundancy Check Module (CRC1) | 168 |

| 13.1. Polynomial Specification                        |     |

| 13.2. Endianness                                      |     |

| 13.3. CRC Seed Value                                  |     |

| 13.4. Inverting the Final Value                       |     |

| 13.5. Flipping the Final Value                        |     |

| 13.6. Using CRC1 with SFR Access                      |     |

| 13.7. Using the CRC1 module with the DMA              | 171 |

| 14. Advanced Encryption Standard (AES) Peripheral     |     |

| 14.1. Hardware Description                            |     |

| 14.1.1. AES Encryption/Decryption Core                |     |

| 14.1.2. Data SFRs                                     |     |

| 14.1.3. Configuration sfrs                            |     |

| 14.1.4. Input Multiplexer                             |     |

| 14.1.5. Output Multiplexer                            |     |

| 14.1.6. Internal State Machine                        |     |

| 14.2. Key Inversion                                   |     |

| 14.2.1. Key Inversion using DMA                       |     |

| 14.2.2. Key Inversion using SFRs                      |     |

| 14.2.3. Extended Key Output Byte Order                |     |

| 14.2.4. Using the DMA to unwrap the extended Key      |     |

| 14.3. AES Block Cipher                                |     |

| 14.4. AES Block Cipher Data Flow                      | 185 |

| 14.4.1. AES Block Cipher Encryption using DMA         |     |

| 14.4.2. AES Block Cipher Encryption using SFRs        |     |

| 14.5. AES Block Cipher Decryption                     |     |

| 14.5.1. AES Block Cipher Decryption using DMA         | 188 |

| 14.5.2. AES Block Cipher Decryption using SFRs        |     |

| 14.6. Block Cipher Modes                              |     |

| 14.6.1. Cipher Block Chaining Mode                    | 190 |

| 14.6.2. CBC Encryption Initialization Vector Location |     |

| 14.6.3. CBC Encryption using DMA                      |     |

| 14.6.4. CBC Decryption                                |     |

| 14.6.5. Counter Mode                                  |     |

| 14.6.6. CTR Encryption using DMA                      |     |

|                                                       | 200 |

# C8051F96x

27

# C8051F96x

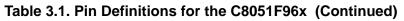

|                  | Pi     | n Numbe | rs    |                       |                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------------------|--------|---------|-------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name             | DQFN76 |         | QFN40 | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                    |  |  |

| P0.0             | A4     | 6       | 4     | D I/O or<br>A In      | Port 0.0. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>REF</sub> |        |         |       | A In<br>A Out         | External $V_{REF}$ Input.<br>Internal $V_{REF}$ Output. External $V_{REF}$ decoupling capacitors are recommended. See ADC0 Section for details.                                                                                                                                                                                                                |  |  |

| P0.1             | A3     | 4       | 3     | D I/O or<br>A In      | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |

| AGND             |        |         |       | G                     | Optional Analog Ground. See ADC0 Section for details.                                                                                                                                                                                                                                                                                                          |  |  |

| P0.2             | A2     | 2       | 2     | D I/O or<br>A In      | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |

| XTAL1            |        |         |       | A In                  | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See Oscillator Section.                                                                                                                                                                                                                                           |  |  |

| P0.3             | A1     | 1       | 1     | D I/O or<br>A In      | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |

| XTAL2            |        |         |       | A Out<br>D In<br>A In | External Clock Output. This pin is the excitation driver for an<br>external crystal or resonator.<br>External Clock Input. This pin is the external clock input in<br>external CMOS clock mode.<br>External Clock Input. This pin is the external clock input in<br>capacitor or RC oscillator configurations.<br>See Oscillator Section for complete details. |  |  |

| P0.4             | A40    | 79      | 40    | D I/O or<br>A In      | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |

| тх               |        |         |       | D Out                 | UART TX Pin. See Port I/O Section.                                                                                                                                                                                                                                                                                                                             |  |  |

| P0.5             | A39    | 78      | 39    | D I/O or<br>A In      | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |

| RX               |        |         |       | D In                  | UART RX Pin. See Port I/O Section.                                                                                                                                                                                                                                                                                                                             |  |  |

| P0.6             | A38    | 76      | 38    | D I/O or<br>A In      | Port 0.6. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |

| CNVSTR           |        |         |       | D In                  | External Convert Start Input for ADC0. See ADC0 section for a complete description.                                                                                                                                                                                                                                                                            |  |  |

| P0.7             | A37    | 74      | 37    | D I/O or<br>A In      | Port 0.7. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |

| IREF0            |        |         |       | A Out                 | IREF0 Output. See IREF Section for complete description.                                                                                                                                                                                                                                                                                                       |  |  |

# Table 4.4. Digital Supply Current with DC-DC Converter Disabled-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Conditions                                                                                                  | Min       | Тур        | Max                                     | Units    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------|------------|-----------------------------------------|----------|--|

| Digital Supply Current - A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ctive Mode, No Clock Gating (PCLKACT=0                                                                      | x0F)      |            |                                         |          |  |

| (CPU Active, fetching inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                             |           |            |                                         |          |  |

| I <sub>BAT</sub> <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $V_{BAT}$ = 1.8–3.8 V, F = 24.5 MHz<br>(includes precision oscillator current)                              | _         | 4.9        | 6.2                                     | mA       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{BAT}$ = 1.8–3.8 V, F = 20 MHz<br>(includes low power oscillator current)                                | —         | 3.9        |                                         | mA       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{BAT} = 1.8 V, F = 1 MHz$<br>$V_{BAT} = 3.8 V, F = 1 MHz$<br>(includes external oscillator/GPIO current) | _         | 175<br>190 |                                         | μΑ<br>μΑ |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BAT</sub> = 1.8–3.8 V, F = 32.768 kHz<br>(includes SmaRTClock oscillator current)                    | _         | 85         |                                         | μΑ       |  |

| I <sub>BAT</sub> Frequency<br>Sensitivity <sup>1,3,4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>BAT</sub> = 1.8–3.8 V, T = 25 °C                                                                     |           | 183        |                                         | µA/MHz   |  |

| Digital Supply Current - A<br>(CPU Active, fetching inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ctive Mode, All Peripheral Clocks Disablec<br>ructions from flash)                                          | I (PCLI   | (ACT=0     | x00)                                    |          |  |

| I <sub>BAT</sub> <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>BAT</sub> = 1.8–3.8 V, F = 24.5 MHz<br>(includes precision oscillator current)                       |           | 3.9        |                                         | mA       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>BAT</sub> = 1.8–3.8 V, F = 20 MHz<br>(includes low power oscillator current)                         | —         | 3.1        |                                         | mA       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{BAT} = 1.8 V, F = 1 MHz$<br>$V_{BAT} = 3.8 V, F = 1 MHz$<br>(includes external oscillator/GPIO current) | _         | 165<br>180 |                                         | μΑ<br>μΑ |  |

| I <sub>BAT</sub> Frequency<br>Sensitivity <sup>1, 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>BAT</sub> = 1.8–3.8 V, T = 25 °C                                                                     | _         | TBD        |                                         | µA/MHz   |  |

| Notes:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                             |           |            |                                         | L        |  |

| 1. Active Current measure using typical code loop - Digital Supply Current depends upon the particular code being executed. Digital Supply Current depends on the particular code being executed. The values in this table are obtained with the CPU executing a mix of instructions in two loops: djnz R1, \$, followed by a loop that accesses an SFR, and moves data around using the CPU (between accumulator and b-register). The supply current will vary slightly based on the physical location of this code in flash. As described in the Fla Memory chapter, it is best to align the jump addresses with a flash word address (byte location /4), to minimize flash accesses and power consumption. |                                                                                                             |           |            |                                         |          |  |

| 2. Includes oscillator and r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | egulator supply current.                                                                                    |           |            |                                         |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | cterization data; Not production tested.<br>t enabled.                                                      |           |            |                                         |          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                             |           |            |                                         |          |  |

| 5. Low-Power Idle mode of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | urrent measured with CLKMODE = 0x04, PCON =                                                                 | • 0x01, a | and PCL    | <en 0<="" =="" td=""><td>x0F.</td></en> | x0F.     |  |

7. Low-Power Idle mode current measured with CLKMODE = 0x04, PCON = 0x01, and PCLKEN = 0x00.

| Multiplexed Mode |                         |                          |  |  |  |  |

|------------------|-------------------------|--------------------------|--|--|--|--|

| Signal Name      | Por                     | t Pin                    |  |  |  |  |

|                  | 8-Bit Mode <sup>1</sup> | 16-Bit Mode <sup>2</sup> |  |  |  |  |

| RD               | P3.6                    | P3.6                     |  |  |  |  |

| WR               | P3.7                    | P3.7                     |  |  |  |  |

| ALE              | P3.5                    | P3.5                     |  |  |  |  |

| AD0              | P6.0                    | P6.0                     |  |  |  |  |

| AD1              | P6.1                    | P6.1                     |  |  |  |  |

| AD2              | P6.2                    | P6.2                     |  |  |  |  |

| AD3              | P6.3                    | P6.3                     |  |  |  |  |

| AD4              | P6.4                    | P6.4                     |  |  |  |  |

| AD5              | P6.5                    | P6.5                     |  |  |  |  |

| AD6              | P6.6                    | P6.6                     |  |  |  |  |

| AD7              | P6.7                    | P6.7                     |  |  |  |  |

| A8               | —                       | P5.0                     |  |  |  |  |

| A9               | —                       | P5.1                     |  |  |  |  |

| A10              | —                       | P5.2                     |  |  |  |  |

| A11              | —                       | P5.3                     |  |  |  |  |

| A12              | —                       | P5.4                     |  |  |  |  |

| A13              | —                       | P5.5                     |  |  |  |  |

| A14              | —                       | P5.6                     |  |  |  |  |

| A15              | —                       | P5.7                     |  |  |  |  |

|                  | —                       | —                        |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |

| —                | —                       | —                        |  |  |  |  |

| Required I/O:    | 11                      | 19                       |  |  |  |  |

## Table 10.1. EMIF Pinout (C8051F960/3/6)

| Non Multiplexed Mode |                         |                          |  |  |  |

|----------------------|-------------------------|--------------------------|--|--|--|

| Signal Name          | Ро                      | rt Pin                   |  |  |  |

|                      | 8-Bit Mode <sup>1</sup> | 16-Bit Mode <sup>2</sup> |  |  |  |

| RD                   | P3.6                    | P3.6                     |  |  |  |

| WR                   | P3.7                    | P3.7                     |  |  |  |

| D0                   | P6.0                    | P6.0                     |  |  |  |

| D1                   | P6.1                    | P6.1                     |  |  |  |

| D2                   | P6.2                    | P6.2                     |  |  |  |

| D3                   | P6.3                    | P6.3                     |  |  |  |

| D4                   | P6.4                    | P6.4                     |  |  |  |

| D5                   | P6.5                    | P6.5                     |  |  |  |

| D6                   | P6.6                    | P6.6                     |  |  |  |

| D7                   | P6.7                    | P6.7                     |  |  |  |

| A0                   | P5.0                    | P5.0                     |  |  |  |

| A1                   | P5.1                    | P5.1                     |  |  |  |

| A2                   | P5.2                    | P5.2                     |  |  |  |

| A3                   | P5.3                    | P5.3                     |  |  |  |

| A4                   | P5.4                    | P5.4                     |  |  |  |

| A5                   | P5.5                    | P5.5                     |  |  |  |

| A6                   | P5.6                    | P5.6                     |  |  |  |

| A7                   | P5.7                    | P5.7                     |  |  |  |

| A8                   | —                       | P4.0                     |  |  |  |

| A9                   | —                       | P4.1                     |  |  |  |

| A10                  | —                       | P4.2                     |  |  |  |

| A11                  | —                       | P4.3                     |  |  |  |

| A12                  | —                       | P4.4                     |  |  |  |

| A13                  | —                       | P4.5                     |  |  |  |

| A14                  | —                       | P4.6                     |  |  |  |

| A15                  | —                       | P4.7                     |  |  |  |

| Required I/O:        | 18                      | 26                       |  |  |  |

#### Notes:

**1.** Using 8-bit movx instruction without bank select.

2. Using 16-bit movx instruction.

## SFR Definition 10.1. EMI0CN: External Memory Interface Control

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------|---|---|---|---|---|---|---|

| Name  | PGSEL[7:0]      |   |   |   |   |   |   |   |

| Туре  | R/W             |   |   |   |   |   |   |   |

| Reset | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

### SFR Page = 0x0; SFR Address = 0xAA

| Bit | Name       | Function                                                                                                                                                                   |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PGSEL[7:0] | XRAM Page Select Bits.                                                                                                                                                     |

|     |            | The XRAM Page Select Bits provide the high byte of the 16-bit external data memory address when using an 8-bit MOVX command, effectively selecting a 256-byte page of RAM. |

|     |            | 0x00: 0x0000 to 0x00FF                                                                                                                                                     |

|     |            | 0x01: 0x0100 to 0x01FF                                                                                                                                                     |

|     |            | <br>0xFE: 0xFE00 to 0xFEFF<br>0xFF: 0xFF00 to 0xFFFF                                                                                                                       |

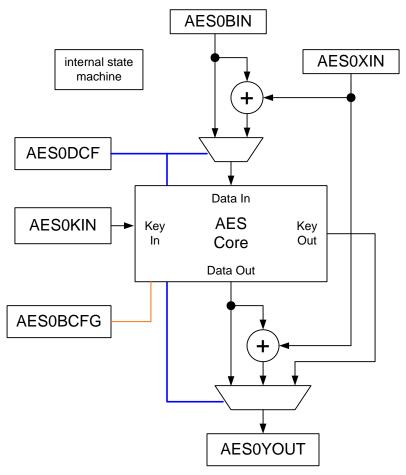

## 14.1. Hardware Description

Figure 14.1. AES Peripheral Block Diagram

The AES Encryption module consists of these elements.

- AES Encryption/Decryption Core

- Configuration sfrs

- Key input sfr

- Data sfrs

- Input Multiplexer

- Output Multiplexer

- Input Exclusive OR block

- Output Exclusive OR block

- Internal State Machine

176

#### 14.4.1. AES Block Cipher Encryption using DMA

Normally, the AES block is used with the DMA. This provides the best performance and lowest power consumption. Code examples are provided in 8051 compiler independent C code using the DMA. It is highly recommended to use with the code examples. The steps are documented in the datasheet for completeness.

Steps to encrypt data using Simple AES block encryption (ECB mode)

- Prepare encryption Key and data to be encrypted in xram.

- Reset AES module by clearing bit 2 of AES0BCFG.

- Disable the first three DMA channels by clearing bits 0 to 2 in the DMA0EN sfr.

- Configure the first DMA channel for the AES0KIN sfr

- Select the first DMA channel by writing 0x00 to the DMA0SEL sfr

- Configure the second DMA channel to move xram to AES0KIN sfr by writing 0x05 to the DMA0NCF sfr

- Write 0x01 tDMA0NMD to enable wrapping

- Write the xram location of encryption key to the DMA0NBAH and DMA0NBAL sfrs.

- Write the key length in bytes to the DMA0NSZL sfr

- Clear the DMA0NSZH sfr

- Clear the DMA0NAOH and DMA0NAOL sfrs.

- Configure the second DMA channel for the AES0BIN sfr.

- Select the second DMA channel by writing 0x01 to the DMA0SEL sfr.

- Configure the second DMA channel to move xram to the AES0BIN sfr by writing 0x06 to the DMA0NCF sfr.

- Clear DMA0NMD to disable wrapping.

- Write the xram address of the data to be encrypted to the DMA0NBAH and DMA0NBAL sfrs.

- Write the number of bytes to be encrypted in multiples of 16 bytes to the DMA0NSZH and DMA0NSZL sfrs.

- Clear the DMA0NAOH and DMA0NAOL sfrs.

- Configure the third DMA channel for the AES0YOUT sfr

- Select the third DMA channel by writing 0x02 to the DMA0SEL sfr

- Configure the third DMA channel to move the contents of the AES0YOUT sfr to xram by writing 0x08 to the DMA0NCF sfr.

- Enable transfer complete interrupt by setting bit 7 of DMA0NCF sfr.

- Clear DMA0NMD to disable wrapping.

- Write the xram address for encrypted data to the DMA0NBAH and DMA0NBAL sfrs.

- Write the number of bytes to be encrypted in multiples of 16 bytes to the DMA0NSZH and DMA0NSZL sfrs.

- Clear the DMA0NAOH and DMA0NAOL sfrs.

- Clear first three DMA interrupts by clearing bits 0 to 2 in the DMA0INT sfr.

- Enable first three DMA channels setting bits 0 to 2 in the DMA0EN sfr

- Configure the AES Module data flow for AES Block Cipher by writing 0x00 to the AES0DCFG sfr.

- Write key size to bits 1 and 0 of the AES0BCFG

- Configure the AES core for encryption by setting the bit 2 of AES0BCFG

- Initiate the encryption operation be setting bit 3 of AES0BCFG

- Wait on the DMA interrupt from DMA channel 2

- Disable the AES Module by clearing bit 2 of AES0BCFG

- Disable the DMA by writing 0x00 to DMA0EN

## SFR Definition 14.3. AES0BIN: AES Block Input

| Bit   | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | AESOBIN[7:0] |     |     |     |     |     |     |     |

| Туре  | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

### SFR Address = 0xEB; SFR page = 0x2; Not bit-Addressable

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | AES0BIN[7:0] | AES Block Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |              | During an encryption operation, the plaintext is written to the AES0BIN sfr. During<br>an decryption operation, the ciphertext is written to the AES0BIN sfr. During a key<br>inversion the encryption key is written to AES0BIN.<br>When used with the DMA, the DMA will write directly to this sfr.<br>The AES0BIN may be used in conjunction with the AES0XIN sfr for some cipher<br>block modes.<br>When used without the DMA, AES0BIN, AES0XIN, and AES0KIN must be written<br>in sequence.<br>Reading this register will yield the last value written. This can be used for debug<br>purposes. |

9. Restore previous interrupt state.

Steps 4–7 must be repeated for each 1024-byte page to be erased.

#### Notes:

- 1. Flash security settings may prevent erasure of some flash pages, such as the reserved area and the page containing the lock bytes. For a summary of flash security settings and restrictions affecting flash erase operations, please see Section "18.3. Security Options" on page 252.

- 2. 8-bit MOVX instructions cannot be used to erase or write to flash memory at addresses higher than 0x00FF.

#### 18.1.3. Flash Write Procedure

A write to flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in flash. A byte location to be programmed should be erased before a new value is written.

The recommended procedure for writing a single byte in flash is as follows:

- 1. Save current interrupt state and disable interrupts.

- 2. Set the PSWE bit (register PSCTL).

- 3. Clear the PSEE bit (register PSCTL).

- 4. If writing to an address in Banks 1, 2, or 3, set the COBANK[1:0] bits (register PSBANK) for the appropriate bank.

- 5. Ensure that the flash byte has been erased (has a value of 0xFF).

- 6. Write the first key code to FLKEY: 0xA5.

- 7. Write the second key code to FLKEY: 0xF1.

- 8. Using the MOVX instruction, write a single data byte to the desired location within the 1024-byte sector.

- 9. Clear the PSWE bit.

- 10. Restore previous interrupt state.

Steps 2-8 must be repeated for each byte to be written.

#### Notes:

- 1. Flash security settings may prevent writes to some areas of flash, such as the reserved area. For a summary of flash security settings and restrictions affecting flash write operations, please see Section "18.3. Security Options" on page 252.

- 2. 8-bit MOVX instructions cannot be used to erase or write to flash memory at addresses higher than 0x00FF.

The level of flash security depends on the flash access method. The three flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 18.1 summarizes the flash security features of the C8051F96x devices.

| Action                                                                   | C2 Debug                | User Firmware e   | executing from:   |  |

|--------------------------------------------------------------------------|-------------------------|-------------------|-------------------|--|

|                                                                          | Interface               | an unlocked page  | a locked page     |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)      | Permitted               | Permitted         | Permitted         |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)        | Not Permitted           | Flash Error Reset | Permitted         |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)      | Permitted               | Permitted         | Permitted         |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)       | Not Permitted           | Flash Error Reset | Permitted         |  |

| Read contents of Lock Byte<br>(if no pages are locked)                   | Permitted               | Permitted         | Permitted         |  |

| Read contents of Lock Byte<br>(if any page is locked)                    | Not Permitted           | Flash Error Reset | Permitted         |  |

| Erase page containing Lock Byte<br>(if no pages are locked)              | Permitted               | Flash Error Reset | Flash Error Reset |  |

| Erase page containing Lock Byte—Unlock all pages (if any page is locked) | C2 Device Erase<br>Only | Flash Error Reset | Flash Error Reset |  |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)              | Not Permitted           | Flash Error Reset | Flash Error Reset |  |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)            | Not Permitted           | Flash Error Reset | Flash Error Reset |  |

| Read, Write or Erase Reserved Area                                       | Not Permitted           | Flash Error Reset | Flash Error Reset |  |

| Table 18.1. | Flash   | Security | Summarv |

|-------------|---------|----------|---------|

|             | 1 10011 | occurry  | Gammary |

C2 Device Erase—Erases all flash pages including the page containing the Lock Byte.

Flash Error Reset—Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset).

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

### 18.5. Flash Write and Erase Guidelines

Any system which contains routines which write or erase flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of VDD, system clock frequency, or temperature. This accidental execution of flash modifying code can result in alteration of flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of flash by firmware, the VDD Monitor must be enabled and enabled as a reset source on C8051F96x devices for the flash to be successfully modified. If either the VDD Monitor or the VDD Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the flash.

The following guidelines are recommended for any system that contains routines which write or erase flash from code.

#### 18.5.1. VDD Maintenance and the VDD Monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the minimum VDD rise time specification of 1 ms is met. If the system cannot meet this rise time specification, then add an external VDD brownout circuit to the RST pin of the device that holds the device in reset until VDD reaches the minimum device operating voltage and reasserts RST if VDD drops below the minimum device operating voltage.

- 3. Keep the on-chip VDD Monitor enabled and enable the VDD Monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the 'C' compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the VDD Monitor and enabling the VDD Monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories web site.

#### Notes:

On C8051F96x devices, both the VDD Monitor and the VDD Monitor reset source must be enabled to write or erase flash without generating a Flash Error Device Reset.

On C8051F96x devices, both the VDD Monitor and the VDD Monitor reset source are enabled by hardware after a power-on reset.

- 4. As an added precaution, explicitly enable the VDD Monitor and enable the VDD Monitor as a reset source inside the functions that write and erase flash memory. The VDD Monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the flash write or erase operation instruction.

- 5. Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct, but "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a '1'. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

## SFR Definition 18.7. FRBCN: Flash Read Buffer Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0      |

|-------|---|---|---|---|---|---|------|--------|

| Name  |   |   |   |   |   |   | FRBD | CHBLKW |

| Туре  | R | R | R | R | R | R | R/W  | R/W    |

| Reset | 0 | 0 | 1 | 0 | 0 | 0 | 0    | 0      |

### SFR Page = 0xF; SFR Address = 0xB5

| Bit | Name   | Function                                                                                                                                                                                                                                         |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b. Write = don't care.                                                                                                                                                                                                              |

| 1   | FRBD   | Flash Read Buffer Disable Bit.<br>0: Flash read buffer is enabled and being used.<br>1: Flash read buffer is disabled and bypassed.                                                                                                              |

| 0   | CHBLKW | <ul> <li>Block Write Enable Bit.</li> <li>This bit allows block writes to flash memory from firmware.</li> <li>0: Each byte of a software flash write is written individually.</li> <li>1: Flash bytes are written in groups of four.</li> </ul> |

## SFR Definition 19.6. PMU0MD: Power Management Unit Mode

| Bit   | 7     | 6      | 5      | 4   | 3   | 2   | 1   | 0   |

|-------|-------|--------|--------|-----|-----|-----|-----|-----|

| Name  | RTCOE | WAKEOE | MONDIS |     |     |     |     |     |

| Туре  | R/W   | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W |

| Reset | 0     | 0      | 0      | 0   | 0   | 0   | 0   | 0   |

## SFR Page = 0x0; SFR Address = 0xB6

| Bit | Name   | Function                                                                                                                                               |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RTCOE  | Buffered SmaRTClock Output Enable.                                                                                                                     |

|     |        | Enables the buffered SmaRTClock oscillator output on P0.2.<br>0: Buffered SmaRTClock output not enabled.<br>1: Buffered SmaRTClock output not enabled. |

| 6   | WAKEOE | Wakeup Request Output Enable.                                                                                                                          |

|     |        | Enables the Sleep Mode wake-up request signal on P0.3.                                                                                                 |

|     |        | 0: Wake-up request signal is not enabled.                                                                                                              |

|     |        | 1: Wake-up request signal is enabled.                                                                                                                  |

| 5   | MONDIS | POR Supply Monitor Disable.                                                                                                                            |

|     |        | Writing a 1 to this bit disables the POR supply monitor.                                                                                               |

| 4:0 | Unused | Read = 00000b. Write = Don't Care.                                                                                                                     |

## 23.1. Programmable Precision Internal Oscillator

All C8051F96x devices include a programmable precision internal oscillator that may be selected as the system clock. OSCICL is factory calibrated to obtain a 24.5 MHz frequency. See Section "4. Electrical Characteristics" on page 56 for complete oscillator specifications.

The precision oscillator supports a spread spectrum mode which modulates the output frequency in order to reduce the EMI generated by the system. When enabled (SSE = 1), the oscillator output frequency is modulated by a stepped triangle wave whose frequency is equal to the oscillator frequency divided by 384 (63.8 kHz using the factory calibration). The deviation from the nominal oscillator frequency is +0%, -1.6%, and the step size is typically 0.26% of the nominal frequency. When using this mode, the typical average oscillator frequency is lowered from 24.5 MHz to 24.3 MHz.

### 23.2. Low Power Internal Oscillator

All C8051F96x devices include a low power internal oscillator that defaults as the system clock after a system reset. The low power internal oscillator frequency is 20 MHz  $\pm$  10% and is automatically enabled when selected as the system clock and disabled when not in use. See Section "4. Electrical Characteristics" on page 56 for complete oscillator specifications.

## 23.3. External Oscillator Drive Circuit

All C8051F96x devices include an external oscillator circuit that may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. Figure 23.1 shows a block diagram of the four external oscillator options. The external oscillator is enabled and configured using the OSCXCN register.

The external oscillator output may be selected as the system clock or used to clock some of the digital peripherals (e.g., Timers, PCA, etc.). See the data sheet chapters for each digital peripheral for details. See Section "4. Electrical Characteristics" on page 56 for complete oscillator specifications.

#### 23.3.1. External Crystal Mode

If a crystal or ceramic resonator is used as the external oscillator, the crystal/resonator and a 10 M $\Omega$  resistor must be wired across the XTAL1 and XTAL2 pins as shown in Figure 23.1, Option 1. Appropriate loading capacitors should be added to XTAL1 and XTAL2, and both pins should be configured for analog I/O with the digital output drivers disabled.

Figure 23.2 shows the external oscillator circuit for a 20 MHz quartz crystal with a manufacturer recommended load capacitance of 12.5 pF. Loading capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins. The total value of the each loading capacitor and the stray capacitance of each XTAL pin should equal 12.5 pF x 2 = 25 pF. With a stray capacitance of 10 pF per pin, the 15 pF capacitors yield an equivalent series capacitance of 12.5 pF across the crystal.

**Note:** The recommended load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

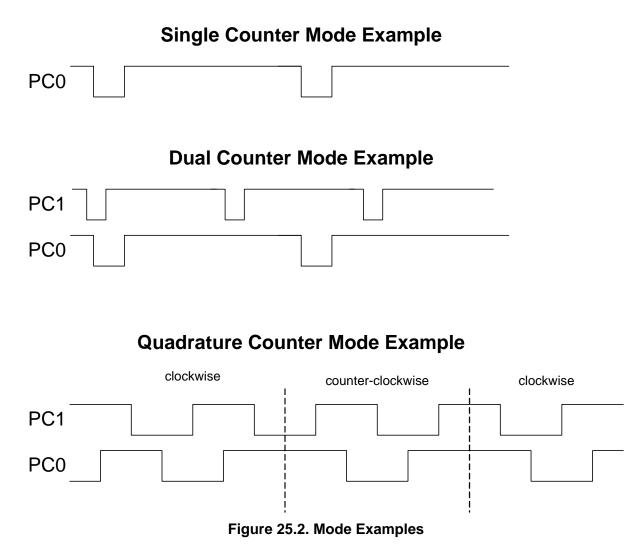

## 25.1. Counting Modes

The Pulse Counter supports three different counting modes: single counter mode, dual counter mode, and quadrature counter mode. Figure 25.2 illustrates the three counter modes.

The single counter mode uses only one Pulse Counter pin PC0 (P1.0) to count pulses from a single input channel. This mode uses only counter 0 and comparator. (Counter 1 and comparator 1 are not used.) The single counter mode supports only one meter-encoder with a single-channel output. A single-channel encoder is an effective solution when the metered fluid flows only in one direction. A single-channel encoder does not provide any direction information and does not support bidirectional fluid metering.

The dual counter mode supports two independent single-channel meters. Each meter has its own independent counter and comparator. Some of the global configuration settings apply to both channels, such as pull-up current, sampling rate, and debounce time. The dual mode may also be used for a redundant count using a two-channel non-quadrature encoder.

Quadrature counter mode supports a single two-channel quadrature meter encoder. The quadrature counter mode supports bidirectional encoders and applications with bidirectional fluid flow. In quadrature counter mode, clock-wise counts will increment counter 0, while counter clock-wise counts will increment counter 1. Subtracting counter 1 from counter 0 will yield the net position. If the normal fluid flow is clock-

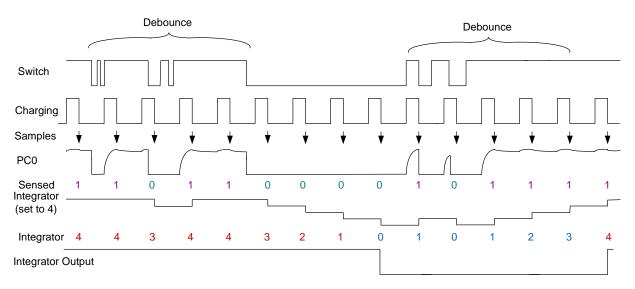

enable signal. The enable signal enables the pull-up resistor when high and disables when low. PC0 is the line to the reed switch. On the right side of PC0 waveform, the line voltage is decreasing towards ground when the pull-up resistors are disabled. Beneath the charging waveform, the arrows represent the sample points. The pulse counter samples the PC0 voltage once the charging completes. The sensed ones and zeros are the sampled data. Finally the integrator waveform illustrates the output of the digital integrator. The integrator is set to 4 initially and counts to down to 0 before toggling the output low. Once the integrator reaches the low state, it needs to count up to 4 before toggling its output to the high state. The debounce logic filters out switch bounce or noise that appears for a short duration.

Figure 25.4. Debounce Timing

## 25.7. Reset Behavior

Unlike most MCU peripherals, an MCU reset does not completely reset the Pulse Counter. This includes a power on reset and all other reset sources. An MCU reset does not clear the counter values. The Pulse Counter SFRs do not reset to a default value upon reset. The 24-bit counter values are persistent unless cleared manually by writing to the PC0MD SFR. Note that if the VBAT voltage ever drops below the minimum operating voltage, this may compromise contents of the counters.

The PC0MD register should normally be written only once after reset. The PC0MD SFR is the master mode register. This register sets the counter mode and sample rate. Writing to the PC0MD SFR also resets the other PC0xxx SFRs.

Note that the RTC clock will reset on an MCU reset, so counting cannot resume until the RTC clock has been re-started.

Firmware should read the reset sources SFR RSTSRC to determine the source of the last reset and initialize the Pulse Counter accordingly.

When the pulse counter resets, it takes some time (typically two RTC clock cycles) to synchronize between internal clock domains. The counters do not increment during this synchronization time.

## 25.8. Wake up and Interrupt Sources

The Pulse Counter has multiple interrupt and wake-up source conditions. To enable an interrupt, enable the source in the PC0INT0/1 SFRs and enable the Pulse Counter interrupt using bit 4 of the EIE2 bit register. The Pulse Counter interrupt service routine should read the interrupt flags in PC0INT0/1 to determine the source of the interrupt and clear the interrupt flags.

## SFR Definition 25.6. PC0DCL: PC0 Debounce Configuration Low

| Bit   | 7           | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------|-----|---|---|---|---|---|---|--|

| Name  | PC0DCL[7:0] |     |   |   |   |   |   |   |  |

| Туре  |             | R/W |   |   |   |   |   |   |  |

| Reset | 0           | 0   | 0 | 0 | 0 | 1 | 0 | 0 |  |

SFR Address = 0xF9; SFR Page = 0x2

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PC0DCL[7:0] | Pulse Counter Debounce Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |             | Number of cumulative good samples seen by the integrator before recogniz-<br>ing the input as low. Setting PC0DCL to 0x00 will disable integrators on both<br>PC0 and PC1. The actual value used is PC0DCL plus one. Sampling a low<br>decrements while sampling a high increments the count. Switch bounce<br>produces a random looking signal. The worst case would be to bounce high<br>at each sample point and not start decrementing the integrator until the<br>switch bounce settled. Therefore, minimum pulse width should account for<br>twice the debounce time. For example, using a sample rate of 1 ms and a<br>PC0DCL value of 0x09 will look for 10 cumulative lows before recognizing<br>the input as low (1 ms x 10 = 10 ms). The minimum pulse width should be<br>20 ms or greater for this example. If PC0DCL has a value of 0x03 and the<br>sample rate is 500 µs, the integrator would need to see 4 cumulative lows<br>before recognizing the low (500 µs x 4 = 2 ms). The minimum pulse width<br>should be 4 ms for this example. |

## SFR Definition 25.7. PC0CTR0H: PC0 Counter 0 High (MSB)

| Bit    | 7                    | 6                                       | 5           | 4 | 3 | 2 | 1 | 0 |  |  |  |

|--------|----------------------|-----------------------------------------|-------------|---|---|---|---|---|--|--|--|

| Name   | Name PC0CTR0H[23:16] |                                         |             |   |   |   |   | L |  |  |  |

| Type R |                      |                                         |             |   |   |   |   |   |  |  |  |

| Reset  | : 0                  | 0                                       | 0 0 0 0 0 0 |   |   |   |   |   |  |  |  |

| SFR A  | ddress = 0xD         | C; SFR Pa                               | ge = 0x2    |   |   |   |   |   |  |  |  |

| Bit    | Name                 | ;                                       | Function    |   |   |   |   |   |  |  |  |

| 7.0    | релетран             | PC0CTP0HI23:161 PC0 Counter 0 High Byte |             |   |   |   |   |   |  |  |  |

| 7:0 | PC0CTR0H[23:16] | PC0 Counter 0 High Byte  |

|-----|-----------------|--------------------------|

|     |                 | Bits 23:16 of Counter 0. |

## SFR Definition 25.8. PC0CTR0M: PC0 Counter 0 Middle

| Bit   | 7                   | 6           | 5                                                    | 4 | 3     | 2   | 1 | 0 |

|-------|---------------------|-------------|------------------------------------------------------|---|-------|-----|---|---|

| Nam   | Name PC0CTR0M[15:8] |             |                                                      |   |       |     |   |   |

| Туре  | Type R              |             |                                                      |   |       |     |   |   |

| Rese  | t 0                 | 0           | 0                                                    | 0 | 0     | 0   | 0 | 0 |

| SFR A | ddress = 0xD        | 8; SFR Page | e = 0x2                                              |   |       |     |   |   |

| Bit   | Name                | ;           |                                                      |   | Funct | ion |   |   |

| 7:0   | PC0CTR0M            |             | PC0 Counter 0 Middle Byte<br>Bits 15:8 of Counter 0. |   |       |     |   |   |

## SFR Definition 25.9. PC0CTR0L: PC0 Counter 0 Low (LSB)

| Bit   | 7             | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------------|-----------------|---|---|---|---|---|---|--|--|--|

| Name  | PC0CTR0L[7:0] |                 |   |   |   |   |   |   |  |  |  |

| Туре  |               | R               |   |   |   |   |   |   |  |  |  |

| Reset | 0             | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

SFR Address = 0xDA; SFR Page = 0x2

| Bit | Name          | Function               |

|-----|---------------|------------------------|

| 7:0 | PC0CTR0L[7:0] | PC0 Counter 0 Low Byte |

|     |               | Bits 7:0 of Counter 0. |

**Note:** PC0CTR0L must be read before PC0CTR0M and PC0CTR0H to latch the count for reading. PC0CTRL must be qualified using the RDVALID bit (PC0TH[0]).

## SFR Definition 31.2. SPI1CN: SPI1 Control

| Bit   | 7    | 6    | 5    | 4      | 3          | 2 | 1     | 0     |

|-------|------|------|------|--------|------------|---|-------|-------|

| Name  | SPIF | WCOL | MODF | RXOVRN | NSSMD[1:0] |   | TXBMT | SPIEN |

| Туре  | R/W  | R/W  | R/W  | R/W    | R/W        |   | R     | R/W   |

| Reset | 0    | 0    | 0    | 0      | 0          | 1 | 1     | 0     |

# SFR Page = 0x0; SFR Address = 0xF8; Bit-Addressable

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF       | SPI1 Interrupt Flag.                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit is set to logic 1 by hardware at the end of a data transfer. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                                                                                     |

| 6   | WCOL       | Write Collision Flag.                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | This bit is set to logic 1 if a write to SPI1DAT is attempted when TXBMT is 0. When this occurs, the write to SPI1DAT will be ignored, and the transmit buffer will not be written. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                       |

| 5   | MODF       | Mode Fault Flag.                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                             |

| 4   | RXOVRN     | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI1 shift register. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                         |

| 3:2 | NSSMD[1:0] | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | Selects between the following NSS operation modes:<br>(See Section 31.2 and Section 31.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |