Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                         |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 57                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 8.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                      |

| Data Converters            | A/D 16x10b/12b                                                   |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 80-TQFP                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f964-a-gq |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 15. Encoder/Decoder                                     | 207 |

|---------------------------------------------------------|-----|

| 15.1. Manchester Encoding                               | 208 |

| 15.2. Manchester Decoding                               |     |

| 15.3. Three-out-of-Six Encoding                         | 210 |

| 15.4. Three-out-of-Six Decoding                         | 211 |

| 15.5. Encoding/Decoding with SFR Access                 | 212 |

| 15.6. Decoder Error Interrupt                           | 212 |

| 15.7. Using the ENC0 module with the DMA                | 213 |

| 16. Special Function Registers                          | 216 |

| 16.1. SFR Paging                                        | 216 |

| 16.2. Interrupts and SFR Paging                         | 216 |

| 16.3. SFR Page Stack Example                            | 218 |

| 17. Interrupt Handler                                   |     |

| 17.1. Enabling Interrupt Sources                        | 237 |

| 17.2. MCU Interrupt Sources and Vectors                 | 237 |

| 17.3. Interrupt Priorities                              | 238 |

| 17.4. Interrupt Latency                                 |     |

| 17.5. Interrupt Register Descriptions                   | 240 |

| 17.6. External Interrupts INT0 and INT1                 | 247 |

| 18. Flash Memory                                        |     |

| 18.1. Programming the Flash Memory                      |     |

| 18.1.1. Flash Lock and Key Functions                    |     |

| 18.1.2. Flash Erase Procedure                           |     |

| 18.1.3. Flash Write Procedure                           |     |

| 18.1.4. Flash Write Optimization                        |     |

| 18.2. Non-volatile Data Storage                         |     |

| 18.3. Security Options                                  |     |

| 18.4. Determining the Device Part Number at Run Time    |     |

| 18.5. Flash Write and Erase Guidelines                  |     |

| 18.5.1. VDD Maintenance and the VDD Monitor             |     |

| 18.5.2. PSWE Maintenance                                |     |

| 18.5.3. System Clock                                    |     |

| 18.6. Minimizing Flash Read Current                     |     |

| 19. Power Management                                    |     |

| 19.1. Normal Mode                                       |     |

| 19.2. Idle Mode                                         |     |

| 19.3. Stop Mode                                         |     |

| 19.4. Low Power Idle Mode                               |     |

| 19.5. Suspend Mode                                      |     |

| 19.6. Sleep Mode                                        |     |

| 19.7. Configuring Wakeup Sources                        |     |

| 19.8. Determining the Event that Caused the Last Wakeup |     |

| 19.9. Power Management Specifications                   |     |

| 20. On-Chip DC-DC Buck Converter (DC0)                  |     |

| 20.1. Startup Behavior                                  | 275 |

## Table 4.4. Digital Supply Current with DC-DC Converter Disabled (Continued)

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                                                                | Conditions                                                                                                  | Min | Тур              | Max | Units    |  |  |  |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|------------------|-----|----------|--|--|--|

| Digital Supply Current—Idle Mode<br>(CPU Inactive, not Fetching Instructions from Flash) |                                                                                                             |     |                  |     |          |  |  |  |

| I <sub>BAT</sub> <sup>2</sup>                                                            | V <sub>BAT</sub> = 1.8–3.8 V, F = 24.5 MHz<br>(includes precision oscillator current)                       |     | 3.5              | —   | mA       |  |  |  |

|                                                                                          | V <sub>BAT</sub> = 1.8–3.8 V, F = 20 MHz<br>(includes low power oscillator current)                         |     | 2.6              | —   | mA       |  |  |  |

|                                                                                          | $V_{BAT}$ = 1.8 V, F = 1 MHz<br>$V_{BAT}$ = 3.8 V, F = 1 MHz<br>(includes external oscillator/GPIO current) | _   | 340<br>360       |     | μΑ<br>μΑ |  |  |  |

|                                                                                          | V <sub>BAT</sub> = 1.8–3.8 V, F = 32.768 kHz<br>(includes SmaRTClock oscillator current)                    | —   | 230 <sup>5</sup> | —   | μA       |  |  |  |

| I <sub>BAT</sub> Frequency Sensitivity <sup>3</sup>                                      | V <sub>BAT</sub> = 1.8–3.8 V, T = 25 °C                                                                     |     | 135              | —   | µA/MHz   |  |  |  |

Notes:

- Active Current measure using typical code loop Digital Supply Current depends upon the particular code being executed. Digital Supply Current depends on the particular code being executed. The values in this table are obtained with the CPU executing a mix of instructions in two loops: djnz R1, \$, followed by a loop that accesses an SFR, and moves data around using the CPU (between accumulator and b-register). The supply current will vary slightly based on the physical location of this code in flash. As described in the Flash Memory chapter, it is best to align the jump addresses with a flash word address (byte location /4), to minimize flash accesses and power consumption.

- 2. Includes oscillator and regulator supply current.

- **3.** Based on device characterization data; Not production tested.

- 4. Measured with one-shot enabled.

- 5. Low-Power Idle mode current measured with CLKMODE = 0x04, PCON = 0x01, and PCLKEN = 0x0F.

- 6. Using SmaRTClock osillator with external 32.768 kHz CMOS clock. Does not include crystal bias current.

- 7. Low-Power Idle mode current measured with CLKMODE = 0x04, PCON = 0x01, and PCLKEN = 0x00.

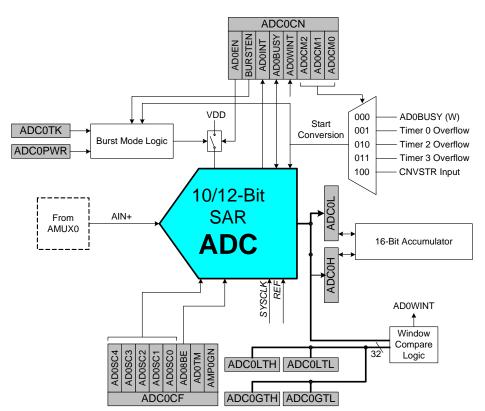

# 5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

The ADC0 on C8051F96x devices is a 300 ksps, 10-bit or 75 ksps, 12-bit successive-approximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results. See Section 5.4 for more details on using the ADC in 12-bit mode.

The ADC is fully configurable under software control via Special Function Registers. The ADC0 operates in Single-ended mode and may be configured to measure various different signals using the analog multiplexer described in "5.7. ADC0 Analog Multiplexer" on page 95. The voltage reference for the ADC is selected as described in "5.9. Voltage and Ground Reference Options" on page 100.

Figure 5.1. ADC0 Functional Block Diagram

## 5.1. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the AD0SJST[2:0]. When the repeat count is set to 1, conversion codes are represented as 10bit unsigned integers. Inputs are measured from 0 to VREF x 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to 0.

## 5.8. Temperature Sensor

An on-chip temperature sensor is included on the C8051F96x which can be directly accessed via the ADC multiplexer in single-ended configuration. To use the ADC to measure the temperature sensor, the ADC mux channel should select the temperature sensor. The temperature sensor transfer function is shown in Figure 5.8. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the ADC multiplexer is set correctly. The TEMPE bit in register REFOCN enables/disables the temperature sensor, as described in SFR Definition 5.15. REFOCN: Voltage Reference Control. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 4.12 for the slope and offset parameters of the temperature sensor.

Figure 5.8. Temperature Sensor Transfer Function

#### 5.8.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 4.13 for linearity specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. Typically a 1-point (offset) calibration includes the following steps:

- 1. Control/measure the ambient temperature (this temperature must be known).

- 2. Power the device, and delay for a few seconds to allow for self-heating.

- 3. Perform an ADC conversion with the temperature sensor selected as the positive input and GND selected as the negative input.

- 4. Calculate the offset characteristics, and store this value in non-volatile memory for use with subsequent temperature sensor measurements.

# 6. Programmable Current Reference (IREF0)

C8051F96x devices include an on-chip programmable current reference (source or sink) with two output current settings: Low Power Mode and High Current Mode. The maximum current output in Low Power Mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in High Current Mode is 504  $\mu$ A (8  $\mu$ A steps).

The current source/sink is controlled though the IREF0CN special function register. It is enabled by setting the desired output current to a non-zero value. It is disabled by writing 0x00 to IREF0CN. The port I/O pin associated with ISRC0 should be configured as an analog input and skipped in the Crossbar. See "Port Input/Output" on page 356 for more details.

## SFR Definition 6.1. IREF0CN: Current Reference Control

| Bit   | 7    | 6    | 5        | 4   | 3 | 2 | 1 | 0 |

|-------|------|------|----------|-----|---|---|---|---|

| Name  | SINK | MODE | IREF0DAT |     |   |   |   |   |

| Туре  | R/W  | R/W  |          | R/W |   |   |   |   |

| Reset | 0    | 0    | 0        | 0   | 0 | 0 | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xB9

| Bit | Name          | Function                                                                                                                                                                                           |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SINK          | IREF0 Current Sink Enable.                                                                                                                                                                         |

|     |               | Selects if IREF0 is a current source or a current sink.                                                                                                                                            |

|     |               | 0: IREF0 is a current source.                                                                                                                                                                      |

|     |               | 1: IREF0 is a current sink.                                                                                                                                                                        |

| 6   | MDSEL         | IREF0 Output Mode Select.                                                                                                                                                                          |

|     |               | Selects Low Power or High Current Mode.                                                                                                                                                            |

|     |               | 0: Low Power Mode is selected (step size = 1 $\mu$ A).                                                                                                                                             |

|     |               | 1: High Current Mode is selected (step size = 8 $\mu$ A).                                                                                                                                          |

| 5:0 | IREF0DAT[5:0] | IREF0 Data Word.                                                                                                                                                                                   |

|     |               | Specifies the number of steps required to achieve the desired output current.<br>Output current = direction x step size x IREF0DAT.<br>IREF0 is in a low power state when IREF0DAT is set to 0x00. |

## 6.1. PWM Enhanced Mode

The precision of the current reference can be increased by fine tuning the IREF0 output using a PWM signal generated by the PCA. This mode allows the IREF0DAT bits to perform a course adjustment on the IREF0 output. Any available PCA channel can perform a fine adjustment on the IREF0 output. When enabled (PWMEN = 1), the CEX signal selected using the PWMSS bit field is internally routed to IREF0 to control the on time of a current source having the weight of 2 LSBs. With the two least significant bits of IREF0DAT set to 00b, applying a 100% duty cycle on the CEX signal will be equivalent to setting the two LSBs of IREF0DAT to 10b. PWM enhanced mode is enabled and setup using the IREF0CF register.

# SFR Definition 7.5. CPT0MX: Comparator0 Input Channel Select

| Bit   | 7   | 6          | 5   | 4   | 3   | 2          | 1   | 0   |  |

|-------|-----|------------|-----|-----|-----|------------|-----|-----|--|

| Name  |     | CMX0N[3:0] |     |     |     | CMX0P[3:0] |     |     |  |

| Туре  | R/W | R/W        | R/W | R/W | R/W | R/W        | R/W | R/W |  |

| Reset | 1   | 1          | 1   | 1   | 1   | 1          | 1   | 1   |  |

SFR Page = 0x0; SFR Address = 0x9F

| Bit | Name  |       | Function                                                            |            |                        |  |  |  |

|-----|-------|-------|---------------------------------------------------------------------|------------|------------------------|--|--|--|

| 7:4 | CMX0N | -     | <b>0 Negative Input Selection.</b><br>negative input channel for Co |            |                        |  |  |  |

|     |       | 0000: | P0.1                                                                | 1000:      | P2.1                   |  |  |  |

|     |       | 0001: | P0.3                                                                | 1001:      | P2.3                   |  |  |  |

|     |       | 0010: | P0.5                                                                | 1010:      | Reserved               |  |  |  |

|     |       | 0011: | Reserved                                                            | 1011:      | Reserved               |  |  |  |

|     |       | 0100: | Reserved                                                            | 1100:      | Compare                |  |  |  |

|     |       | 0101: | Reserved                                                            | 1101:      | VBAT divided by 2      |  |  |  |

|     |       | 0110: | P1.5                                                                | 1110:      | Digital Supply Voltage |  |  |  |

|     |       | 0111: | P1.7                                                                | 1111:      | Ground                 |  |  |  |

| 3:0 | CMX0P | -     | r0 Positive Input Selection. positive input channel for Comparison  | nparator0. |                        |  |  |  |

|     |       | 0000: | P0.0                                                                | 1000:      | P2.0                   |  |  |  |

|     |       | 0001: | P0.2                                                                | 1001:      | P2.2                   |  |  |  |

|     |       | 0010: | P0.4                                                                | 1010:      | Reserved               |  |  |  |

|     |       | 0011: | P0.6                                                                | 1011:      | Reserved               |  |  |  |

|     |       | 0100: | Reserved                                                            | 1100:      | Compare                |  |  |  |

|     |       | 0101: | Reserved                                                            | 1101:      | VBAT divided by 2      |  |  |  |

|     |       | 0110: | P1.4                                                                | 1110:      | VBAT Supply Voltage    |  |  |  |

|     |       | 0111: | P1.6                                                                | 1111:      | VBAT Supply Voltage    |  |  |  |

| Multiplexed Mode |                         |                          |  |  |  |  |  |

|------------------|-------------------------|--------------------------|--|--|--|--|--|

| Signal Name      | Por                     | t Pin                    |  |  |  |  |  |

|                  | 8-Bit Mode <sup>1</sup> | 16-Bit Mode <sup>2</sup> |  |  |  |  |  |

| RD               | P3.6                    | P3.6                     |  |  |  |  |  |

| WR               | P3.7                    | P3.7                     |  |  |  |  |  |

| ALE              | P3.5                    | P3.5                     |  |  |  |  |  |

| AD0              | P6.0                    | P6.0                     |  |  |  |  |  |

| AD1              | P6.1                    | P6.1                     |  |  |  |  |  |

| AD2              | P6.2                    | P6.2                     |  |  |  |  |  |

| AD3              | P6.3                    | P6.3                     |  |  |  |  |  |

| AD4              | P6.4                    | P6.4                     |  |  |  |  |  |

| AD5              | P6.5                    | P6.5                     |  |  |  |  |  |

| AD6              | P6.6                    | P6.6                     |  |  |  |  |  |

| AD7              | P6.7                    | P6.7                     |  |  |  |  |  |

| A8               | —                       | P5.0                     |  |  |  |  |  |

| A9               | —                       | P5.1                     |  |  |  |  |  |

| A10              | —                       | P5.2                     |  |  |  |  |  |

| A11              | —                       | P5.3                     |  |  |  |  |  |

| A12              | —                       | P5.4                     |  |  |  |  |  |

| A13              | —                       | P5.5                     |  |  |  |  |  |

| A14              | —                       | P5.6                     |  |  |  |  |  |

| A15              | —                       | P5.7                     |  |  |  |  |  |

|                  | —                       | —                        |  |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |  |

| _                | —                       | —                        |  |  |  |  |  |

| —                | —                       | —                        |  |  |  |  |  |

| Required I/O:    | 11                      | 19                       |  |  |  |  |  |

## Table 10.1. EMIF Pinout (C8051F960/3/6)

| Non Multiplexed Mode |                         |                          |  |  |  |  |  |

|----------------------|-------------------------|--------------------------|--|--|--|--|--|

| Signal Name          | Ро                      | rt Pin                   |  |  |  |  |  |

|                      | 8-Bit Mode <sup>1</sup> | 16-Bit Mode <sup>2</sup> |  |  |  |  |  |

| RD                   | P3.6                    | P3.6                     |  |  |  |  |  |

| WR                   | P3.7                    | P3.7                     |  |  |  |  |  |

| D0                   | P6.0                    | P6.0                     |  |  |  |  |  |

| D1                   | P6.1                    | P6.1                     |  |  |  |  |  |

| D2                   | P6.2                    | P6.2                     |  |  |  |  |  |

| D3                   | P6.3                    | P6.3                     |  |  |  |  |  |

| D4                   | P6.4                    | P6.4                     |  |  |  |  |  |

| D5                   | P6.5                    | P6.5                     |  |  |  |  |  |

| D6                   | P6.6                    | P6.6                     |  |  |  |  |  |

| D7                   | P6.7                    | P6.7                     |  |  |  |  |  |

| A0                   | P5.0                    | P5.0                     |  |  |  |  |  |

| A1                   | P5.1                    | P5.1                     |  |  |  |  |  |

| A2                   | P5.2                    | P5.2                     |  |  |  |  |  |

| A3                   | P5.3                    | P5.3                     |  |  |  |  |  |

| A4                   | P5.4                    | P5.4                     |  |  |  |  |  |

| A5                   | P5.5                    | P5.5                     |  |  |  |  |  |

| A6                   | P5.6                    | P5.6                     |  |  |  |  |  |

| A7                   | P5.7                    | P5.7                     |  |  |  |  |  |

| A8                   | —                       | P4.0                     |  |  |  |  |  |

| A9                   | —                       | P4.1                     |  |  |  |  |  |

| A10                  | —                       | P4.2                     |  |  |  |  |  |

| A11                  | —                       | P4.3                     |  |  |  |  |  |

| A12                  | —                       | P4.4                     |  |  |  |  |  |

| A13                  | —                       | P4.5                     |  |  |  |  |  |

| A14                  | —                       | P4.6                     |  |  |  |  |  |

| A15                  | —                       | P4.7                     |  |  |  |  |  |

| Required I/O:        | 18                      | 26                       |  |  |  |  |  |

#### Notes:

**1.** Using 8-bit movx instruction without bank select.

2. Using 16-bit movx instruction.

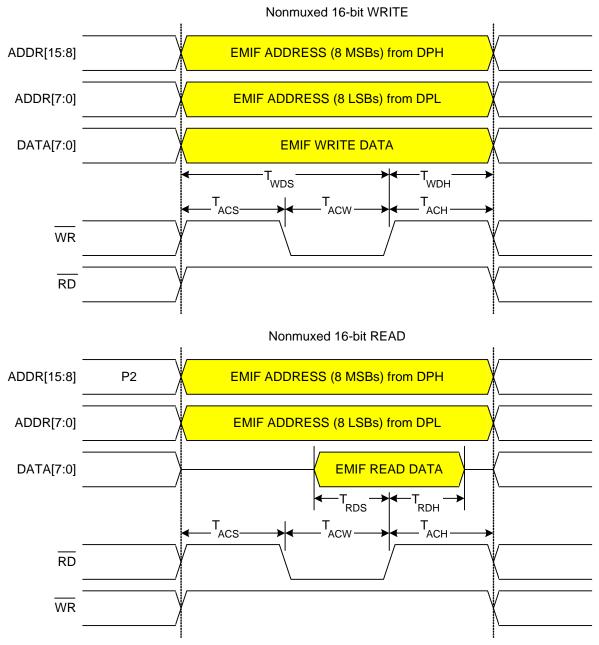

## 10.6.1. Non-Multiplexed Mode 10.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111

#### 14.6.3.1. CBC Encryption using SFRs

- First Configure AES Module for CBC Block Cipher Mode Encryption

- Reset AES module by writing 0x00 to AES0BCFG.

- Configure the AES Module data flow for XOR on input data by writing 0x01 to the AES0DCFG sfr.

- Write key size to bits 1 and 0 of the AES0BCFG.

- Configure the AES core for encryption by setting bit 2 of AES0BCFG.

- Enable the AES core by setting bit 3 of AES0BCFG.

- Repeat alternating write sequence 16 times

- Write plaintext byte to AES0BIN.

- Write initialization vector to AES0XIN

- Write encryption key byte to AES0KIN.

- Write remaining encryption key bytes to AES0KIN for 192-bit and 256-bit decryption only.

- Wait on AES done interrupt or poll bit 5 of AES0BCFG.

- Read 16 encrypted bytes from the AES0YOUT sfr.

If encrypting multiple blocks, this process may be repeated. It is not necessary reconfigure the AES module for each block. When using Cipher Block Chaining the initialization vector is written to the AES0XIN sfr for the first block only, as described. Additional blocks will chain the encrypted data from the previous block.

## 23.4. Special Function Registers for Selecting and Configuring the System Clock

The clocking sources on C8051F96x devices are enabled and configured using the OSCICN, OSCICL, OSCXCN and the SmaRTClock internal registers. See Section "24. SmaRTClock (Real Time Clock)" on page 300 for SmaRTClock register descriptions. The system clock source for the MCU can be selected using the CLKSEL register. To minimize active mode current, the oneshot timer which sets Flash read time should by bypassed when the system clock is greater than 10 MHz. See the FLSCL register description for details.

The clock selected as the system clock can be divided by 1, 2, 4, 8, 16, 32, 64, or 128. When switching between two clock divide values, the transition may take up to 128 cycles of the undivided clock source. The CLKRDY flag can be polled to determine when the new clock divide value has been applied. The clock divider must be set to "divide by 1" when entering Suspend or Sleep Mode.

The system clock source may also be switched on-the-fly. The switchover takes effect after one clock period of the slower oscillator.

| Bit   | 7      | 6           | 5 | 4 | 3   | 2 | 1           | 0 |

|-------|--------|-------------|---|---|-----|---|-------------|---|

| Name  | CLKRDY | CLKDIV[2:0] |   |   |     |   | CLKSEL[2:0] | ] |

| Туре  | R      | R/W         |   |   | R/W |   | R/W         |   |

| Reset | 0      | 0           | 0 | 1 | 0   | 0 | 1           | 0 |

#### SFR Definition 23.1. CLKSEL: Clock Select

#### SFR Page = 0x0 and 0xF; SFR Address = 0xA9

| Bit | Name        | Function                                                                                                                                                                            |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CLKRDY      | System Clock Divider Clock Ready Flag.                                                                                                                                              |

|     |             | <ul><li>0: The selected clock divide setting has not been applied to the system clock.</li><li>1: The selected clock divide setting has been applied to the system clock.</li></ul> |

| 6:4 | CLKDIV[2:0] | System Clock Divider Bits.                                                                                                                                                          |

|     |             | Selects the clock division to be applied to the undivided system clock source.<br>000: System clock is divided by 1.                                                                |

|     |             | 001: System clock is divided by 2.                                                                                                                                                  |

|     |             | 010: System clock is divided by 4.                                                                                                                                                  |

|     |             | 011: System clock is divided by 8.                                                                                                                                                  |

|     |             | 100: System clock is divided by 16.                                                                                                                                                 |

|     |             | 101: System clock is divided by 32.                                                                                                                                                 |

|     |             | 110: System clock is divided by 64.                                                                                                                                                 |

|     |             | 111: System clock is divided by 128.                                                                                                                                                |

| 3   | Unused      | Read = 0b. Must Write 0b.                                                                                                                                                           |

| 2:0 | CLKSEL[2:0] | System Clock Select.                                                                                                                                                                |

|     |             | Selects the oscillator to be used as the undivided system clock source.<br>000: Precision Internal Oscillator.<br>001: External Oscillator.                                         |

|     |             | 010: Low Power Oscillator divided by 8.                                                                                                                                             |

|     |             | 011: SmaRTClock Oscillator.                                                                                                                                                         |

|     |             | 100: Low Power Oscillator.                                                                                                                                                          |

|     |             | All other values reserved.                                                                                                                                                          |

## SFR Definition 27.20. P2MDIN: Port2 Input Mode

| Bit   | 7   | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|-------------|---|---|---|---|---|---|--|

| Name  |     | P2MDIN[6:0] |   |   |   |   |   |   |  |

| Туре  | R/W |             |   |   |   |   |   |   |  |

| Reset | 1   | 1           | 1 | 1 | 1 | 1 | 1 | 1 |  |

SFR Page = 0x0; SFR Address = 0xF3

| Bit | Name        | Function                                                                                                                                                                                                                                                                                              |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved    | Read = 1b; Must Write 1b.                                                                                                                                                                                                                                                                             |

| 6:0 | P2MDIN[3:0] | Analog Configuration Bits for P2.6–P2.0 (respectively).                                                                                                                                                                                                                                               |

|     |             | <ul> <li>Port pins configured for analog mode have their weak pullup and digital receiver disabled. The digital driver is not explicitly disabled.</li> <li>0: Corresponding P2.n pin is configured for analog mode.</li> <li>1: Corresponding P2.n pin is not configured for analog mode.</li> </ul> |

## SFR Definition 27.21. P2MDOUT: Port2 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|---|---|---|---|---|---|---|--|

| Name  | P2MDOUT[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = 0x0; SFR Address = 0xA6

| Bit | Name         | Function                                                                                             |

|-----|--------------|------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDOUT[7:0] | Output Configuration Bits for P2.7–P2.0 (respectively).                                              |

|     |              | These bits control the digital driver even when the corresponding bit in register P2MDIN is logic 0. |

|     |              | 0: Corresponding P2.n Output is open-drain.                                                          |

|     |              | 1: Corresponding P2.n Output is push-pull.                                                           |

| SMBCS1 | SMBCS0 | SMBus Clock Source         |  |  |  |

|--------|--------|----------------------------|--|--|--|

| 0      | 0      | Timer 0 Overflow           |  |  |  |

| 0      | 1      | Timer 1 Overflow           |  |  |  |

| 1      | 0      | Timer 2 High Byte Overflow |  |  |  |

| 1      | 1      | Timer 2 Low Byte Overflow  |  |  |  |

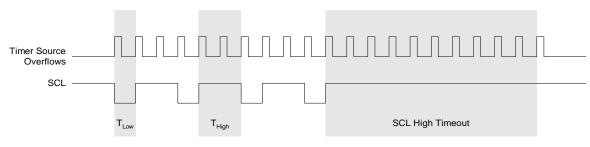

#### Table 28.1. SMBus Clock Source Selection

The SMBCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 28.1. The selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in Section "32. Timers" on page 448.

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

#### Equation 28.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 28.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 28.1.

$$BitRate = \frac{f_{ClockSourceOverflow}}{3}$$

Equation 28.2. Typical SMBus Bit Rate

Figure 28.4 shows the typical SCL generation described by Equation 28.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by Equation 28.2.

Figure 28.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 28.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| Table 28.5. SMBus Status Decoding With Hardware ACK Generation Disabled (EHACK = 0) |

|-------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------|

|                    | Values Read      |       |                                                                       |     |                                                 |                                                                                                |   | Values<br>Writ |     | tus<br>ected                   |

|--------------------|------------------|-------|-----------------------------------------------------------------------|-----|-------------------------------------------------|------------------------------------------------------------------------------------------------|---|----------------|-----|--------------------------------|

| Mode               | Status<br>Vector | ACKRQ | ARBLOST                                                               | ACK | Current SMbus State                             | Typical Response Options                                                                       |   | STO            | ACK | Next Status<br>Vector Expected |

|                    | 1110             | 0     | 0                                                                     | х   | A master START was gener-<br>ated.              | Load slave address + R/W into SMB0DAT.                                                         | 0 | 0              | х   | 1100                           |

|                    |                  | ~     | ~                                                                     | •   | A master data or address byte                   | Set STA to restart transfer.                                                                   | 1 | 0              | Х   | 1110                           |

| ter                |                  | 0     | 0                                                                     | 0   | was transmitted; NACK received.                 | Abort transfer.                                                                                | 0 | 1              | х   | -                              |

| unsmit             |                  |       |                                                                       |     |                                                 | Load next data byte into SMB0DAT.                                                              | 0 | 0              | х   | 1100                           |

| . Tra              | 1100             |       |                                                                       |     |                                                 | End transfer with STOP.                                                                        | 0 | 1              | Х   | -                              |

| Master Transmitter | 1100             | 0     | 0                                                                     | 1   | was transmitted; ACK received.                  | End transfer with STOP and start another transfer.                                             | 1 | 1              | х   | -                              |

|                    |                  |       |                                                                       |     |                                                 | Send repeated START.                                                                           | 1 | 0              | Х   | 1110                           |

|                    |                  |       |                                                                       |     |                                                 | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT).           | 0 | 0              | х   | 1000                           |

|                    |                  |       |                                                                       |     |                                                 | Acknowledge received byte;<br>Read SMB0DAT.                                                    | 0 | 0              | 1   | 1000                           |

|                    |                  |       |                                                                       |     |                                                 | Send NACK to indicate last byte, and send STOP.                                                | 0 | 1              | 0   | -                              |

| 'er                |                  |       | Send NACK to indicate last byt<br>and send STOP followed by<br>START. | -   | 1                                               | 1                                                                                              | 0 | 1110           |     |                                |

| Recei              | 1000             | 1     | 0                                                                     | х   | A master data byte was received; ACK requested. | Send ACK followed by repeated START.                                                           | 1 | 0              | 1   | 1110                           |

| Master Receiver    |                  |       |                                                                       |     | neceived, ACR requested.                        | Send NACK to indicate last byte, and send repeated START.                                      | 1 | 0              | 0   | 1110                           |

|                    |                  |       |                                                                       |     |                                                 | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI).    | 0 | 0              | 1   | 1100                           |

|                    |                  |       |                                                                       |     |                                                 | Send NACK and switch to Mas-<br>ter Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0 | 0              | 0   | 1100                           |

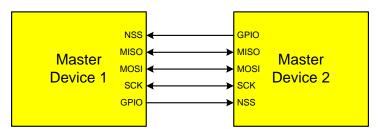

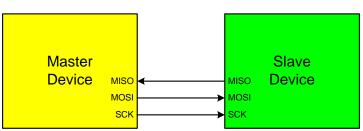

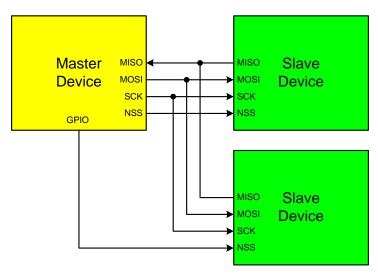

Figure 30.2. Multiple-Master Mode Connection Diagram

Figure 30.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

## 30.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data,

| Parameter                | Description                                                  | Min                          | Max                     | Units |

|--------------------------|--------------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mode              | Timing (See Figure 30.8 and Figure 30.9)                     | 1                            |                         |       |

| Т <sub>МСКН</sub>        | SCK High Time                                                | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub>        | SCK Low Time                                                 | 1 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>MIS</sub>         | MISO Valid to SCK Shift Edge                                 | 1 x T <sub>SYSCLK</sub> + 20 | _                       | ns    |

| Т <sub>МІН</sub>         | SCK Shift Edge to MISO Change                                | 0                            |                         | ns    |

| Slave Mode               | <b>Fiming</b> (See Figure 30.10 and Figure 30.11)            |                              |                         |       |

| T <sub>SE</sub>          | NSS Falling to First SCK Edge                                | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SD</sub>          | Last SCK Edge to NSS Rising                                  | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SEZ</sub>         | NSS Falling to MISO Valid                                    | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>         | NSS Rising to MISO High-Z                                    | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| Т <sub>СКН</sub>         | SCK High Time                                                | 5 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>CKL</sub>         | SCK Low Time                                                 | 5 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SIS</sub>         | MOSI Valid to SCK Sample Edge                                | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SIH</sub>         | SCK Sample Edge to MOSI Change                               | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| Т <sub>SOH</sub>         | SCK Shift Edge to MISO Change                                | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>         | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)             | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| Note: T <sub>SYSCL</sub> | $_{C}$ is equal to one period of the device system clock (S) | /SCLK).                      | 1                       | 1     |

Table 30.1. SPI Slave Timing Parameters

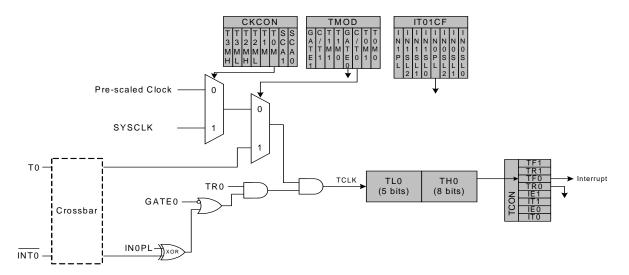

Figure 32.1. T0 Mode 0 Block Diagram

#### 32.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

#### 32.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "17.6. External Interrupts INT0 and INT1" on page 247 for details on the external input signals INT0 and INT1).

# SFR Definition 32.2. TCON: Timer Control

| Bit   | 7              | 6                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                              | 4               | 3                                              | 2           | 1   | 0   |  |  |

|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------|-------------|-----|-----|--|--|

| Nam   | e TF1          | TR1                                                                                                                                                                                                                                                                 | TF0                                                                                                                                                                                                            | TR0             | IE1                                            | IT1         | IE0 | IT0 |  |  |

| Туре  | R/W            | R/W                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                            | R/W             | R/W                                            | R/W         | R/W | R/W |  |  |

| Rese  | t 0            | 0                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                              | 0               | 0                                              | 0           | 0   | 0   |  |  |

| SFR F | Page = All Pag | es; SFR Address = 0x88; Bit-Addressable                                                                                                                                                                                                                             |                                                                                                                                                                                                                |                 |                                                |             |     |     |  |  |

| Bit   | Name Function  |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                |                 |                                                |             |     |     |  |  |

| 7     | TF1            | Set to 1 by I                                                                                                                                                                                                                                                       | <b>Timer 1 Overflow Flag.</b><br>Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine. |                 |                                                |             |     |     |  |  |

| 6     | TR1            | Timer 1 Ru                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                |                 |                                                |             |     |     |  |  |

|       |                |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                | etting this bit | to 1.                                          |             |     |     |  |  |

| 5     | TF0            | Set to 1 by I                                                                                                                                                                                                                                                       | <b>Timer 0 Overflow Flag.</b><br>Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine. |                 |                                                |             |     |     |  |  |

| 4     | TR0            | Timer 0 Ru                                                                                                                                                                                                                                                          | n Control.                                                                                                                                                                                                     |                 |                                                |             |     |     |  |  |

|       |                | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                        |                                                                                                                                                                                                                |                 |                                                |             |     |     |  |  |

| 3     | IE1            | External In                                                                                                                                                                                                                                                         | terrupt 1.                                                                                                                                                                                                     |                 |                                                |             |     |     |  |  |

|       |                | can be clea                                                                                                                                                                                                                                                         | red by softw                                                                                                                                                                                                   | are but is au   | n edge/level<br>tomatically c<br>n edge-trigge | leared when |     |     |  |  |

| 2     | IT1            | Interrupt 1                                                                                                                                                                                                                                                         | Type Select                                                                                                                                                                                                    | t.              |                                                |             |     |     |  |  |

|       |                | This bit selects whether the configured INT1 interrupt will be edge or level sensitive.<br>INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see<br>SFR Definition 17.7).<br>0: INT1 is level triggered.<br>1: INT1 is edge triggered. |                                                                                                                                                                                                                |                 |                                                |             |     |     |  |  |

| 1     | IE0            | External In                                                                                                                                                                                                                                                         | terrupt 0.                                                                                                                                                                                                     |                 |                                                |             |     |     |  |  |

|       |                | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                             |                                                                                                                                                                                                                |                 |                                                |             |     |     |  |  |

| 0     | IT0            | Interrupt 0                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |                 |                                                |             |     |     |  |  |

|       |                | This bit selects whether the configured INT0 interrupt will be edge or level sensitive.<br>INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFR Definition 17.7).<br>0: INT0 is level triggered.<br>1: INT0 is edge triggered.        |                                                                                                                                                                                                                |                 |                                                |             |     |     |  |  |

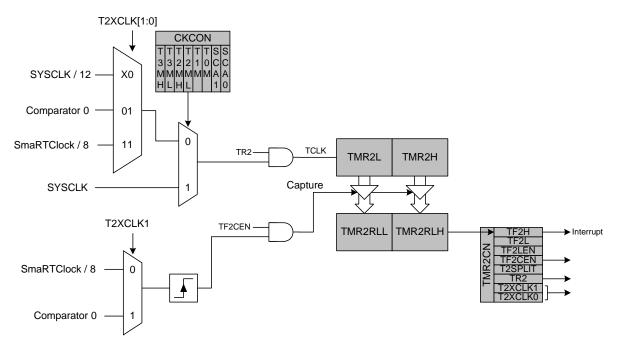

# C8051F96x

When Capture Mode is enabled, a capture event will be generated either every Comparator 0 rising edge or every 8 SmaRTClock clock cycles, depending on the T2XCLK1 setting. When the capture event occurs, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set (triggering an interrupt if Timer 2 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 or SmaRT-Clock period can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading.

For example, if T2ML = 1b, T2XCLK1 = 0b, and TF2CEN = 1b, Timer 2 will clock every SYSCLK and capture every SmaRTClock clock divided by 8. If the SYSCLK is 24.5 MHz and the difference between two successive captures is 5984, then the SmaRTClock clock is as follows:

24.5 MHz/(5984/8) = 0.032754 MHz or 32.754 kHz.

This mode allows software to determine the exact SmaRTClock frequency in self-oscillate mode and the time between consecutive Comparator 0 rising edges, which is useful for detecting changes in the capacitance of a Touch Sense Switch.

Figure 32.6. Timer 2 Capture Mode Block Diagram

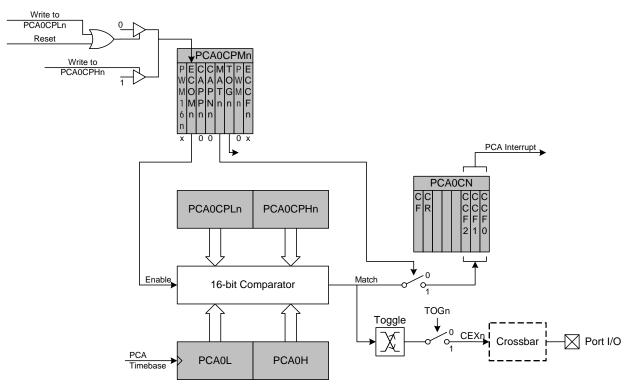

Figure 33.6. PCA High-Speed Output Mode Diagram

#### 33.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 33.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 33.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. The MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

# **CONTACT INFORMATION**

#### Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.