# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                         |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 57                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 8.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                      |

| Data Converters            | A/D 16x10b/12b                                                   |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 76-VFQFN Dual Rows, Exposed Pad                                  |

| Supplier Device Package    | 76-DQFN (6x6)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f966-a-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 5.10. External Voltage Reference                     | . 101 |

|------------------------------------------------------|-------|

| 5.11. Internal Voltage Reference                     |       |

| 5.12. Analog Ground Reference                        |       |

| 5.13. Temperature Sensor Enable                      |       |

| 5.14. Voltage Reference Electrical Specifications    |       |

| 6. Programmable Current Reference (IREF0)            |       |

| 6.1. PWM Enhanced Mode                               |       |

| 6.2. IREF0 Specifications                            |       |

| 7. Comparators                                       |       |

| 7.1. Comparator Inputs                               |       |

| 7.2. Comparator Outputs                              |       |

| 7.3. Comparator Response Time                        |       |

| 7.4. Comparator Hysterisis                           |       |

| 7.5. Comparator Register Descriptions                |       |

| 7.6. Comparator0 and Comparator1 Analog Multiplexers |       |

| 8. CIP-51 Microcontroller                            |       |

| 8.1. Instruction Set                                 |       |

| 8.1.1. Instruction and CPU Timing                    | . 116 |

| 8.2. CIP-51 Register Descriptions                    |       |

| 9. Memory Organization                               |       |

| 9.1. Program Memory                                  |       |

| 9.1.1. MOVX Instruction and Program Memory           | . 127 |

| 9.2. Data Memory                                     | . 127 |

| 9.2.1. Internal RAM                                  | . 128 |

| 9.2.2. External RAM                                  | . 128 |

| 10. External Data Memory Interface and On-Chip XRAM  | . 129 |

| 10.1. Accessing XRAM                                 | . 129 |

| 10.1.1. 16-Bit MOVX Example                          | . 129 |

| 10.1.2. 8-Bit MOVX Example                           | . 129 |

| 10.2. Configuring the External Memory Interface      | . 130 |

| 10.3. Port Configuration                             |       |

| 10.4. Multiplexed and Non-multiplexed Selection      |       |

| 10.4.1. Multiplexed Configuration                    | . 134 |

| 10.4.2. Non-multiplexed Configuration                | . 134 |

| 10.5. Memory Mode Selection                          |       |

| 10.5.1. Internal XRAM Only                           | . 136 |

| 10.5.2. Split Mode without Bank Select               |       |

| 10.5.3. Split Mode with Bank Select                  |       |

| 10.5.4. External Only                                |       |

| 10.6. Timing                                         |       |

| 10.6.1. Non-Multiplexed Mode                         |       |

| 10.6.2. Multiplexed Mode                             |       |

| 11. Direct Memory Access (DMA0)                      |       |

| 11.1. DMA0 Architecture                              |       |

| 11.2. DMA0 Arbitration                               | . 148 |

# 1.5. SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

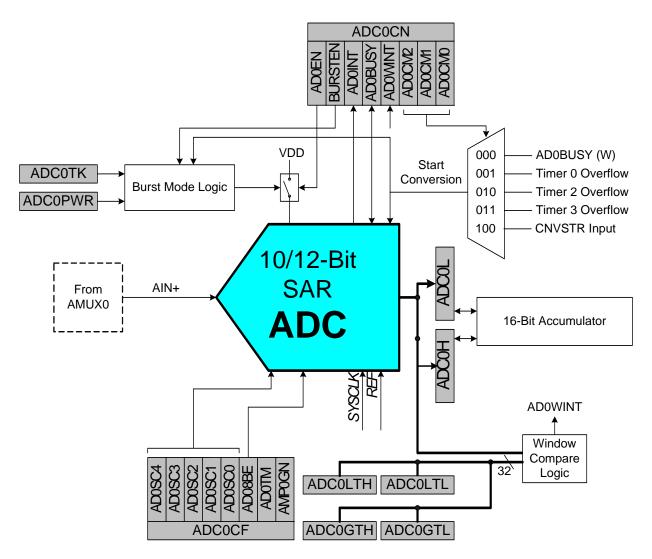

The ADC0 on C8051F96x devices is a 300 ksps, 10-bit or 75 ksps, 12-bit successive-approximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results. See Section "5.4. 12-Bit Mode" on page 84 for more details on using the ADC in 12-bit mode.

The ADC is fully configurable under software control via Special Function Registers. The ADC0 operates in single-ended mode and may be configured to measure various different signals using the analog multiplexer described in Section "5.7. ADC0 Analog Multiplexer" on page 95. The voltage reference for the ADC is selected as described in Section "5.9. Voltage and Ground Reference Options" on page 100.

Figure 1.13. ADC0 Functional Block Diagram

# Table 4.15. IREF0 Electrical Characteristics

$V_{BAT}$  = 1.8 to 3.8 V, –40 to +85 °C, unless otherwise specified.

| Parameter                                                                                           | Conditions                                                                                                                                                                                                | Min                  | Тур                                 | Max                                                    | Units                      |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------|--------------------------------------------------------|----------------------------|

| Static Performance                                                                                  |                                                                                                                                                                                                           |                      |                                     |                                                        |                            |

| Resolution                                                                                          |                                                                                                                                                                                                           |                      | 6                                   |                                                        |                            |

| Output Compliance Range                                                                             | Low Power Mode, Source<br>High Current Mode, Source<br>Low Power Mode, Sink<br>High Current Mode, Sink                                                                                                    | 0<br>0<br>0.3<br>0.8 |                                     | $V_{BAT} - 0.4 \\ V_{BAT} - 0.8 \\ V_{BAT} \\ V_{BAT}$ | V                          |

| Integral Nonlinearity                                                                               |                                                                                                                                                                                                           | —                    | <±0.2                               | ±1.0                                                   | LSB                        |

| Differential Nonlinearity                                                                           |                                                                                                                                                                                                           | —                    | <±0.2                               | ±1.0                                                   | LSB                        |

| Offset Error                                                                                        |                                                                                                                                                                                                           | —                    | <±0.1                               | ±0.5                                                   | LSB                        |

|                                                                                                     | Low Power Mode, Source                                                                                                                                                                                    | —                    | —                                   | ±5                                                     | %                          |

| Full Scale Error                                                                                    | High Current Mode, Source                                                                                                                                                                                 |                      | —                                   | ±6                                                     | %                          |

|                                                                                                     | Low Power Mode, Sink                                                                                                                                                                                      | —                    | —                                   | ±8                                                     | %                          |

|                                                                                                     | High Current Mode, Sink                                                                                                                                                                                   | —                    | —                                   | ±8                                                     | %                          |

| Absolute Current Error                                                                              | Low Power Mode<br>Sourcing 20 µA                                                                                                                                                                          | _                    | <±1                                 | ±3                                                     | %                          |

| Dynamic Performance                                                                                 |                                                                                                                                                                                                           |                      |                                     |                                                        |                            |

| Output Settling Time to 1/2 LSB                                                                     |                                                                                                                                                                                                           | —                    | 300                                 | —                                                      | ns                         |

| Startup Time                                                                                        |                                                                                                                                                                                                           |                      | 1                                   | —                                                      | μs                         |

| Power Consumption                                                                                   |                                                                                                                                                                                                           |                      |                                     |                                                        |                            |

| Net Power Supply Current<br>(V <sub>BAT</sub> supplied to IREF0 minus<br>any output source current) | Low Power Mode, Source<br>IREF0DAT = 000001<br>IREF0DAT = 111111<br>High Current Mode, Source<br>IREF0DAT = 000001<br>IREF0DAT = 111111<br>Low Power Mode, Sink<br>IREF0DAT = 000001<br>IREF0DAT = 111111 |                      | 10<br>10<br>10<br>10<br>1<br>1<br>1 |                                                        | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |

| Note: Refer to "6.1. PWM Enhance                                                                    | High Current Mode, Sink<br>IREF0DAT = 000001<br>IREF0DAT = 111111                                                                                                                                         |                      | 12<br>81                            | IREE0 resoluti                                         | μA<br>μA                   |

### 5.2. Modes of Operation

ADC0 has a maximum conversion speed of 300 ksps in 10-bit mode. The ADC0 conversion clock (SAR-CLK) is a divided version of the system clock when burst mode is disabled (BURSTEN = 0), or a divided version of the low power oscillator when burst mode is enabled (BURSEN = 1). The clock divide value is determined by the AD0SC bits in the ADC0CF register.

### 5.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 3 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. When Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See "32. Timers" on page 448 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to 1 Bit 6 in register P0SKIP. See "27. Port Input/Output" on page 356 for details on Port I/O configuration.

#### 5.2.2. Tracking Modes

Each ADC0 conversion must be preceded by a minimum tracking time in order for the converted result to be accurate. The minimum tracking time is given in Table 4.12. The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state when Burst Mode is disabled, the ADC0 input is continuously tracked, except when a conversion is in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a tracking period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR signal is used to initiate conversions in low-power tracking mode, ADC0 tracks only when CNVSTR is low; conversion begins on the rising edge of CNVSTR (see Figure 5.2). Tracking can also be disabled (shutdown) when the device is in low power standby or sleep modes. Low-power track-and-hold mode is also useful when AMUX settings are frequently changed, due to the settling time requirements described in "5.2.4. Settling Time Requirements" on page 83.

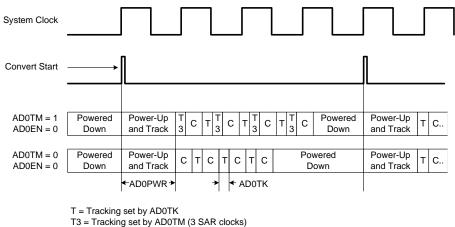

### 5.2.3. Burst Mode

Burst Mode is a power saving feature that allows ADC0 to remain in a low power state between conversions. When Burst Mode is enabled, ADC0 wakes from a low power state, accumulates 1, 4, 8, 16, 32, or 64 using an internal Burst Mode clock (approximately 20 MHz), then re-enters a low power state. Since the Burst Mode clock is independent of the system clock, ADC0 can perform multiple conversions then enter a low power state within a single system clock cycle, even if the system clock is slow (e.g. 32.768 kHz), or suspended.

Burst Mode is enabled by setting BURSTEN to logic 1. When in Burst Mode, AD0EN controls the ADC0 idle power state (i.e. the state ADC0 enters when not tracking or performing conversions). If AD0EN is set to logic 0, ADC0 is powered down after each burst. If AD0EN is set to logic 1, ADC0 remains enabled after each burst. On each convert start signal, ADC0 is awakened from its Idle Power State. If AD0C0 is powered down, it will automatically power up and wait the programmable Power-Up Time controlled by the AD0PWR bits. Otherwise, ADC0 will start tracking and converting immediately. Figure 5.3 shows an example of Burst Mode Operation with a slow system clock and a repeat count of 4.

When Burst Mode is enabled, a single convert start will initiate a number of conversions equal to the repeat count. When Burst Mode is disabled, a convert start is required to initiate each conversion. In both modes, the ADC0 End of Conversion Interrupt Flag (AD0INT) will be set after "repeat count" conversions have been accumulated. Similarly, the Window Comparator will not compare the result to the greater-than and less-than registers until "repeat count" conversions have been accumulated.

In Burst Mode, tracking is determined by the settings in AD0PWR and AD0TK. The default settings for these registers will work in most applications without modification; however, settling time requirements may need adjustment in some applications. Refer to "5.2.4. Settling Time Requirements" on page 83 for more details.

Notes:

- Setting AD0TM to 1 will insert an additional 3 SAR clocks of tracking before each conversion, regardless of the settings of AD0PWR and AD0TK.

- When using Burst Mode, care must be taken to issue a convert start signal no faster than once every four SYSCLK periods. This includes external convert start signals.

# SFR Definition 5.6. ADC0H: ADC0 Data Word High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | ADC0[15:8] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Page = 0x0; SFR Address = 0xBE

| Bit   | Name                                                                                                                                                              | Description                  | Read                                                                                                               | Write                                                                                       |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0   | ADC0[15:8]                                                                                                                                                        | ADC0 Data Word High<br>Byte. | Most Significant Byte of the<br>16-bit ADC0 Accumulator<br>formatted according to the<br>settings in AD0SJST[2:0]. | Set the most significant<br>byte of the 16-bit ADC0<br>Accumulator to the value<br>written. |  |  |  |  |

| Note: | If Accumulator shifting is enabled, the most significant bits of the value read will be zeros. This register should not be written when the SYNC bit is set to 1. |                              |                                                                                                                    |                                                                                             |  |  |  |  |

### SFR Definition 5.7. ADC0L: ADC0 Data Word Low Byte

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------|---|---|---|---|---|---|---|--|

| Name  | ADC0[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W       |   |   |   |   |   |   |   |  |

| Reset | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = 0x0; SFR Address = 0xBD;

| Bit   | Name                                                                                                                                                                                                                                    | Description                 | Read                                                                                                                | Write                                                                                        |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | ADC0[7:0]                                                                                                                                                                                                                               | ADC0 Data Word Low<br>Byte. | Least Significant Byte of the<br>16-bit ADC0 Accumulator<br>formatted according to the<br>settings in AD0SJST[2:0]. | Set the least significant<br>byte of the 16-bit ADC0<br>Accumulator to the value<br>written. |  |  |  |  |  |

| Note: | <ul> <li>If Accumulator shifting is enabled, the most significant bits of the value read will be the least significant bits of the accumulator high byte. This register should not be written when the SYNC bit is set to 1.</li> </ul> |                             |                                                                                                                     |                                                                                              |  |  |  |  |  |

### 5.6. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

# SFR Definition 8.3. SP: Stack Pointer

| Bit   | 7                  | 6           | 5            | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------------|-------------|--------------|---|---|---|---|---|--|--|

| Name  | SP[7:0]            |             |              |   |   |   |   |   |  |  |

| Туре  | R/W                |             |              |   |   |   |   |   |  |  |

| Reset | et 0 0 0 0 0 1 1 1 |             |              |   |   |   |   |   |  |  |

|       | ge = All Pag       | es; SFR Add | lress = 0x81 |   |   |   |   |   |  |  |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

# SFR Definition 8.4. ACC: Accumulator

| Name ACC[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ACC[7:0] |  |  |  |  |  |  |  |  |

| Type R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W      |  |  |  |  |  |  |  |  |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 |          |  |  |  |  |  |  |  |  |

SFR Page = All Pages; SFR Address = 0xE0; Bit-Addressable

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

# SFR Definition 8.5. B: B Register

| Bit   | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------|---|---|---|---|---|---|---|--|

| Name  | B[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W    |   |   |   |   |   |   |   |  |

| Reset | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = All Pages; SFR Address = 0xF0; Bit-Addressable

| ſ | Bit | Name   | Function                                                                        |

|---|-----|--------|---------------------------------------------------------------------------------|

| Ī | 7:0 | B[7:0] | B Register.                                                                     |

|   |     |        | This register serves as a second accumulator for certain arithmetic operations. |

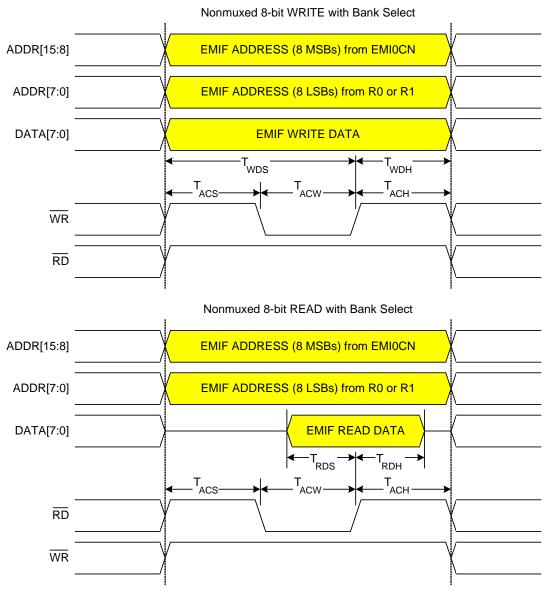

### 10.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110

Figure 10.6. Non-multiplexed 8-bit MOVX with Bank Select Timing

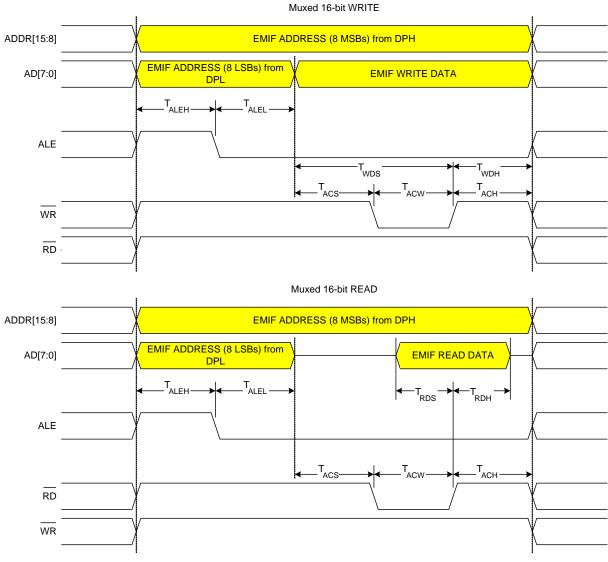

# 10.6.2. Multiplexed Mode 10.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011

Figure 10.7. Multiplexed 16-bit MOVX Timing

# SFR Definition 13.5. CRC1OUTL: CRC1 Output LSB

| Bit   | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------------|---|---|---|---|---|---|---|--|

| Name  | CRC1OUTL[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R             | R | R | R | R | R | R | R |  |

| Reset | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| Bit | Name          | Function        |

|-----|---------------|-----------------|

| 7:0 | CRC1OUTL[7:0] | CRC1 Output LSB |

# SFR Definition 13.6. CRC1OUTH: CRC1 Output MSB

| Bit   | 7              | 6             | 5                | 4            | 3    | 2 | 1 | 0 |  |  |

|-------|----------------|---------------|------------------|--------------|------|---|---|---|--|--|

| Nam   | e              | CRC1OUTH[7:0] |                  |              |      |   |   |   |  |  |

| Туре  | e R            | R             | R                | R            | R    | R | R | R |  |  |

| Rese  | et 0           | 0             | 0                | 0            | 0    | 0 | 0 | 0 |  |  |

| SFR F | Page = 0x2; SF | R Address :   | = 0xBB; Not      | Bit-Addressa | able |   |   |   |  |  |

| Bit   | Name           |               | Function         |              |      |   |   |   |  |  |

| 7:0   | CRC1OUTH[7     | 7:0] CRC1     | CRC1 Output MSB. |              |      |   |   |   |  |  |

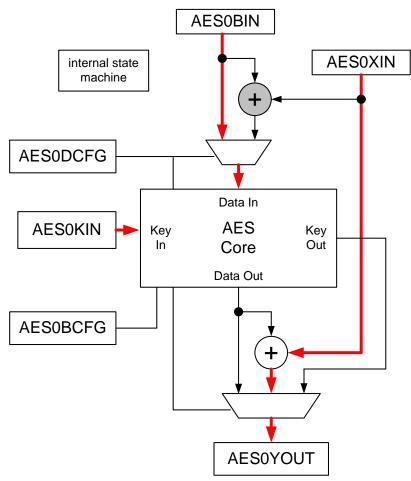

### 14.4.2. AES Block Cipher Encryption using SFRs

- First Configure AES Module for AES Block Cipher

- Reset AES module by writing 0x00 to AES0BCFG.

- Configure the AES Module data flow for AES Block Cipher by writing 0x00 to the AES0DCFG sfr.

- Write key size to bits 1 and 0 of the AES0BCFG.

- Configure the AES core for encryption by setting bit 2 of AES0BCFG.

- Enable the AES core by setting bit 3 of AES0BCFG.

- Repeat alternating write sequence 16 times

- Write plaintext byte to AES0BIN.

- Write encryption key byte to AES0KIN.

- Write remaining encryption key bytes to AES0KIN for 192-bit and 256-bit encryption only.

- Wait on AES done interrupt or poll bit 5 of AES0BCFG.

- Read 16 encrypted bytes from the AES0YOUT sfr.

If encrypting multiple blocks, this process may be repeated. It is not necessary reconfigure the AES module for each block.

### 14.6.4. CBC Decryption

The AES0 module data flow for CBC encryption is shown in Figure 14.6. The ciphertext is written to the AES0BIN sfr. For the first block, the initialization vector is written to the AES0XIN sfr. For subsequent blocks, the previous block ciphertext is written to the AES0XIN sfr. The AES0DCF sfr is configured to XOR AES0XIN with AES0BIN for the AES core data input. The XOR on the output is not used. The AES core is configured for an encryption operation. The encryption key is written to AES0KIN. The key size is set to the desired key size.

Figure 14.6. CBC Decryption Data Flow

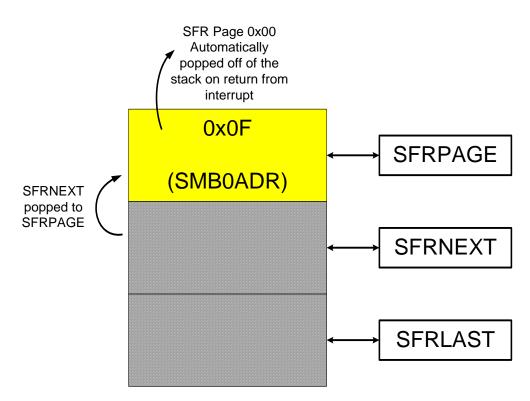

Figure 16.6. SFR Page Stack Upon Return From SPI0 Interrupt

In the example above, all three bytes in the SFR Page Stack are accessible via the SFRPAGE, SFRNEXT, and SFRLAST special function registers. If the stack is altered while servicing an interrupt, it is possible to return to a different SFR Page upon interrupt exit than selected prior to the interrupt call. Direct access to the SFR Page stack can be useful to enable real-time operating systems to control and manage context switching between multiple tasks.

Push operations on the SFR Page Stack only occur on interrupt service, and pop operations only occur on interrupt exit (execution on the RETI instruction). The automatic switching of the SFRPAGE and operation of the SFR Page Stack as described above can be disabled in software by clearing the SFR Automatic Page Enable Bit (SFRPGEN) in the SFR Page Control Register (SFR0CN). See SFR Definition 16.1.

### 22.2. Power-Fail Reset

C8051F96x devices have two Active Mode Supply Monitors that can hold the system in reset if the supply voltage drops below  $V_{RST}$ . The first of the two identical supply monitors is connected to the output of the supply select switch (which chooses the VBAT or VDC pin as the source of the digital supply voltage) and is enabled and selected as a reset source after each power-on or power-fail reset. This supply monitor will be referred to as the digital supply monitor. The second supply monitor is connected directly to the VBAT pin an is disabled after each power-on or power-fail reset. This supply monitor will be referred to as the analog supply monitor. The analog supply monitor should be enabled any time the supply select switch is set to the VDC pin to ensure that the VBAT supply does not drop below  $V_{RST}$ .

When enabled and selected as a reset source, any power down transition or power irregularity that causes the monitored supply voltage to drop below  $V_{RST}$  will cause the RST pin to be driven low and the CIP-51 will be held in a reset state (see Figure 22.2). When the supply voltage returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state.

After a power-fail reset, the PORSF flag reads 1, the contents of RAM invalid, and the digital supply monitor is enabled and selected as a reset source. The enable state of either supply monitor and its selection as a reset source is only altered by power-on and power-fail resets. For example, if the supply monitor is deselected as a reset source and disabled by software, then a software reset is performed, the supply monitor will remain disabled and de-selected after the reset.

In battery-operated systems, the contents of RAM can be preserved near the end of the battery's usable life if the device is placed in Sleep Mode prior to a power-fail reset occurring. When the device is in Sleep Mode, the power-fail reset is automatically disabled, both active mode supply monitors are turned off, and the contents of RAM are preserved as long as the supply does not fall below  $V_{POR}$ . A large capacitor can be used to hold the power supply voltage above  $V_{POR}$  while the user is replacing the battery. Upon waking from Sleep mode, the enable and reset source select state of the  $V_{DD}$  supply monitor are restored to the value last set by the user.

To allow software early notification that a power failure is about to occur, the VDDOK bit is cleared when the supply falls below the  $V_{WARN}$  threshold. The VDDOK bit can be configured to generate an interrupt. Each of the active mode supply montiors have their independent VDDOK and  $V_{WARN}$  flags. See Section "17. Interrupt Handler" on page 237 for more details.

**Important Note:** To protect the integrity of Flash contents, **the active mode supply monitor(s) must be enabled and selected as a reset source if software contains routines which erase or write Flash memory.** If the digital supply monitor is not enabled, any erase or write performed on Flash memory will cause a Flash Error device reset.

### 27.2.2. Assigning Port I/O Pins to Digital Functions

Any Port pins not assigned to analog functions may be assigned to digital functions or used as GPIO. Most digital functions rely on the Crossbar for pin assignment; however, some digital functions bypass the Crossbar in a manner similar to the analog functions listed above. **Port pins used by these digital func-tions and any Port pins selected for use as GPIO should have their corresponding bit in PnSKIP set to 1.** Table 27.2 shows all available digital functions and the potential mapping of Port I/O to each digital function.

| Digital Function                                                                                                           | Potentially Assignable Port Pins                                                                                                                                                                                           | SFR(s) used for<br>Assignment |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| UART0, SPI0, SPI1, SMBus,<br>CP0 and CP1 Outputs, Sys-<br>tem Clock Output, PCA0,<br>Timer0 and Timer1 External<br>Inputs. | Any Port pin available for assignment by the<br>Crossbar. This includes P0.0–P2.7 pins which<br>have their PnSKIP bit set to 0.<br><b>Note:</b> The Crossbar will always assign UART0 and<br>SPI1 pins to fixed locations. | XBR0, XBR1, XBR2              |

| Any pin used for GPIO                                                                                                      | P0.0–P7.0                                                                                                                                                                                                                  | P0SKIP, P1SKIP,<br>P2SKIP     |

| External Memory Interface                                                                                                  | P3.6–P6.7                                                                                                                                                                                                                  | EMI0CF                        |

### Table 27.2. Port I/O Assignment for Digital Functions

### 27.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions

External digital event capture functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The digital event capture functions do not require dedicated pins and will function on both GPIO pins (PnSKIP = 1) and pins in use by the Crossbar (PnSKIP = 0). External digital even capture functions cannot be used on pins configured for analog I/O. Table 27.3 shows all available external digital event capture functions.

| Digital Function     | Potentially Assignable Port Pins | SFR(s) used for<br>Assignment  |

|----------------------|----------------------------------|--------------------------------|

| External Interrupt 0 | P0.0–P0.5, P1.6, P1.7            | IT01CF                         |

| External Interrupt 1 | P0.0–P0.4, P1.6, P1.7            | IT01CF                         |

| Port Match           | P0.0–P1.7                        | POMASK, POMAT<br>P1MASK, P1MAT |

# SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7     | 6    | 5     | 4    | 3      | 2     | 1     | 0     |

|-------|-------|------|-------|------|--------|-------|-------|-------|

| Name  | CP1AE | CP1E | CP0AE | CP0E | SYSCKE | SMB0E | SPI0E | URT0E |

| Туре  | R/W   | R/W  | R/W   | R/W  | R/W    | R/W   | R/W   | R/W   |

| Reset | 0     | 0    | 0     | 0    | 0      | 0     | 0     | 0     |

# SFR Page = 0x0 and 0xF; SFR Address = 0xE1

| Bit     | Name          | Function                                                                     |

|---------|---------------|------------------------------------------------------------------------------|

| 7       | CP1AE         | Comparator1 Asynchronous Output Enable.                                      |

|         |               | 0: Asynchronous CP1 output unavailable at Port pin.                          |

|         |               | 1: Asynchronous CP1 output routed to Port pin.                               |

| 6       | CP1E          | Comparator1 Output Enable.                                                   |

|         |               | 0: CP1 output unavailable at Port pin.                                       |

|         |               | 1: CP1 output routed to Port pin.                                            |

| 5       | CP0AE         | Comparator0 Asynchronous Output Enable.                                      |

|         |               | 0: Asynchronous CP0 output unavailable at Port pin.                          |

|         |               | 1: Asynchronous CP0 output routed to Port pin.                               |

| 4       | CP0E          | Comparator0 Output Enable.                                                   |

|         |               | 0: CP1 output unavailable at Port pin.                                       |

|         |               | 1: CP1 output routed to Port pin.                                            |

| 3       | SYSCKE        | SYSCLK Output Enable.                                                        |

|         |               | 0: SYSCLK output unavailable at Port pin.                                    |

|         |               | 1: SYSCLK output routed to Port pin.                                         |

| 2       | SMB0E         | SMBus I/O Enable.                                                            |

|         |               | 0: SMBus I/O unavailable at Port pin.                                        |

|         |               | 1: SDA and SCL routed to Port pins.                                          |

| 1       | SPI0E         | SPI0 I/O Enable                                                              |

|         |               | 0: SPI0 I/O unavailable at Port pin.                                         |

|         |               | 1: SCK, MISO, and MOSI (for SPI0) routed to Port pins.                       |

|         |               | NSS (for SPI0) routed to Port pin only if SPI0 is configured to 4-wire mode. |

| 0       | URT0E         | UART0 Output Enable.                                                         |

|         |               | 0: UART I/O unavailable at Port pin.                                         |

|         |               | 1: TX0 and RX0 routed to Port pins P0.4 and P0.5.                            |

| Note: S | SPI0 can be a | ssigned either 3 or 4 Port I/O pins.                                         |

# SFR Definition 27.16. P1MDOUT: Port1 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|---|---|---|---|---|---|---|--|

| Name  | P1MDOUT[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = 0x0; SFR Address = 0xA5

| Bit | Name         | Function                                                                                                                                                                                                                          |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                           |

|     |              | <ul> <li>These bits control the digital driver even when the corresponding bit in register P1MDIN is logic 0.</li> <li>0: Corresponding P1.n Output is open-drain.</li> <li>1: Corresponding P1.n Output is push-pull.</li> </ul> |

# SFR Definition 27.17. P1DRV: Port1 Drive Strength

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------------|---|---|---|---|---|---|---|--|

| Name  | P1DRV[7:0]      |   |   |   |   |   |   |   |  |

| Туре  | R/W             |   |   |   |   |   |   |   |  |

| Reset | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |  |

SFR Page = 0xF; SFR Address = 0xA5

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |

# SFR Definition 27.40. P7MDOUT: Port7 Output Mode

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| Name  |   |   |   |   |   |   |   | P7MDOUT |

| Туре  |   |   |   |   |   |   |   | R/W     |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0       |

SFR Page = 0xF; SFR Address = 0xFC

| Bit | Name      | Function                               |  |  |  |  |  |

|-----|-----------|----------------------------------------|--|--|--|--|--|

| 7:1 | Unused    | Read = 0000000b; Write = Don't Care.   |  |  |  |  |  |

| 0   | P7MDOUT.0 | Output Configuration Bits for P7.0.    |  |  |  |  |  |

|     |           | These bits control the digital driver. |  |  |  |  |  |

|     |           | 0: P7.0 Output is open-drain.          |  |  |  |  |  |

|     |           | 1: P7.0 Output is push-pull.           |  |  |  |  |  |

# SFR Definition 27.41. P7DRV: Port7 Drive Strength

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|-------|---|---|---|---|---|---|---|-------|

| Name  |   |   |   |   |   |   |   | P7DRV |

| Туре  |   |   |   |   |   |   |   | R/W   |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

SFR Page = 0xF; SFR Address = 0xAB

| Bit | Name    | Function                                                                                                                                                                                                                                                        |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | Unused  | Read = 0000000b; Write = Don't Care.                                                                                                                                                                                                                            |

| 0   | P7DRV.0 | <ul> <li>Drive Strength Configuration Bits for P7.0.</li> <li>Configures digital I/O Port cells to high or low output drive strength.</li> <li>0: P7.0 Output has low output drive strength.</li> <li>1: P7.0 Output has high output drive strength.</li> </ul> |

| Operational Mode                      |   |   | PCA0CPMn |   |   |   |   |   |   | PCA0PWM |   |     |    |  |

|---------------------------------------|---|---|----------|---|---|---|---|---|---|---------|---|-----|----|--|

| Software Timer                        | Х | С | 0        | 0 | 1 | 0 | 0 | А | 0 | Х       | В | XXX | XX |  |

| High Speed Output                     | Х | С | 0        | 0 | 1 | 1 | 0 | А | 0 | Х       | В | XXX | ХХ |  |

| Frequency Output                      | Х | С | 0        | 0 | 0 | 1 | 1 | А | 0 | Х       | В | XXX | ХХ |  |

| 8-Bit Pulse Width Modulator (Note 7)  | 0 | С | 0        | 0 | Е | 0 | 1 | А | 0 | Х       | В | XXX | 00 |  |

| 9-Bit Pulse Width Modulator (Note 7)  | 0 | С | 0        | 0 | Е | 0 | 1 | А | D | Х       | В | XXX | 01 |  |

| 10-Bit Pulse Width Modulator (Note 7) |   | С | 0        | 0 | Е | 0 | 1 | А | D | Х       | В | XXX | 10 |  |

| 11-Bit Pulse Width Modulator (Note 7) | 0 | С | 0        | 0 | Е | 0 | 1 | А | D | Х       | В | XXX | 11 |  |

| 16-Bit Pulse Width Modulator          | 1 | С | 0        | 0 | Е | 0 | 1 | А | 0 | Х       | в | XXX | XX |  |

### Table 33.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules

Notes:

- **1.** X = Don't Care (no functional difference for individual module if 1 or 0).

- **2.** A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

- 3. B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).

- 4. C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the

- associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0). **5.** D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated

- channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- 6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

- 7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

### 33.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

# **CONTACT INFORMATION**

#### Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.