Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | -                                                                          |

| Program Memory Type        | ROMIess                                                                    |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at80c51rd2-slrum |

|                            |                                                                            |

Table 3 shows all SFRs with their address and their reset value.

Table 4-1.SFR Mapping

|     | Bit<br>Addressable | iviapping          |                     | No                  | on-bit Addressal     | ole                  |                      |                     |     |

|-----|--------------------|--------------------|---------------------|---------------------|----------------------|----------------------|----------------------|---------------------|-----|

|     | 0/8                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                 |     |

| F8h |                    | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAPL2H<br>XXXX XXXX | CCAPL3H<br>XXXX XXXX | CCAPL4H<br>XXXX XXXX |                     | FFh |

| F0h | B<br>0000 0000     |                    |                     |                     |                      |                      |                      |                     | F7h |

| E8h |                    | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                     | EFh |

| E0h | ACC<br>0000 0000   |                    |                     |                     |                      |                      |                      |                     | E7h |

| D8h | CCON<br>00X0 0000  | CMOD<br>00XX X000  | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                     | DFh |

| D0h | PSW<br>0000 0000   |                    |                     |                     |                      |                      |                      |                     | D7h |

| C8h | T2CON<br>0000 0000 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                     | CFh |

| C0h |                    |                    |                     |                     |                      |                      |                      |                     | C7h |

| B8h | IPL0<br>X000 000   | SADEN<br>0000 0000 |                     |                     |                      |                      |                      |                     | BFh |

| B0h | P3<br>1111 1111    | IE1<br>XXXX XXX0b  | IPL1<br>XXXX XXX0b  | IPH1<br>XXXX XXX0b  |                      |                      |                      | IPH0<br>X000 0000   | B7h |

| A8h | IE0<br>0000 0000   | SADDR<br>0000 0000 |                     |                     |                      |                      |                      |                     | AFh |

| A0h | P2<br>1111 1111    |                    | AUXR1<br>XXXX XXX0  |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000 | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>XXXX XXXX  | BRL<br>0000 0000    | BDRCON<br>XXX0 0000 | KBLS<br>0000 0000    | KBE<br>0000 0000     | KBF<br>0000 0000     |                     | 9Fh |

| 90h | P1<br>1111 1111    |                    |                     |                     |                      |                      |                      | CKRL<br>1111 1111   | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XX0X 0000    | CKCON0<br>0000 0000 | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000   | 87h |

|     | 0/8                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                 |     |

## 6. Enhanced Features

In comparison to the original 80C52, the microcontrollers implement the following new features:

- X2 option

- · Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- · Hardware Watchdog

- 4-level Interrupt Priority System

- · Power-off Flag

- Power On Reset

- ONCE mode

- ALE disabling

- Some enhanced features are also located in the UART and the Timer 2

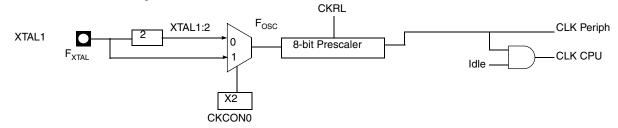

## 6.1 X2 Feature and OSC Clock Generation

The microcontroller core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divides frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Saves power consumption while keeping same CPU power (oscillator power saving).

- Saves power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increases CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

#### 6.1.1 Description

The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

Figure 6-1 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1  $\div$  2 to avoid glitches when switching from X2 to standard mode. Figure 6-2 shows the switching mode waveforms.

Figure 6-1. Clock Generation Diagram

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0h, accesses the data byte at address 0A0h, rather than P2 (whose address is 0A0h).

- The XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first bytes of external data memory. The bits XRS0 and XRS1 are used to hide a part of the available XRAM as explained in Table 8-1. This can be useful if external peripherals are mapped at addresses already used by the internal XRAM.

- With EXTRAM = 0, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than the accessible size of the XRAM will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Accesses to XRAM above 0FFH can only be done by the use of DPTR.

- With EXTRAM = 1, MOVX @ Ri and MOVX @ DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port 0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @ DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and MOVX @ DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit allows to stretch the XRAM timings; if M0 is set, the read and write pulses are extended from 6 to 30 clock periods. This is useful to access external slow peripherals.

**Table 8-2.** AUXR Register AUXR - Auxiliary Register (8Eh)

| 7 | 6 | 5  | 4 | 3    | 2    | 1      | 0  |  |

|---|---|----|---|------|------|--------|----|--|

| - | - | МО | - | XRS1 | XRS0 | EXTRAM | AO |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                 |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                                                                 |

| 6             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                                                                 |

| 5             | МО              | Pulse length Cleared to stretch MOVX control: the $\overline{\text{RD}}$ and the $\overline{\text{WR}}$ pulse length is 6 clock periods (default). Set to stretch MOVX control: the $\overline{\text{RD}}$ and the $\overline{\text{WR}}$ pulse length is 30 clock periods. |

| 4             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                                                                 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                      |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3             | XRS1            | XRAM Size                                                                                                                                                                                                        |

| 2             | XRS0            | XRS1         XRS0         XRAM Size           0         0         256 bytes (default)           0         1         512 bytes           1         0         768 bytes           1         1         1024 bytes   |

| 1             | EXTRAM          | EXTRAM bit Cleared to access internal XRAM using MOVX @ Ri/ @ DPTR. Set to access external memory. Programmed by hardware after Power-up regarding Hardware Security Byte (HSB), default setting, XRAM selected. |

| 0             | AO              | ALE Output bit Cleared, ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if X2 mode is used) (default). Set, ALE is active only if a MOVX or MOVC instruction is used.                  |

Reset Value = XX0X 00'HSB.XRAM'0b (see Table 8-1)

Not bit addressable

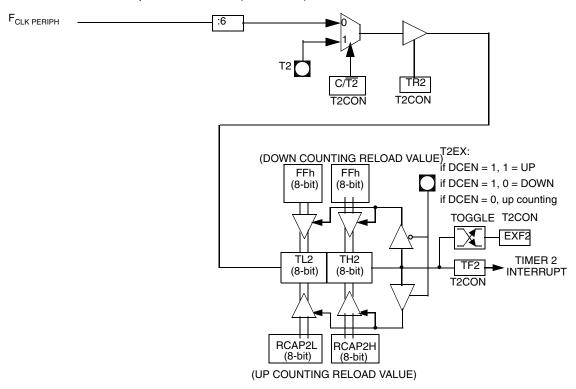

Figure 9-1. Auto-Reload Mode Up/Down Counter (DCEN = 1)

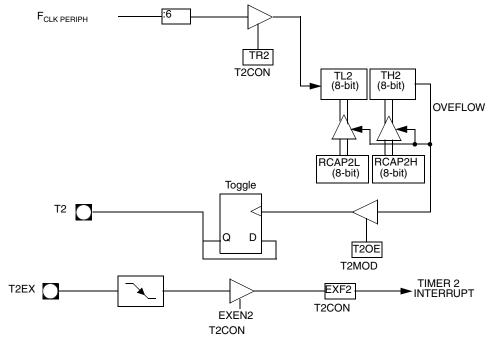

# 9.2 Programmable Clock-Output

In the clock-out mode, Timer 2 operates as a 50% duty-cycle, programmable clock generator (see Figure 9-2). The input clock increments TL2 at frequency  $F_{CLK\ PERIPH}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$$Clock-OutFrequency = \frac{F_{CLKPERIPH}}{4 \times (65536 - RCAP2H/RCAP2L)}$$

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz  $(F_{CLK\ PERIPH}/2^{16})$  to 4 MHz  $(F_{CLK\ PERIPH}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

Figure 9-2. Clock-Out Mode  $C/\overline{T2} = 07$

Table 9-1.T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7   | 6    | 5    | 4    | 3     | 2   | 1     | 0       |

|-----|------|------|------|-------|-----|-------|---------|

| TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2# | CP/RL2# |

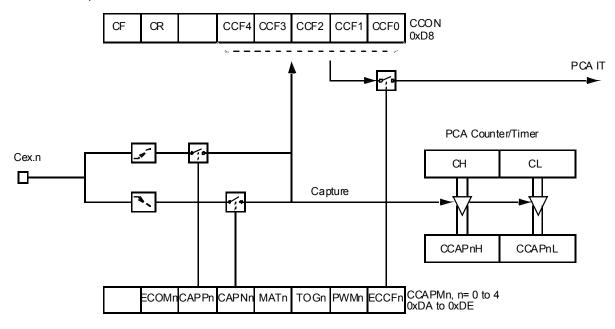

• Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags can only be cleared by software.

Table 10-2. CCON Register

CCON - PCA Counter Control Register (D8h)

| 7  | 6  | 5 | 4    | 3    | 2    | 1    | 0    |

|----|----|---|------|------|------|------|------|

| CF | CR | - | CCF4 | CCF3 | CCF2 | CCF1 | CCF0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                     |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number        | Willemonic      | PCA Counter Overflow flag                                                                                                                                                       |

| 7             | CF              | Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is set. CF may be set by either hardware or software but can only be cleared by software. |

| 6             | CR              | PCA Counter Run control bit  Must be cleared by software to turn the PCA counter off.  Set by software to turn the PCA counter on.                                              |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                                                    |

| 4             | CCF4            | PCA Module 4 interrupt flag  Must be cleared by software.  Set by hardware when a match or capture occurs.                                                                      |

| 3             | CCF3            | PCA Module 3 interrupt flag  Must be cleared by software.  Set by hardware when a match or capture occurs.                                                                      |

| 2             | CCF2            | PCA Module 2 interrupt flag  Must be cleared by software.  Set by hardware when a match or capture occurs.                                                                      |

| 1             | CCF1            | PCA Module 1 interrupt flag  Must be cleared by software.  Set by hardware when a match or capture occurs.                                                                      |

| 0             | CCF0            | PCA Module 0 interrupt flag  Must be cleared by software.  Set by hardware when a match or capture occurs.                                                                      |

Reset Value = 000X 0000b

Not bit addressable

The watchdog timer function is implemented in module 4 (see Figure 10-4).

The PCA interrupt system is shown in Figure 10-2.

**Table 10-6.** CCAPnL Registers (n = 0-4)

CCAP0L - PCA Module 0 Compare/Capture Control Register Low (0EAh)

CCAP1L - PCA Module 1 Compare/Capture Control Register Low (0EBh)

CCAP2L - PCA Module 2 Compare/Capture Control Register Low (0ECh)

CCAP3L - PCA Module 3 Compare/Capture Control Register Low (0EDh)

CCAP4L - PCA Module 4 Compare/Capture Control Register Low (0EEh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description                                       |

|---------------|-----------------|---------------------------------------------------|

| 7-0           | -               | PCA Module n Compare/Capture Control CCAPnL Value |

Reset Value = 0000 0000b

Not bit addressable

Table 10-7. CH Register

CH - PCA Counter Register High (0F9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | • | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description             |

|---------------|-----------------|-------------------------|

| 7-0           | -               | PCA counter<br>CH Value |

Reset Value = 0000 0000b

Not bit addressable

Table 10-8. CL Register

CL - PCA Counter Register Low (0E9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description             |

|---------------|-----------------|-------------------------|

| 7-0           | -               | PCA Counter<br>CL Value |

Reset Value = 0000 0000b

Not bit addressable

## 10.1 PCA Capture Mode

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCA-PnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (see Figure 10-3).

Figure 10-3. PCA Capture Mode

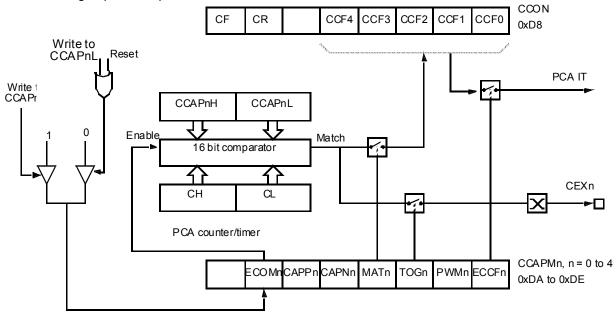

# 10.2 16-bit Software Timer/ Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (see Figure 10-4).

Figure 10-5. PCA High-speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could occur.

Once ECOM is set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing the CCAPMn register.

## 10.4 Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 10-6 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

#### 11.2.3 Reset Addresses

On reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and broadcast addresses are XXXX XXXXb (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

**Table 11-1.** SADEN Register SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

Not bit addressable

Table 11-2. SADDR Register

SADDR - Slave Address Register (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

Not bit addressable

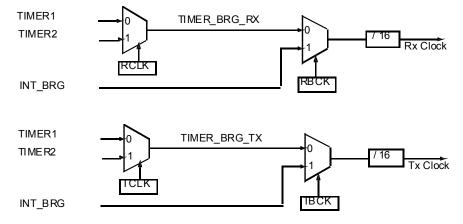

#### 11.3 Baud Rate Selection for UART for Mode 1 and 3

The Baud Rate Generator for transmit and receive clocks can be selected separately via the T2CON and BDRCON registers.

Figure 11-4. Baud Rate selection

Table 11-3. Baud Rate Selection Table UART

| TCLK<br>(T2CON) | RCLK<br>(T2CON) | TBCK<br>(BDRCON) | RBCK<br>(BDRCON) | Clock Source<br>UART Tx | Clock Source<br>UART Rx |

|-----------------|-----------------|------------------|------------------|-------------------------|-------------------------|

| 0               | 0               | 0                | 0                | Timer 1                 | Timer 1                 |

| 1               | 0               | 0                | 0                | Timer 2                 | Timer 1                 |

| 0               | 1               | 0                | 0                | Timer 1                 | Timer 2                 |

| 1               | 1               | 0                | 0                | Timer 2                 | Timer 2                 |

| Х               | 0               | 1                | 0                | INT_BRG                 | Timer 1                 |

| Х               | 1               | 1                | 0                | INT_BRG                 | Timer 2                 |

| 0               | Х               | 0                | 1                | Timer 1                 | INT_BRG                 |

| 1               | Х               | 0                | 1                | Timer 2                 | INT_BRG                 |

| Х               | Х               | 1                | 1                | INT_BRG                 | INT_BRG                 |

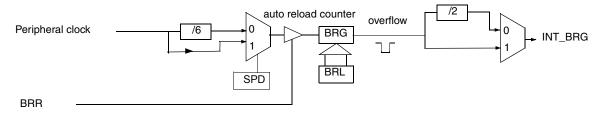

## 11.3.1 Internal Baud Rate Generator (BRG)

When the internal Baud Rate Generator is used, the Baud Rates are determined by the BRG overflow depending on the BRL reload value, the value of SPD bit (Speed Mode) in BDRCON register and the value of the SMOD1 bit in PCON register.

Figure 11-5. Internal Baud Rate

• The baud rate for UART is token by formula:

$$BaudRate = \frac{2_{SMOD} \times F_{CLKPERIPH}}{2 \times 2 \times 6 (1 - SPD) \times 16 \times [256 - (BRL)]}$$

$$(BRL) = 256 - \frac{2_{SMOD1} \times F_{CLKPERIPH}}{2 \times 2 \times 6_{(1-SPD)} \times 16 \times BaudRate}$$

# **Table 11-13.** BDRCON Register BDRCON - Baud Rate Control Register (9Bh)

7 6 5 4 3 2 1 0 - - BRR TBCK RBCK SPD SRC

| Bit    | Bit      |                                                                                                                                                                                                                                 |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                                                                                                     |

| 7      | -        | Reserved The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                     |

| 6      | -        | Reserved The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                     |

| 5      | -        | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                    |

| 4      | BRR      | Baud Rate Run Control bit Cleared to stop the internal Baud Rate Generator. Set to start the internal Baud Rate Generator.                                                                                                      |

| 3      | TBCK     | Transmission Baud rate Generator Selection bit for UART Cleared to select Timer 1 or Timer 2 for the Baud Rate Generator. Set to select internal Baud Rate Generator.                                                           |

| 2      | RBCK     | Reception Baud Rate Generator Selection bit for UART Cleared to select Timer 1 or Timer 2 for the Baud Rate Generator. Set to select internal Baud Rate Generator.                                                              |

| 1      | SPD      | Baud Rate Speed Control bit for UART Cleared to select the SLOW Baud Rate Generator. Set to select the FAST Baud Rate Generator.                                                                                                |

| 0      | SRC      | Baud Rate Source select bit in Mode 0 for UART  Cleared to select F <sub>OSC</sub> /12 as the Baud Rate Generator (F <sub>CLK PERIPH</sub> /6 in X2 mode).  Set to select the internal Baud Rate Generator for UARTs in mode 0. |

Reset Value = XXX0 0000b Not bit addressable

# IPH1 - Interrupt Priority High Register (B3h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|---|---|---|---|---|---|---|------|

| - | - | - | - | - | - | - | KBDH |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                     |

|---------------|-----------------|-------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 6             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 4             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 3             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 2             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 1             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 0             | KBDH            | Keyboard interrupt Priority High bit  KB DHKBDLPriority Level  0 0 Lowest  0 1  1 0  1 1Highest |

Reset Value = XXXX XXX0b Not bit addressable

# 12.2 Interrupt Sources and Vector Addresses

Table 12-8.

Interrupt Sources and Vector Addresses

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request | Vector<br>Address |

|--------|------------------|------------------|----------------------|-------------------|

| 0      | 0                | Reset            |                      | 0000h             |

| 1      | 1                | INT0             | IE0                  | 0003h             |

| 2      | 2                | Timer 0          | TF0                  | 000Bh             |

| 3      | 3                | INT1             | IE1                  | 0013h             |

| 4      | 4                | Timer 1          | IF1                  | 001Bh             |

| 5      | 6                | UART             | RI+TI                | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2             | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                | 003Bh             |

# 13. Keyboard Interface

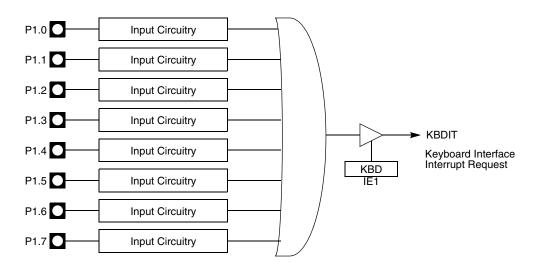

The AT80C51RD2 implement a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as alternate function of P1 and allow to exit from idle and power-down modes.

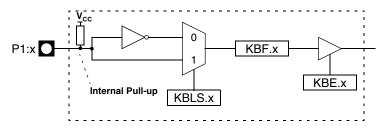

The keyboard interfaces with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 13-3), KBE, The Keyboard Interrupt Enable register (Table 13-2), and KBF, the Keyboard Flag register (Table 13-1).

#### 13.0.1 Interrupt

The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IE1) allows global enable or disable of the keyboard interrupt (see Figure 13-1). As detailed in Figure 13-2 each keyboard input has the capability to detect a programmable level according to KBLS.x bit value. Level detection is then reported in interrupt flags KBF.x that can be masked by software using KBE.x bits.

This structure allow keyboard arrangement from  $1 \times n$  to  $8 \times n$  matrix and allows usage of P1 inputs for other purpose.

Figure 13-1. Keyboard Interface Block Diagram

Figure 13-2. Keyboard Input Circuitry

#### 13.0.2 Power Reduction Mode

P1 inputs allow exit from idle and power-down modes as detailed in Section "Power-down Mode", page 56.

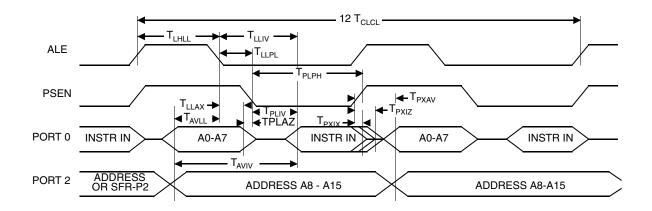

Table 17-4. AC Parameters for a Variable Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X Parameter for -<br>M Range | Units |

|-------------------|------|-------------------|-----------|------------------------------|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 15                           | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 20                           | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 20                           | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 35                           | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 15                           | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 25                           | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 45                           | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0                            | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 15                           | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 45                           | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10                           | ns    |

## 17.3.3 External Program Memory Read Cycle

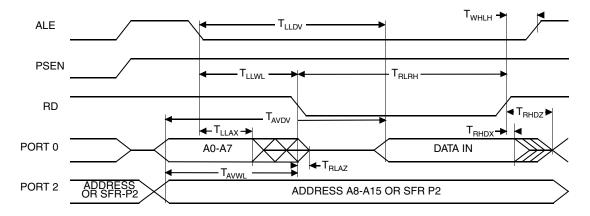

# 17.3.4 External Data Memory Characteristics

## 17.3.6 External Data Memory Read Cycle

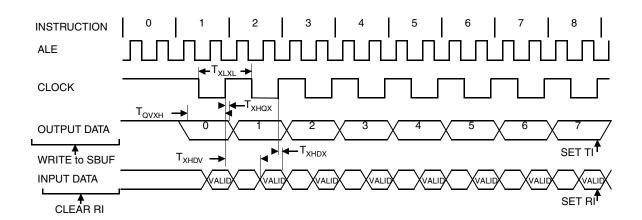

# 17.3.7 Serial Port Timing - Shift Register Mode

Table 17-7. Symbol Description

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

Table 17-8. AC Parameters for a Fix Clock

|                   | -M  |     |       |

|-------------------|-----|-----|-------|

| Symbol            | Min | Max | Units |

| T <sub>XLXL</sub> | 300 |     | ns    |

| T <sub>QVHX</sub> | 200 |     | ns    |

| T <sub>XHQX</sub> | 30  |     | ns    |

| T <sub>XHDX</sub> | 0   |     | ns    |

| T <sub>XHDV</sub> |     | 117 | ns    |

**Table 17-9.** AC Parameters for a Variable Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock | X Parameter for -<br>M Range | Units |

|-------------------|------|-------------------|----------|------------------------------|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |                              | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50                           | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20                           | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0                            | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133                          | ns    |

## 17.3.8 Shift Register Timing Waveforms

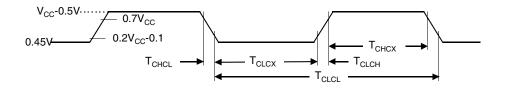

#### 17.3.9 External Clock Drive Waveforms

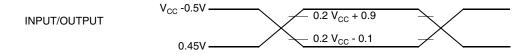

## 17.3.10 AC Testing Input/Output Waveforms

AC inputs during testing are driven at  $V_{CC}$  - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at  $V_{IH}$  min for a logic "1" and  $V_{IL}$  max for a logic "0".

## STANDARD NOTES FOR PLCC

- 1/ CONTROLLING DIMENSIONS: INCHES

- 2/ DIMENSIONING AND TOLERANCING PER ANSI Y 14.5M 1982.

3/ "D" AND "E1" DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTUSIONS. MOLD FLASH OR PROTUSIONS SHALL NOT EXCEED 0.20 mm (.008 INCH) PER SIDE.

# STANDARD NOTES FOR POFP/ VQFP / TQFP / DQFP

- 1/ CONTROLLING DIMENSIONS: INCHES

- 2/ ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y 14.5M 1982.

- 3/ "D1 AND E1" DIMENSIONS DO NOT INCLUDE MOLD PROTUSIONS.

MOLD PROTUSIONS SHALL NOT EXCEED 0.25 mm (0.010 INCH).

THE TOP PACKAGE BODY SIZE MAY BE SMALLER THAN THE BOTTOM PACKAGE BODY SIZE BY AS MUCH AS 0.15 mm.

- 4/ DATUM PLANE "H" LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

- 5/ DATUM "A" AND "D" TO BE DETERMINED AT DATUM PLANE H.

- 6/ DIMENSION "f" DOES NOT INCLUDE DAMBAR PROTUSION ALLOWABLE DAMBAR PROTUSION SHALL BE 0.08mm/.003" TOTAL IN EXCESS OF THE "f" DIMENSION AT MAXIMUM MATERIAL CONDITION.

DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.