Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        |                                                                            |

| Program Memory Type        | ROMIess                                                                    |

| EEPROM Size                |                                                                            |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at80c51rd2-slsim |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

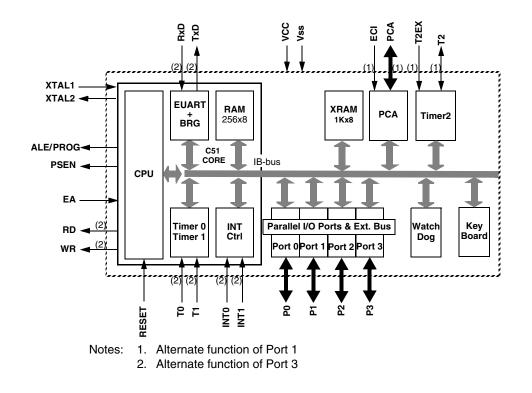

# 1. Description

AT80C51RD2 microcontrollers are high performance versions of the 80C51 8-bit microcontrollers.

The microcontrollers retain all features of the Atmel 80C52 with 256 bytes of internal RAM, a 7-source 4-level interrupt controller and three timer/counters.

In addition, the microcontrollers have a Programmable Counter Array, an XRAM of 1024 byte, a Hardware Watchdog Timer, a Keyboard Interface, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a speed improvement mechanism (X2 mode).

The microcontrollers have 2 software-selectable modes of reduced activity and 8 bit clock prescaler for further reduction in power consumption. In Idle mode, the CPU is frozen while the peripherals and the interrupt system are still operating. In the Power-down mode, the RAM is saved and all other functions are inoperative.

| Table 1. Memory Siz |

|---------------------|

|---------------------|

|            | ROM (Bytes) | XRAM (Bytes) | TOTAL RAM (Bytes) | I/O |

|------------|-------------|--------------|-------------------|-----|

| AT80C51RD2 | ROMIess     | 1024         | 1280              | 32  |

## 2. Block Diagram

#### Table 3-1.Pin Description

|                 |         | Pin Numb | er               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|---------|----------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic        | DIL     | PLCC44   | VQFP44 1.4       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> | 20      | 22       | 16               | Ι    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CC</sub> | 40      | 44       | 38               | I    | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0.0 - P0.7     | 39 - 32 | 43 - 36  | 37 - 30          | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bi-directional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. Port 0 must be polarized to $V_{CC}$ or $V_{SS}$ in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port 0 also inputs the code bytes during EPROM programming. External pull-ups are required during program verification during which P0 outputs the code bytes. |

| P1.0 - P1.7     | 1 - 8   | 2 - 9    | 40 - 44<br>1 - 3 | I/O  | <b>Port 1:</b> Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. Port 1 also receives the low-order address byte during memory programming and verification.<br>Alternate functions for T89C51RB2/RC2 Port 1 include:                                                                                                                                                           |

|                 | 1       | 2        | 40               | I/O  | P1.0: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |          |                  | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 2       | 3        | 41               | I/O  | P1.1: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |          |                  | Ι    | T2EX: Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 3       | 4        | 42               | I/O  | P1.2: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |          |                  | I    | ECI: External Clock for the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 4       | 5        | 43               | I/O  | P1.3: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |          |                  | I/O  | CEX0: Capture/Compare External I/O for PCA module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 5       | 6        | 44               | I/O  | P1.4: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |          |                  | I/O  | CEX1: Capture/Compare External I/O for PCA module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 6       | 7        | 1                | I/O  | P1.5: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |          |                  | I/O  | CEX2: Capture/Compare External I/O for PCA module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 7       | 8        | 2                | I/O  | P1.6: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |          |                  | I/O  | CEX3: Capture/Compare External I/O for PCA module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 8       | 9        | 3                | I/O  | P1.7: Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |         |          |                  | I/O  | CEX4: Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XTAL1           | 19      | 21       | 15               | I    | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XTAL2           | 18      | 20       | 14               | 0    | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Table 3-1. Pin Description (Continued)

|             | Pin Number |                |              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------|------------|----------------|--------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Mnemonic    | DIL        | PLCC44         | VQFP44 1.4   | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| P2.0 - P2.7 | 21 - 28    | 24 - 31        | 18 - 25      | I/O   | Port 2: Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins<br>that have 1s written to them are pulled high by the internal pull-ups and can be<br>used as inputs. As inputs, Port 2 pins that are externally pulled low will source<br>current because of the internal pull-ups. Port 2 emits the high-order address by<br>during fetches from external program memory and during accesses to external<br>data memory that use 16-bit addresses (MOVX @DPTR). In this application, it<br>uses strong internal pull-ups emitting 1s. During accesses to external data mem<br>that use 8-bit addresses (MOVX @Ri), Port 2 emits the contents of the P2 SFR<br>Some Port 2 pins receive the high order address bits during ROM reading and<br>verification:<br>P2.0 to P2.5 for 16 KB devices<br>P2.0 to P2.6 for 32 KB devices |  |  |

| P3.0 - P3.7 | 10 - 17    | 11,<br>13 - 19 | 5,<br>7 - 13 | I/O   | <b>Port 3:</b> Port 3 is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             | 10         | 11             | 5            | I     | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|             | 11         | 13             | 7            | 0     | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|             | 12         | 14             | 8            | I     | INTO (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|             | 13         | 15             | 9            | I     | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|             | 14         | 16             | 10           | I     | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|             | 15         | 17             | 11           | I     | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|             | 16         | 18             | 12           | 0     | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|             | 17         | 19             | 13           | 0     | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| RST         | 9          | 10             | 4            | I/O   | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ . This pin is an output when the hardware watchdog forces a system reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| ALE/PROG    | 30         | 33             | 27           | O (I) | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during Flash programming. ALE can be disabled by setting SFR's AUXR.0 bit. With this bit set, ALE will be inactive during internal fetches.                                                                                                                                                                                                                                                                                      |  |  |

| PSEN        | 29         | 32             | 26           | 0     | <b>Program Strobe Enable:</b> The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| EA          | 31         | 35             | 29           | Ι     | <b>External Access Enable:</b> $\overline{EA}$ must be externally held low to enable the device to fetch code from external program memory locations. If security level 1 is programmed, $\overline{EA}$ will be internally latched on Reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

# 4. SFR Mapping

The Special Function Registers (SFRs) of the microcontroller fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH, CCAPxL (x: 0 to 4)

- Power and clock control registers: PCON

- Hardware Watchdog Timer registers: WDTRST, WDTPRG

- Interrupt system registers: IE0, IPL0, IPH0, IE1, IPL1, IPH1

- Keyboard Interface registers: KBE, KBF, KBLS

- BRG (Baud Rate Generator) registers: BRL, BDRCON

- Clock Prescaler register: CKRL

- Others: AUXR, AUXR1, CKCON0, CKCON1

# 5. Oscillators

### 5.1 Overview

One oscillator is available for CPU:

• OSC used for high frequency (3 MHz to 40 MHz)

In order to optimize the power consumption and the execution time needed for a specific task, an internal prescaler feature has been implemented between the selected oscillator and the CPU.

### 5.2 Registers

Table 5-1.

Clock Reload Register

| 7             | 6               | 5               | 4                | 3         | 2 | 1 | 0 |

|---------------|-----------------|-----------------|------------------|-----------|---|---|---|

| -             | -               | -               | -                | -         | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description     |                  |           |   |   |   |

| 7:0           | CKRL            | Clock Reload Re | egister: Prescal | ler value |   |   |   |

Reset Value = 1111 1111b

Not bit addressable

#### 5.2.1 Prescaler Divider

A hardware RESET puts the prescaler divider in the following state:

- CKRL = FFh:  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard C51 feature) KS signal selects OSC:  $F_{CLK OUT} = F_{OSC}$

- Any value between FFh down to 00h can be written by software into CKRL register in order to divide frequency of the selected oscillator:

- CKRL = 00h: minimum frequency

- $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/1020$  (Standard Mode)

$F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/510$  (X2 Mode)

- CKRL = FFh: maximum frequency

- $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard Mode)

- $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}$  (X2 Mode)

- F<sub>CLK CPU</sub> and F<sub>CLK PERIPH</sub> In X2 mode:

$$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{2 \times (255 - CKRL)}$$

In X1 mode:

$$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSCA}}{4 \times (255 - CKRL)}$$

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0h, accesses the data byte at address 0A0h, rather than P2 (whose address is 0A0h).

- The XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first bytes of external data memory. The bits XRS0 and XRS1 are used to hide a part of the available XRAM as explained in Table 8-1. This can be useful if external peripherals are mapped at addresses already used by the internal XRAM.

- With EXTRAM = 0, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than the accessible size of the XRAM will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Accesses to XRAM above 0FFH can only be done by the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @ Ri and MOVX @ DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port 0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @ DPTR will generate a sixteen-bit address. Port2 outputs the highorder eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and MOVX @ DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit allows to stretch the XRAM timings; if M0 is set, the read and write pulses are extended from 6 to 30 clock periods. This is useful to access external slow peripherals.

Table 8-2.

AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                                 | 5 4 3 2 1 0                                                                                                                |                 |                  |        |  |  |  |  |  |

|---------------|-----------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|--------|--|--|--|--|--|

| -             | -               | МО                                | MO - XRS1 XRS0 EXTRAM AO                                                                                                   |                 |                  |        |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                       | Description                                                                                                                |                 |                  |        |  |  |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value read | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                             |                 |                  |        |  |  |  |  |  |

| 6             | -               | <b>Reserved</b><br>The value read | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                             |                 |                  |        |  |  |  |  |  |

| 5             | MO              | (default).                        | Cleared to stretch MOVX control: the $\overline{\text{RD}}$ and the $\overline{\text{WR}}$ pulse length is 6 clock periods |                 |                  |        |  |  |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value read | d from this bit is                                                                                                         | s indeterminate | . Do not set thi | is bit |  |  |  |  |  |

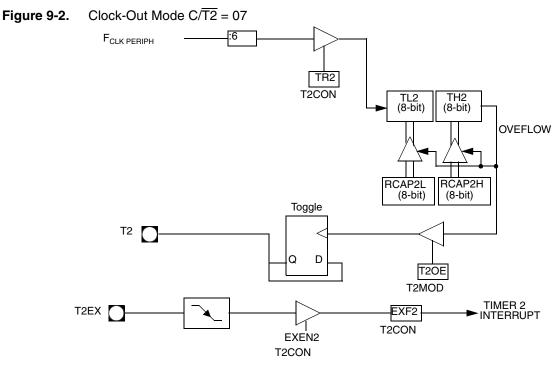

# 9. Timer 2

The Timer 2 in the AT80C51RD2 is the standard C52 Timer 2.

It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 9-1) and T2MOD (Table 9-2) registers. Timer 2 operation is similar to Timer 0 and Timer 1.  $C/\overline{T2}$  selects  $F_{OSC}/12$  (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to be incremented by the selected input.

Timer 2 has 3 operating modes: capture, auto-reload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).

Refer to the Atmel 8-bit Microcontroller Hardware description for Capture and Baud Rate Generator Modes.

Timer 2 includes the following enhancements:

- Auto-reload mode with up or down counter

- Programmable clock-output

#### 9.1 Auto-reload Mode

The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with automatic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (refer to the Atmel 8-bit Microcontroller Hardware description). If DCEN bit is set, Timer 2 acts as an Up/down timer/counter as shown in Figure 9-1. In this mode the T2EX pin controls the direction of count.

When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.

When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.

The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

Table 9-1.T2CON RegisterT2CON - Timer 2 Control Register (C8h)

| 7   | 6    | 5    | 4    | 3     | 2   | 1     | 0       |

|-----|------|------|------|-------|-----|-------|---------|

| TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2# | CP/RL2# |

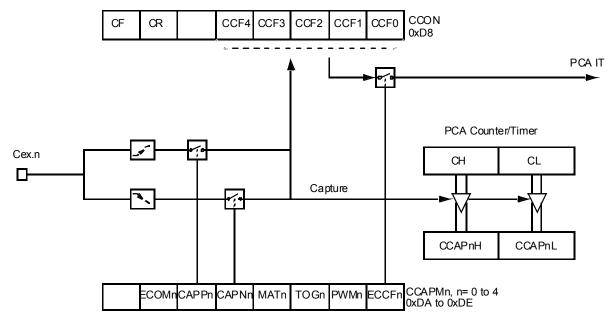

# 10. Programmable Counter Array (PCA)

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture modules. Its clock input can be programmed to count any one of the following signals:

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>)  $\div$  6

- Peripheral clock frequency  $(F_{CLK PERIPH}) \div 2$

- Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture modules can be programmed in any one of the following modes:

- Rising and/or falling edge capture

- Software timer

- High-speed output

- Pulse width modulator

Module 4 can also be programmed as a Watchdog Timer (see Section "PCA Watchdog Timer", page 33).

When the compare/capture modules are programmed in the capture mode, software timer, or high-speed output mode, an interrupt can be generated when the module executes its function. All five modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If the port is not used for the PCA, it can still be used for standard I/O.

| PCA Component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2/ECI         |

| 16-bit Module 0 | P1.3/CEX0        |

| 16-bit Module 1 | P1.4/CEX1        |

| 16-bit Module 2 | P1.5/CEX2        |

| 16-bit Module 3 | P1.6/CEX3        |

The PCA timer is a common time base for all five modules (see Figure 10-1). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD register (Table 10-1) and can be programmed to run at:

- 1/6 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- 1/2 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

## Table 10-1.CMOD Register

CMOD - PCA Counter Mode Register (D9h)

| 7             | 6               | 5                                            | 4                                                                                                                                                                                          | 3                                                          | 2                  | 1      | 0 |  |  |  |  |  |

|---------------|-----------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------|--------|---|--|--|--|--|--|

| CIDL          | WDTE            | -                                            | CPS1 CPS0 ECF                                                                                                                                                                              |                                                            |                    |        |   |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                  | Description                                                                                                                                                                                |                                                            |                    |        |   |  |  |  |  |  |

| 7             | CIDL            | Cleared to pro                               | Counter Idle Control<br>Cleared to program the PCA Counter to continue functioning during idle Mode.<br>Set to program PCA to be gated off during idle.                                    |                                                            |                    |        |   |  |  |  |  |  |

| 6             | WDTE            | Cleared to dis                               | Watchdog Timer Enable<br>Cleared to disable Watchdog Timer function on PCA Module 4.<br>Set to enable Watchdog Timer function on PCA Module 4.                                             |                                                            |                    |        |   |  |  |  |  |  |

| 5             | -               | Reserved<br>The value read                   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                            |                                                            |                    |        |   |  |  |  |  |  |

| 4             | -               | Reserved<br>The value read                   | d from this bit i                                                                                                                                                                          | s indeterminate                                            | e. Do not set this | s bit. |   |  |  |  |  |  |

| 3             | -               | Reserved<br>The value read                   | d from this bit i                                                                                                                                                                          | s indeterminate                                            | e. Do not set this | s bit. |   |  |  |  |  |  |

| 2             | CPS1            | PCA Count P                                  | ulse Select                                                                                                                                                                                |                                                            |                    |        |   |  |  |  |  |  |

| 1             | CPS0            | CPS1CPS0<br>0 0<br>0 1<br>1 0 Timer 0<br>1 1 | CPS1CPS0       Selected PCA input         0       0         Internal clock f <sub>CLK PERIPH/6</sub> 0       1         Internal clock f <sub>CLK PERIPH/2</sub> 1       0 Timer 0 Overflow |                                                            |                    |        |   |  |  |  |  |  |

| 0             | ECF             | Cleared to dis                               |                                                                                                                                                                                            | <b>low Interrupt</b><br>CCON to inhibit<br>N to generate a |                    |        |   |  |  |  |  |  |

Reset Value = 00XX X000b Not bit addressable

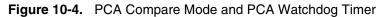

The CMOD register includes three additional bits associated with the PCA (see Figure 10-4 and Table 10-1).

- The CIDL bit which allows the PCA to stop during idle mode.

- The WDTE bit which enables or disables the watchdog function on module 4.

- The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (see Table 10-2).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

• Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags can only be cleared by software.

Table 10-2. CCON Register

CCON - PCA Counter Control Register (D8h)

| 7             | 6               | 5                         | 4                                                                                                                                                                                                                      | 3 | 2      | 1 | 0 |  |  |  |  |

|---------------|-----------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|---|---|--|--|--|--|

| CF            | CR              | -                         | - CCF4 CCF3 CCF2 CCF1 CCF0                                                                                                                                                                                             |   |        |   |   |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description               | Description                                                                                                                                                                                                            |   |        |   |   |  |  |  |  |

| 7             | CF              | Set by hardwa             | <b>PCA Counter Overflow flag</b><br>Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is<br>set. CF may be set by either hardware or software but can only be cleared by software. |   |        |   |   |  |  |  |  |

| 6             | CR              | Must be cleare            | PCA Counter Run control bit<br>Must be cleared by software to turn the PCA counter off.<br>Set by software to turn the PCA counter on.                                                                                 |   |        |   |   |  |  |  |  |

| 5             | -               | Reserved<br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                        |   |        |   |   |  |  |  |  |

| 4             | CCF4            | Must be cleare            | PCA Module 4 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                         |   |        |   |   |  |  |  |  |

| 3             | CCF3            | Must be cleare            | <b>3 interrupt fla</b><br>ed by software.<br>are when a mat                                                                                                                                                            | • | ccurs. |   |   |  |  |  |  |

| 2             | CCF2            | Must be cleare            | 2 interrupt fla<br>ed by software.<br>are when a mat                                                                                                                                                                   | - | ccurs. |   |   |  |  |  |  |

| 1             | CCF1            | Must be cleare            | PCA Module 1 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                         |   |        |   |   |  |  |  |  |

| 0             | CCF0            | Must be cleare            | <b>0 interrupt fla</b><br>ed by software.<br>are when a mat                                                                                                                                                            | • | ccurs. |   |   |  |  |  |  |

Reset Value = 000X 0000b Not bit addressable

The watchdog timer function is implemented in module 4 (see Figure 10-4).

The PCA interrupt system is shown in Figure 10-2.

## 10.1 PCA Capture Mode

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCA-PnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (see Figure 10-3).

#### Figure 10-3. PCA Capture Mode

#### 10.2 16-bit Software Timer/ Compare Mode

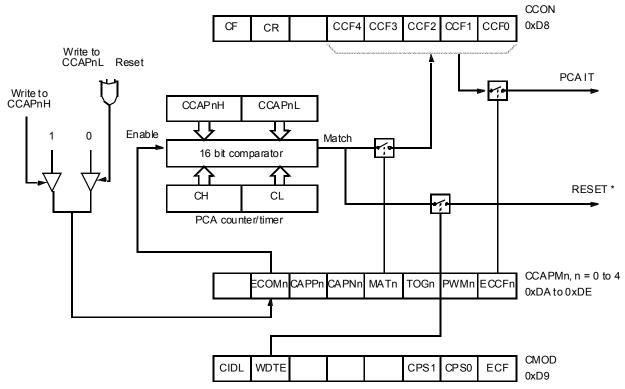

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (see Figure 10-4).

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

#### 10.3 High-speed Output Mode

In this mode, the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (see Figure 10-5).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

Figure 10-6. PCA PWM Mode

## 10.5 PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 10-4 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. Periodically change the compare value so it will never match the PCA timer.

- 2. Periodically change the PCA timer value so it will never match the compare values.

- 3. Disable the watchdog by clearing the WDTE bit before a match occurs and then reenable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

# Table 11-4.SCON RegisterSCON - Serial Control Register (98h)

| 7             | 6               | 5                                                      | 4                                                                                                                                                                                                                                                               | 3                                                                            | 2                | 1                | 0          |  |  |  |  |  |

|---------------|-----------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------|------------------|------------|--|--|--|--|--|

| FE/SM0        | SM1             | SM2                                                    | SM2 REN TB8 RB8 TI RI                                                                                                                                                                                                                                           |                                                                              |                  |                  |            |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                            |                                                                                                                                                                                                                                                                 |                                                                              |                  |                  |            |  |  |  |  |  |

| 7             | FE              | Clear to rese<br>Set by hardw                          | Framing Error bit (SMOD0 = 1)<br>Clear to reset the error state, not cleared by a valid stop bit.<br>Set by hardware when an invalid stop bit is detected.<br>SMOD0 must be set to enable access to the FE bit                                                  |                                                                              |                  |                  |            |  |  |  |  |  |

|               | SM0             | Refer to SM1                                           | Serial port Mode bit 0<br>Refer to SM1 for serial port mode selection.<br>SMOD0 must be cleared to enable access to the SM0 bit                                                                                                                                 |                                                                              |                  |                  |            |  |  |  |  |  |

| 6             | SM1             | SM1ModeDe<br>0 0Shift Re<br>1 18-bit UA<br>0 29-bit UA | <ul> <li>1 18-bit UARTVariable</li> <li>29-bit UARTf<sub>CPU PERIPH /32 or /16</sub></li> </ul>                                                                                                                                                                 |                                                                              |                  |                  |            |  |  |  |  |  |

| 5             | SM2             | Clear to disal<br>Set to enable                        | Serial port Mode 2 bit/Multiprocessor Communication Enable bit<br>Clear to disable multiprocessor communication feature.<br>Set to enable multiprocessor communication feature in mode 2 and 3, and eventually<br>mode 1. This bit should be cleared in mode 0. |                                                                              |                  |                  |            |  |  |  |  |  |

| 4             | REN             |                                                        | nable bit<br>ble serial recep<br>serial receptic                                                                                                                                                                                                                |                                                                              |                  |                  |            |  |  |  |  |  |

| 3             | TB8             | o transmit a l                                         | <b>Bit 8/Ninth bit</b><br>ogic 0 in the 9t<br>it a logic 1 in tl                                                                                                                                                                                                |                                                                              | modes 2 and 3    | 3                |            |  |  |  |  |  |

| 2             | RB8             | Cleared by hardw                                       | ardware if 9th t<br>are if 9th bit re                                                                                                                                                                                                                           | ceived in mode<br>bit received is a<br>ceived is a logic<br>s the received s | logic 0.<br>: 1. | e 0 RB8 is not u | used.      |  |  |  |  |  |

| 1             | ті              | Clear to ackn<br>Set by hardw                          | <b>Transmit Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the stop<br>bit in the other modes.                                                                        |                                                                              |                  |                  |            |  |  |  |  |  |

| 0             | RI              |                                                        | owledge interr<br>are at the end                                                                                                                                                                                                                                | upt.<br>of the 8th bit tin                                                   | ne in mode 0, s  | ee Figure 11-2   | and Figure |  |  |  |  |  |

Reset Value = 0000 0000b

Bit addressable

| Baud Rates | F <sub>osc</sub> =16 | 5.384 MHz | F <sub>osc</sub> =24 MHz |           |  |

|------------|----------------------|-----------|--------------------------|-----------|--|

|            | BRL                  | Error (%) | BRL                      | Error (%) |  |

| 115200     | 247                  | 1.23      | 243                      | 0.16      |  |

| 57600      | 238                  | 1.23      | 230                      | 0.16      |  |

| 38400      | 229                  | 1.23      | 217                      | 0.16      |  |

| 28800      | 220                  | 1.23      | 204                      | 0.16      |  |

| 19200      | 203                  | 0.63      | 178                      | 0.16      |  |

| 9600       | 149                  | 0.31      | 100                      | 0.16      |  |

| 4800       | 43                   | 1.23      | -                        | -         |  |

**Table 11-5.**Example of Computed Value when X2 = 1, SMOD1 = 1, SPD = 1

Table 11-6.Example of Computed Value when X2 = 0, SMOD1 = 0, SPD = 0

| Baud Rates | F <sub>osc</sub> =16. | 384 MHz       | F <sub>osc</sub> =24 MHz |           |  |

|------------|-----------------------|---------------|--------------------------|-----------|--|

|            | BRL                   | BRL Error (%) |                          | Error (%) |  |

| 4800       | 247                   | 1.23          | 243                      | 0.16      |  |

| 2400       | 238                   | 1.23          | 230                      | 0.16      |  |

| 1200       | 220                   | 1.23          | 202                      | 3.55      |  |

| 600        | 185                   | 0.16          | 152                      | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (see Figure 11-4.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 11-13.)

## 11.4 UART Registers

Table 11-7.SADEN Register

SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

#### Table 11-8. SADDR Register

SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

## Table 11-9.SBUF Register

SBUF - Serial Buffer Register for UART (99h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = XXXX XXXXb

#### Table 11-10. BRL Register

BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

# Table 15-2. WDTPRG Register

WDTPRG - Watchdog Timer Out Register (0A7h)

| 7                                                     | 6               | 5                         | 4                                                                                            | 3 | 2  | 1  | 0  |  |  |  |

|-------------------------------------------------------|-----------------|---------------------------|----------------------------------------------------------------------------------------------|---|----|----|----|--|--|--|

| -                                                     | -               | -                         | -                                                                                            | - | S2 | S1 | S0 |  |  |  |

| Bit<br>Number                                         | Bit<br>Mnemonic | Description               |                                                                                              |   |    |    |    |  |  |  |

| 7                                                     | -               |                           |                                                                                              |   |    |    |    |  |  |  |

| 6                                                     | -               |                           |                                                                                              |   |    |    |    |  |  |  |

| 5                                                     | -               | Reserved<br>The value rea | <b>Reserved</b><br>The value read from this bit is undetermined. Do not try to set this bit. |   |    |    |    |  |  |  |

| 4                                                     | -               |                           |                                                                                              |   |    |    |    |  |  |  |

| 3                                                     | -               |                           |                                                                                              |   |    |    |    |  |  |  |

| 2                                                     | S2              | WDT Time-o                | ut select bit                                                                                | 2 |    |    |    |  |  |  |

| 1                                                     | S1              | WDT Time-o                | ut select bit                                                                                | 1 |    |    |    |  |  |  |

| 0                                                     | S0              | WDT Time-o                | ut select bit                                                                                | 0 |    |    |    |  |  |  |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |                 |                           |                                                                                              |   |    |    |    |  |  |  |

Reset Value = XXXX X000

#### 15.2 WDT During Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Powerdown mode the user does not need to service the WDT. There are 2 methods of exiting Powerdown mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as normal, whenever the AT80C51RD2 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of power-down, it is better to reset the WDT just before entering power-down.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the AT80C51RD2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

## 17. Reduced EMI Mode

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

**Table 17-1.**AUXR RegisterAUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                                                                                                                                                                                                                            | 4                                                                                                                                                                                                                                                                                       | 3                | 2              | 1                                 | 0 |  |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-----------------------------------|---|--|--|--|--|

| -             | -               | MO                                                                                                                                                                                                                           | M0 - XRS1 XRS0 EXTRAM AO                                                                                                                                                                                                                                                                |                  |                |                                   |   |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                             |                  |                |                                   |   |  |  |  |  |