Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd20j14a-aut |

# 1. Description

The Atmel® | SMART™ SAM D20 is a series of low-power microcontrollers using the 32-bit ARM® Cortex®-M0+ processor, and ranging from 32- to 64-pins with up to 256KB Flash and 32KB of SRAM. The SAM D20 devices operate at a maximum frequency of 48MHz and reach 2.46 CoreMark/MHz. They are designed for simple and intuitive migration with identical peripheral modules, hex compatible code, identical linear address map and pin compatible migration paths between all devices in the product series. All devices include intelligent and flexible peripherals, Atmel Event System for inter-peripheral signaling, and support for capacitive touch button, slider and wheel user interfaces.

The SAM D20 devices provide the following features: In-system programmable Flash, eight-channel Event System, programmable interrupt controller, up to 52 programmable I/O pins, 32-bit real-time clock and calendar, up to eight 16-bit Timer/Counters (TC) . The timer/counters can be configured to perform frequency and waveform generation, accurate program execution timing or input capture with time and frequency measurement of digital signals. The TCs can operate in 8- or 16-bit mode, selected TCs can be cascaded to form a 32-bit TC. The series provide up to six Serial Communication Modules (SERCOM) that each can be configured to act as an USART, UART, SPI, I<sup>2</sup>C up to 400kHz, up to twenty-channel 350ksps 12-bit ADC with programmable gain and optional oversampling and decimation supporting up to 16-bit resolution, one 10-bit 350ksps DAC, two analog comparators with window mode, Peripheral Touch Controller supporting up to 256 buttons, sliders, wheels and proximity sensing; programmable Watchdog Timer, brown-out detector and power-on reset and two-pin Serial Wire Debug (SWD) program and debug interface.

All devices have accurate and low-power external and internal oscillators. All oscillators can be used as a source for the system clock. Different clock domains can be independently configured to run at different frequencies, enabling power saving by running each peripheral at its optimal clock frequency, and thus maintaining a high CPU frequency while reducing power consumption.

The SAM D20 devices have two software-selectable sleep modes, idle and standby. In idle mode the CPU is stopped while all other functions can be kept running. In standby all clocks and functions are stopped expect those selected to continue running. The device supports SleepWalking. This feature allows the peripheral to wake up from sleep based on predefined conditions, and thus allows the CPU to wake up only when needed, e.g. when a threshold is crossed or a result is ready. The Event System supports synchronous and asynchronous events, allowing peripherals to receive, react to and send events even in standby mode.

The Flash program memory can be reprogrammed in-system through the SWD interface. The same interface can be used for non-intrusive on-chip debug of application code. A boot loader running in the device can use any communication interface to download and upgrade the application program in the Flash memory.

The SAM D20 devices are supported with a full suite of program and system development tools, including C compilers, macro assemblers, program debugger/simulators, programmers and evaluation kits.

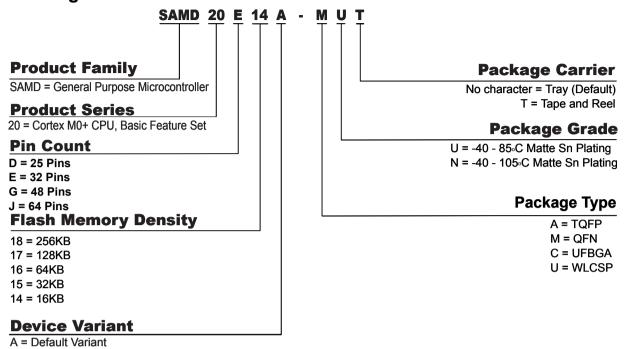

# 3. Ordering Information

## 3.1. SAM D20E

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD20E14A-AU  | 16K           | 2K           | TQFP32  | Tray         |

| ATSAMD20E14A-AUT |               |              |         | Tape & Reel  |

| ATSAMD20E14A-AN  |               |              |         | Tray         |

| ATSAMD20E14A-ANT |               |              |         | Tape & Reel  |

| ATSAMD20E14A-MU  |               |              | QFN32   | Tray         |

| ATSAMD20E14A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20E14A-MN  |               |              |         | Tray         |

| ATSAMD20E14A-MNT |               |              |         | Tape & Reel  |

# 3.2. SAM D20G

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD20G14A-AU  | 16K           | 2K           | TQFP32  | Tray         |

| ATSAMD20G14A-AUT |               |              |         | Tape & Reel  |

| ATSAMD20G14A-AN  |               |              |         | Tray         |

| ATSAMD20G14A-ANT |               |              |         | Tape & Reel  |

| ATSAMD20G14A-MU  |               |              | QFN32   | Tray         |

| ATSAMD20G14A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20G14A-MN  |               |              |         | Tray         |

| ATSAMD20G14A-MNT |               |              |         | Tape & Reel  |

| ATSAMD20G15A-AU  | 32K           | 4K           | TQFP48  | Tray         |

| ATSAMD20G15A-AUT |               |              |         | Tape & Reel  |

| ATSAMD20G15A-AN  |               |              |         | Tray         |

| ATSAMD20G15A-ANT |               |              |         | Tape & Reel  |

| ATSAMD20G15A-MU  |               |              | QFN48   | Tray         |

| ATSAMD20G15A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20G15A-MN  |               |              |         | Tray         |

| ATSAMD20G15A-MNT |               |              |         | Tape & Reel  |

| ATSAMD20G16A-AU  | 64K           | 8K           | TQFP48  | Tray         |

| ATSAMD20G16A-AUT |               |              |         | Tape & Reel  |

| ATSAMD20G16A-AN  |               |              |         | Tray         |

| ATSAMD20G16A-ANT |               |              |         | Tape & Reel  |

| ATSAMD20G16A-MU  |               |              | QFN48   | Tray         |

| ATSAMD20G16A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20G16A-MN  |               |              |         | Tray         |

| ATSAMD20G16A-MNT |               |              |         | Tape & Reel  |

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD20G17A-AU  | 128K          | 16K          | TQFP48  | Tray         |

| ATSAMD20G17A-AUT |               |              |         | Tape & Reel  |

| ATSAMD20G17A-AN  |               |              |         | Tray         |

| ATSAMD20G17A-ANT |               |              |         | Tape & Reel  |

| ATSAMD20G17A-MU  |               |              | QFN48   | Tray         |

| ATSAMD20G17A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20G17A-MN  |               |              |         | Tray         |

| ATSAMD20G17A-MNT |               |              |         | Tape & Reel  |

| ATSAMD20G17A-UUT |               |              | WLCSP45 | Tape & Reel  |

| ATSAMD20G18A-AU  | 256K          | 32K          | TQFP48  | Tray         |

| ATSAMD20G18A-AUT |               |              |         | Tape & Reel  |

| ATSAMD20G18A-AN  |               |              |         | Tray         |

| ATSAMD20G18A-ANT |               |              |         | Tape & Reel  |

| ATSAMD20G18A-MU  |               |              | QFN48   | Tray         |

| ATSAMD20G18A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20G18A-MN  |               |              |         | Tray         |

| ATSAMD20G18A-MNT |               |              |         | Tape & Reel  |

| ATSAMD20G18A-UUT |               |              | WLCSP45 | Tape & Reel  |

# 3.3. SAM D20J

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD20J14A-AU  | 16K           | 2K           | TQFP64  | Tray         |

| ATSAMD20J14A-AUT |               |              |         | Tape & Reel  |

| ATSAMD20J14A-AN  |               |              |         | Tray         |

| ATSAMD20J14A-ANT |               |              |         | Tape & Reel  |

| ATSAMD20J14A-MU  |               |              | QFN64   | Tray         |

| ATSAMD20J14A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20J14A-MN  |               |              |         | Tray         |

| ATSAMD20J14A-MNT |               |              |         | Tape & Reel  |

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD20J18A-AU  | 256K          | 32K          | TQFP64  | Tray         |

| ATSAMD20J18A-AUT |               |              |         | Tape & Reel  |

| ATSAMD20J18A-AN  |               |              |         | Tray         |

| ATSAMD20J18A-ANT |               |              |         | Tape & Reel  |

| ATSAMD20J18A-MU  |               |              | QFN64   | Tray         |

| ATSAMD20J18A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20J18A-MN  |               |              |         | Tray         |

| ATSAMD20J18A-MNT |               |              |         | Tape & Reel  |

| ATSAMD20J18A-CU  |               |              | UFBGA64 | Tray         |

| ATSAMD20J18A-CUT |               |              |         | Tape & Reel  |

# 3.4. Device Identification

The DSU - Device Service Unit peripheral provides the Device Selection bits in the Device Identification register (DID.DEVSEL) in order to identify the device by software. The device variants have a reset value of DID=0x1001drxx, with the LSB identifying the die number ('d'), the die revision ('r') and the device selection ('xx').

**Table 3-1. Device Identification Values**

| Device Variant | DID.DEVSEL | Device ID (DID) |

|----------------|------------|-----------------|

| SAMD20J18C     | 0x00       | 0x10001300      |

| SAMD20J18A     | 0x00       | 0x10001300      |

| SAMD20J17A     | 0x01       | 0x10001301      |

| SAMD20J16A     | 0x02       | 0x10001302      |

| SAMD20J15A     | 0x03       | 0x10001303      |

| SAMD20J14A     | 0x04       | 0x10001304      |

| SAMD20G18A     | 0x05       | 0x10001305      |

| SAMD20G17A     | 0x06       | 0x10001306      |

| SAMD20G16A     | 0x07       | 0x10001307      |

| SAMD20G15A     | 0x08       | 0x10001308      |

| SAMD20G14A     | 0x09       | 0x10001309      |

| SAMD20E18A     | 0x0A       | 0x1000130A      |

| SAMD20E17A     | 0x0B       | 0x1000130B      |

| SAMD20E16A     | 0x0C       | 0x1000130C      |

| SAMD20E15A     | 0x0D       | 0x1000130D      |

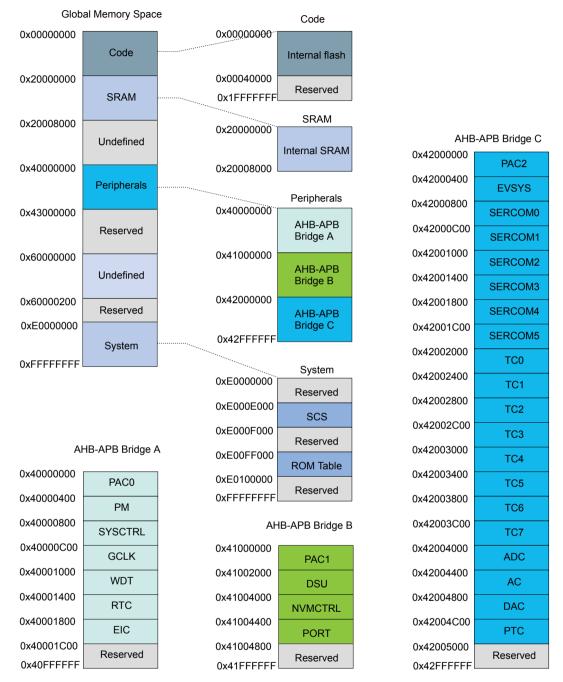

# 6. Product Mapping

Figure 6-1. Product Mapping

This figure represents the full configuration of the SAM D20 device with maximum flash and SRAM capabilities and a full set of peripherals. Refer to the Configuration Summary for details.

- The System Timer is a 24-bit timer that extends the functionality of both the processor and the NVIC. Refer to the Cortex-M0+ Technical Reference Manual for details (www.arm.com).

- Nested Vectored Interrupt Controller (NVIC)

- External interrupt signals connect to the NVIC, and the NVIC prioritizes the interrupts.

Software can set the priority of each interrupt. The NVIC and the Cortex-M0+ processor core are closely coupled, providing low latency interrupt processing and efficient processing of late arriving interrupts. Refer to Nested Vector Interrupt Controller and the Cortex-M0+ Technical Reference Manual for details (www.arm.com).

- System Control Block (SCB)

- The System Control Block provides system implementation information, and system control.

This includes configuration, control, and reporting of the system exceptions. Refer to the Cortex-M0+ Devices Generic User Guide for details (www.arm.com).

- Micro Trace Buffer (MTB)

- The CoreSight MTB-M0+ (MTB) provides a simple execution trace capability to the Cortex-M0+ processor. Refer to section Micro Trace Buffer and the CoreSight MTB-M0+ Technical Reference Manual for details (www.arm.com).

### 7.1.3. Cortex-M0+ Address Map

Table 7-2. Cortex-M0+ Address Map

| Address                               | Peripheral                                  |

|---------------------------------------|---------------------------------------------|

| 0xE000E000                            | System Control Space (SCS)                  |

| 0xE000E010                            | System Timer (SysTick)                      |

| 0xE000E100                            | Nested Vectored Interrupt Controller (NVIC) |

| 0xE000ED00                            | System Control Block (SCB)                  |

| 0x41006000 (see also Product Mapping) | Micro Trace Buffer (MTB)                    |

#### 7.1.4. I/O Interface

#### 7.1.4.1. Overview

Because accesses to the AMBA® AHB-Lite<sup>™</sup> and the single cycle I/O interface can be made concurrently, the Cortex-M0+ processor can fetch the next instructions while accessing the I/Os. This enables single cycle I/O accesses to be sustained for as long as needed. Refer to *CPU Local Bus* for more information.

#### 7.1.4.2. Description

Direct access to PORT registers.

# 7.2. Nested Vector Interrupt Controller

#### 7.2.1. Overview

The Nested Vectored Interrupt Controller (NVIC) in the SAM D20 supports 32 interrupt lines with four different priority levels. For more details, refer to the Cortex-M0+ Technical Reference Manual (www.arm.com).

### 7.2.2. Interrupt Line Mapping

Each of the 28 interrupt lines is connected to one peripheral instance, as shown in the table below. Each peripheral can have one or more interrupt flags, located in the peripheral's Interrupt Flag Status and Clear

(INTFLAG) register. The interrupt flag is set when the interrupt condition occurs. Each interrupt in the peripheral can be individually enabled by writing a one to the corresponding bit in the peripheral's Interrupt Enable Set (INTENSET) register, and disabled by writing a one to the corresponding bit in the peripheral's Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated from the peripheral when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt requests for one peripheral are ORed together on system level, generating one interrupt request for each peripheral. An interrupt request will set the corresponding interrupt pending bit in the NVIC interrupt pending registers (SETPEND/CLRPEND bits in ISPR/ICPR). For the NVIC to activate the interrupt, it must be enabled in the NVIC interrupt enable register (SETENA/CLRENA bits in ISER/ICER). The NVIC interrupt registers IPR0-IPR7 provide a priority field for each interrupt.

Table 7-3. Interrupt Line Mapping

| Peripheral Source                          | NVIC Line |

|--------------------------------------------|-----------|

| EIC NMI – External Interrupt Controller    | NMI       |

| PM – Power Manager                         | 0         |

| SYSCTRL – System Control                   | 1         |

| WDT – Watchdog Timer                       | 2         |

| RTC – Real Time Counter                    | 3         |

| EIC – External Interrupt Controller        | 4         |

| NVMCTRL – Non-Volatile Memory Controller   | 5         |

| EVSYS – Event System                       | 6         |

| SERCOM0 – Serial Communication Interface 0 | 7         |

| SERCOM1 – Serial Communication Interface 1 | 8         |

| SERCOM2 – Serial Communication Interface 2 | 9         |

| SERCOM3 – Serial Communication Interface 3 | 10        |

| SERCOM4 – Serial Communication Interface 4 | 11        |

| SERCOM5 – Serial Communication Interface 5 | 12        |

| TC0 – Timer Counter 0                      | 13        |

| TC1 – Timer Counter 1                      | 14        |

| TC2 – Timer Counter 2                      | 15        |

| TC3 – Timer Counter 3                      | 16        |

| TC4 – Timer Counter 4                      | 17        |

| TC5 – Timer Counter 5                      | 18        |

| TC6 – Timer Counter 6                      | 19        |

| TC7 – Timer Counter 7                      | 20        |

| ADC – Analog-to-Digital Converter          | 21        |

| AC – Analog Comparator                     | 22        |

|                                            |           |

# 7.4. High-Speed Bus System

#### 7.4.1. Features

High-Speed Bus Matrix has the following features:

- Symmetric crossbar bus switch implementation

- Allows concurrent accesses from different masters to different slaves

- 32-bit data bus

- Operation at a one-to-one clock frequency with the bus masters

### 7.4.2. Configuration

#### Table 7-4. Bus Matrix Masters

| Bus Matrix Masters          | Master ID |

|-----------------------------|-----------|

| CM0+ - Cortex M0+ Processor | 0         |

| DSU - Device Service Unit   | 1         |

#### Table 7-5. Bus Matrix Slaves

| Bus Matrix Slaves     | Slave ID |

|-----------------------|----------|

| Internal Flash Memory | 0        |

| AHB-APB Bridge A      | 1        |

| AHB-APB Bridge B      | 2        |

| AHB-APB Bridge C      | 3        |

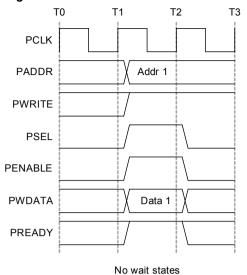

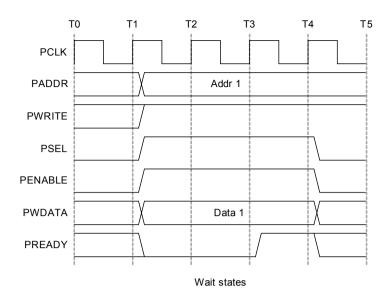

# 7.5. AHB-APB Bridge

The AHB-APB bridge is an AHB slave, providing an interface between the high-speed AHB domain and the low-power APB domain. It is used to provide access to the programmable control registers of peripherals (see *Product Mapping*).

AHB-APB bridge is based on AMBA APB Protocol Specification V2.0 (ref. as APB4) including:

- Wait state support

- Error reporting

- Transaction protection

- Sparse data transfer (byte, half-word and word)

#### Additional enhancements:

- Address and data cycles merged into a single cycle

- Sparse data transfer also apply to read access

to operate the AHB-APB bridge, the clock (CLK\_HPBx\_AHB) must be enabled. See *PM – Power Manager* for details.

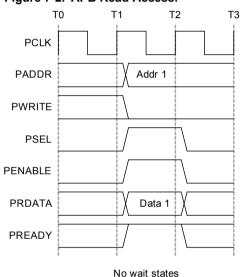

Figure 7-1. APB Write Access.

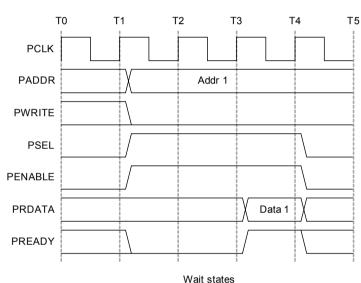

Figure 7-2. APB Read Access.

#### **Related Links**

**Product Mapping on page 19**

# 7.6. PAC - Peripheral Access Controller

#### 7.6.1. Overview

There is one PAC associated with each AHB-APB bridge. The PAC can provide write protection for registers of each peripheral connected on the same bridge.

The PAC peripheral bus clock (CLK\_PACx\_APB) can be enabled and disabled in the Power Manager. CLK\_PAC0\_APB and CLK\_PAC1\_APB are enabled are reset. CLK\_PAC2\_APB is disabled at reset. Refer to PM - Power Manager for details. The PAC will continue to operate in any sleep mode where the selected clock source is running. Write-protection does not apply for debugger access. When the debugger makes an access to a peripheral, write-protection is ignored so that the debugger can update the register.

Write-protect registers allow the user to disable a selected peripheral's write-protection without doing a read-modify-write operation. These registers are mapped into two I/O memory locations, one for clearing and one for setting the register bits. Writing a one to a bit in the Write Protect Clear register (WPCLR) will clear the corresponding bit in both registers (WPCLR and WPSET) and disable the write-protection for the corresponding peripheral, while writing a one to a bit in the Write Protect Set (WPSET) register will set the corresponding bit in both registers (WPCLR and WPSET) and enable the write-protection for the corresponding peripheral. Both registers (WPCLR and WPSET) will return the same value when read.

If a peripheral is write-protected, and if a write access is performed, data will not be written, and the peripheral will return an access error (CPU exception).

The PAC also offers a safety feature for correct program execution, with a CPU exception generated on double write-protection or double unprotection of a peripheral. If a peripheral n is write-protected and a write to one in WPSET[n] is detected, the PAC returns an error. This can be used to ensure that the application follows the intended program flow by always following a write-protect with an unprotect, and vice versa. However, in applications where a write-protected peripheral is used in several contexts, e.g., interrupts, care should be taken so that either the interrupt can not happen while the main application or other interrupt levels manipulate the write-protection status, or when the interrupt handler needs to unprotect the peripheral, based on the current protection status, by reading WPSET.

# 7.7. Register Description

Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly. Refer to the Product Mapping for PAC locations.

#### **Related Links**

**Product Mapping on page 19**

### 7.7.1. PAC0 Register Description

### 7.7.1.2. Write Protect Set

Name:

WPSET

Offset:

0x04

Reset:

0x000000

Property: -

| Bit    | 31 | 30  | 29  | 28          | 27   | 26      | 25 | 24 |

|--------|----|-----|-----|-------------|------|---------|----|----|

|        |    |     |     |             |      |         |    |    |

| Access |    |     |     |             |      |         |    |    |

| Reset  |    |     |     |             |      |         |    |    |

|        |    |     |     |             |      |         |    |    |

| Bit    | 23 | 22  | 21  | 20          | 19   | 18      | 17 | 16 |

|        |    |     |     |             |      |         |    |    |

| Access |    |     |     |             |      |         |    |    |

| Reset  |    |     |     |             |      |         |    |    |

|        |    |     |     |             |      |         |    |    |

| Bit    | 15 | 14  | 13  | 12          | 11   | 10      | 9  | 8  |

|        |    |     |     |             |      |         |    |    |

| Access |    |     |     |             |      |         |    |    |

| Reset  |    |     |     |             |      |         |    |    |

|        |    |     |     |             |      |         |    |    |

| Bit    | 7  | 6   | 5   | 4           | 3    | 2       | 1  | 0  |

|        |    | 6   |     | <del></del> |      |         | !  |    |

|        | 1  | EIC | RTC | WDT         | GCLK | SYSCTRL | PM |    |

| Access |    |     |     | I           |      |         |    |    |

#### Bit 6 - EIC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 5 - RTC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

### Bit 4 - WDT

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 3 - GCLK

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 2 - SYSCTRL

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 1 - PM

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# 7.7.2. PAC1 Register Description

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 16 - ADC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bits 15,14,13,12,11,10,9,8 - TCx

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

### Bits 7,6,5,4,3,2 - SERCOMx

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

### Bit 1 - EVSYS

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| 1 | <b>V</b> alue | Description                   |

|---|---------------|-------------------------------|

| ( | )             | Write-protection is disabled. |

| • | 1             | Write-protection is enabled.  |

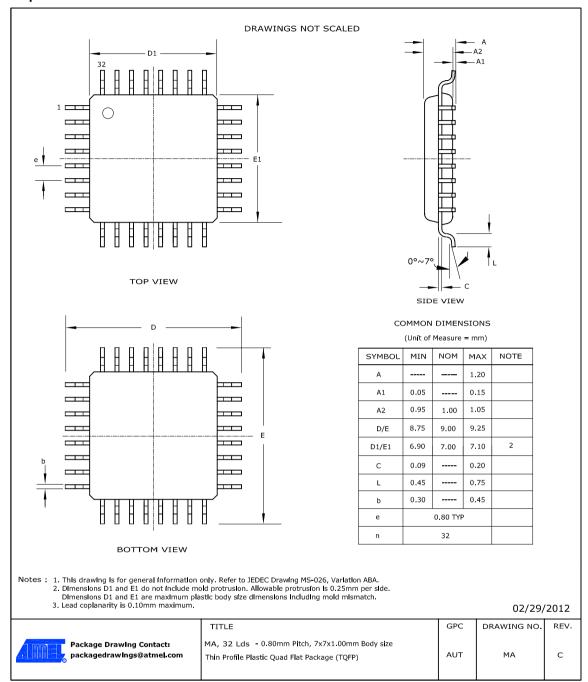

#### Table 8-4. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

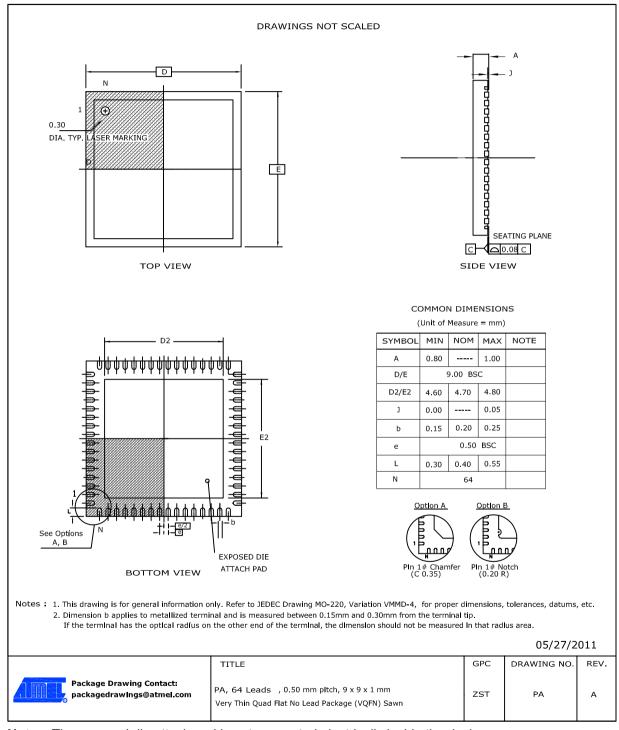

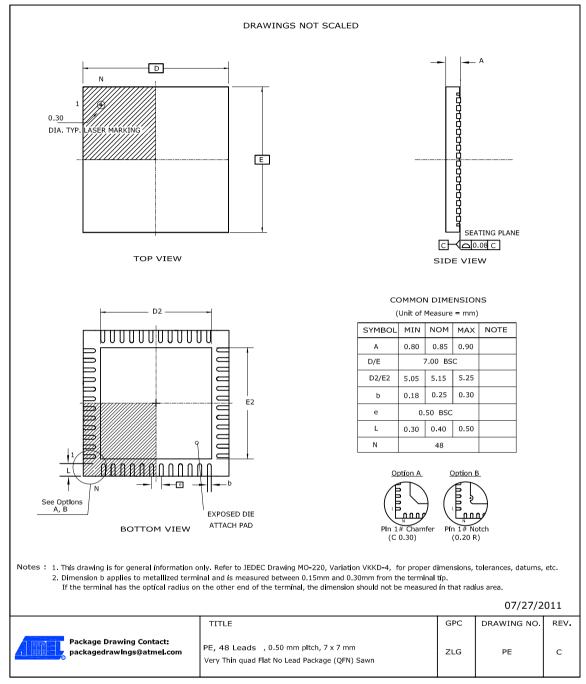

## 8.2.2. 64 pin QFN

Note: The exposed die attach pad is not connected electrically inside the device.

### Table 8-9. Package Characteristics

# Table 8-10. Package Reference

| JEDEC Drawing Reference | MO-220 |

|-------------------------|--------|

| JESD97 Classification   | E8     |

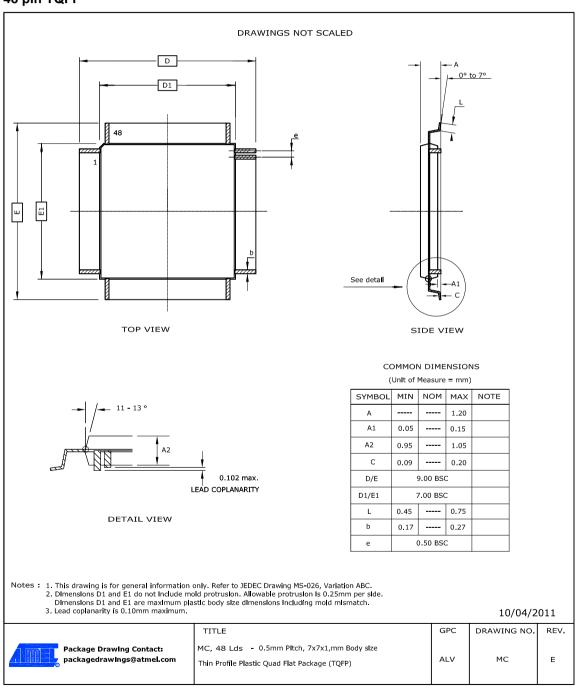

# 8.2.4. 48 pin TQFP

# Table 8-11. Device and Package Maximum Weight

| 140 | mg |

|-----|----|

|     | 9  |

# Table 8-12. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

| ,                          |      |

# Table 8-13. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

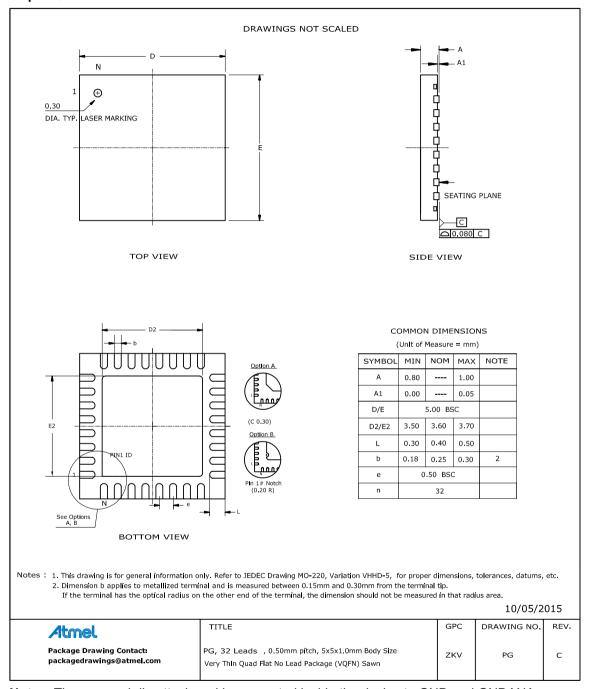

### 8.2.5. 48 pin QFN

**Note:** The exposed die attach pad is not connected electrically inside the device.

Table 8-14. Device and Package Maximum Weight

| 140 | mg |

|-----|----|

|-----|----|

**Table 8-15. Package Characteristics**

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

# 8.2.7. 32 pin TQFP

Table 8-20. Device and Package Maximum Weight

| 100 | mg |

|-----|----|

|     |    |

### Table 8-21. Package Charateristics

| Moisture Sensitivity Level MSL3 |  |

|---------------------------------|--|

|---------------------------------|--|

### Table 8-22. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

## 8.2.8. 32 pin QFN

Note: The exposed die attach pad is connected inside the device to GND and GNDANA.

Table 8-23. Device and Package Maximum Weight

| 90 mg | 90 | mg |

|-------|----|----|

|-------|----|----|