# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 20x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP Exposed Pad                                                        |

| Supplier Device Package    | 64-TQFP-EP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd20j16b-aut |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD20J15A-AU  | 32K           | 4K           | TQFP64  | Tray         |

| ATSAMD20J15A-AUT | -             |              |         | Tape & Reel  |

| ATSAMD20J15A-AN  | -             |              |         | Tray         |

| ATSAMD20J15A-ANT | -             |              |         | Tape & Reel  |

| ATSAMD20J15A-MU  | -             |              | QFN64   | Tray         |

| ATSAMD20J15A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20J15A-MN  | -             |              |         | Tray         |

| ATSAMD20J15A-MNT | -             |              |         | Tape & Reel  |

| ATSAMD20J16A-AU  | 64K           | 8K           | TQFP64  | Tray         |

| ATSAMD20J16A-AUT | -             |              |         | Tape & Reel  |

| ATSAMD20J16A-AN  | -             |              |         | Tray         |

| ATSAMD20J16A-ANT | -             |              |         | Tape & Reel  |

| ATSAMD20J16A-MU  | -             |              | QFN64   | Tray         |

| ATSAMD20J16A-MUT | -             |              |         | Tape & Reel  |

| ATSAMD20J16A-MN  | -             |              |         | Tray         |

| ATSAMD20J16A-MNT | -             |              |         | Tape & Reel  |

| ATSAMD20J16A-CU  | -             |              | UFBGA64 | Tray         |

| ATSAMD20J16A-CUT |               |              |         | Tape & Reel  |

| ATSAMD20J17A-AU  | 128K          | 16K          | TQFP64  | Tray         |

| ATSAMD20J17A-AUT | -             |              |         | Tape & Reel  |

| ATSAMD20J17A-AN  | -             |              |         | Tray         |

| ATSAMD20J17A-ANT | -             |              |         | Tape & Reel  |

| ATSAMD20J17A-MU  |               |              | QFN64   | Tray         |

| ATSAMD20J17A-MUT |               |              |         | Tape & Reel  |

| ATSAMD20J17A-MN  |               |              |         | Tray         |

| ATSAMD20J17A-MNT |               |              |         | Tape & Reel  |

| ATSAMD20J17A-CU  |               |              | UFBGA64 | Tray         |

| ATSAMD20J17A-CUT |               |              |         | Tape & Reel  |

| Ordering Code    | FLASH (bytes) | SRAM (bytes) | Package | Carrier Type |

|------------------|---------------|--------------|---------|--------------|

| ATSAMD20J18A-AU  | 256K          | 32K          | TQFP64  | Tray         |

| ATSAMD20J18A-AUT | _             |              |         | Tape & Reel  |

| ATSAMD20J18A-AN  | _             |              |         | Tray         |

| ATSAMD20J18A-ANT | _             |              |         | Tape & Reel  |

| ATSAMD20J18A-MU  | _             |              | QFN64   | Tray         |

| ATSAMD20J18A-MUT | _             |              |         | Tape & Reel  |

| ATSAMD20J18A-MN  | _             |              |         | Tray         |

| ATSAMD20J18A-MNT |               |              |         | Tape & Reel  |

| ATSAMD20J18A-CU  |               |              | UFBGA64 | Tray         |

| ATSAMD20J18A-CUT |               |              |         | Tape & Reel  |

# 3.4. Device Identification

The DSU - Device Service Unit peripheral provides the Device Selection bits in the Device Identification register (DID.DEVSEL) in order to identify the device by software. The device variants have a reset value of DID=0x1001drxx, with the LSB identifying the die number ('d'), the die revision ('r') and the device selection ('xx').

|  | Table 3-1. | Device | Identification | Values |

|--|------------|--------|----------------|--------|

|--|------------|--------|----------------|--------|

| Device Variant | DID.DEVSEL | Device ID (DID) |

|----------------|------------|-----------------|

| SAMD20J18C     | 0x00       | 0x10001300      |

| SAMD20J18A     | 0x00       | 0x10001300      |

| SAMD20J17A     | 0x01       | 0x10001301      |

| SAMD20J16A     | 0x02       | 0x10001302      |

| SAMD20J15A     | 0x03       | 0x10001303      |

| SAMD20J14A     | 0x04       | 0x10001304      |

| SAMD20G18A     | 0x05       | 0x10001305      |

| SAMD20G17A     | 0x06       | 0x10001306      |

| SAMD20G16A     | 0x07       | 0x10001307      |

| SAMD20G15A     | 0x08       | 0x10001308      |

| SAMD20G14A     | 0x09       | 0x10001309      |

| SAMD20E18A     | 0x0A       | 0x1000130A      |

| SAMD20E17A     | 0x0B       | 0x1000130B      |

| SAMD20E16A     | 0x0C       | 0x1000130C      |

| SAMD20E15A     | 0x0D       | 0x1000130D      |

| Device Variant | DID.DEVSEL  | Device ID (DID) |

|----------------|-------------|-----------------|

| SAMD20E14A     | 0x0E        | 0x1000130E      |

| Reserved       | 0x0F        |                 |

| SAMD20G18U     | 0x10        | 0x10001310      |

| SAMD20G17U     | 0x11        | 0x10001311      |

| Reserved       | 0x12 - 0xFF |                 |

**Note:** The device variant (last letter of the ordering number) is independent of the die revision (DSU.DID.REVISION): The device variant denotes functional differences, whereas the die revision marks evolution of the die. The device variant denotes functional differences, whereas the die revision marks evolution of the die.

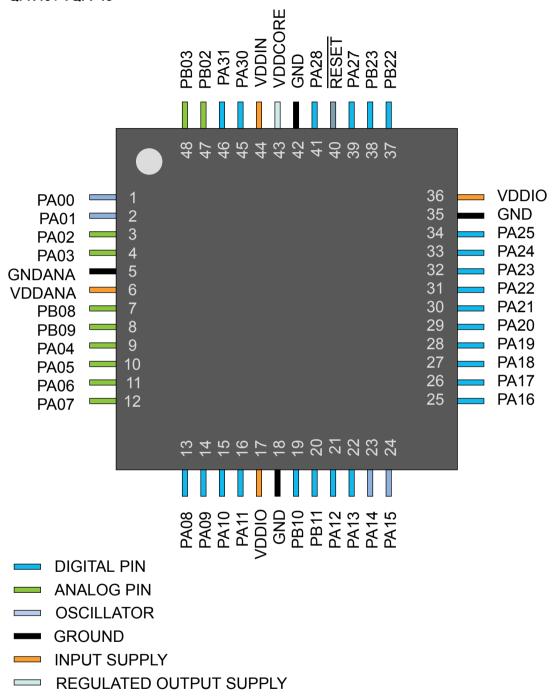

- 5.2. SAM D20G

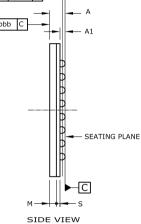

- 5.2.1. QFN48 / TQFP48

RESET PIN

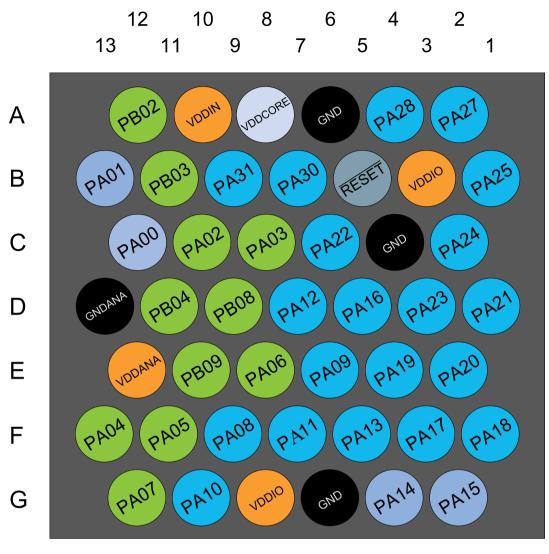

5.2.2. WLCSP45

- DIGITAL PIN

- ANALOG PIN

- OSCILLATOR

- GROUND

- INPUT SUPPLY

- REGULATED OUTPUT SUPPLY

- RESET PIN

Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 17 Atmel-42129P-SAM D20\_Datasheet\_Summary-09/2016

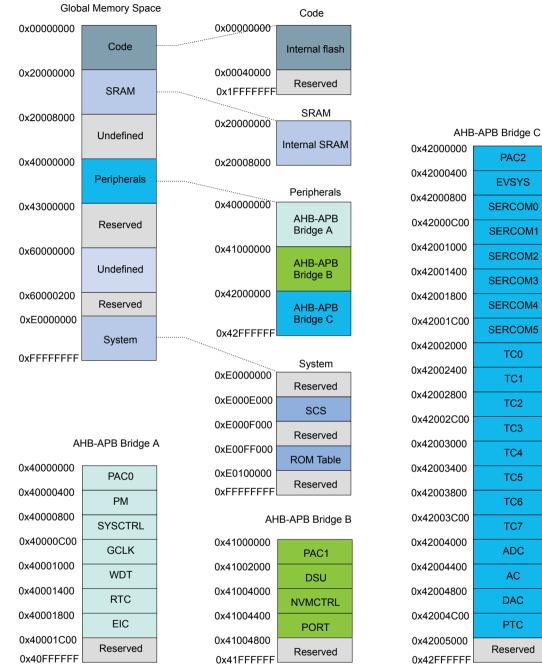

#### 6. **Product Mapping**

#### Figure 6-1. Product Mapping

PAC2 **EVSYS** SERCOM0 SERCOM1 SERCOM2 SERCOM3 SERCOM4 SERCOM5 TC0 TC1 TC2 тС3 TC4 TC5 TC6 TC7 ADC AC DAC PTC Reserved 0x42FFFFFF

This figure represents the full configuration of the SAM D20 device with maximum flash and SRAM capabilities and a full set of peripherals. Refer to the Configuration Summary for details.

# 7. Processor And Architecture

# 7.1. Cortex M0+ Processor

The SAM D20 implements the ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ processor, based on the ARMv6 Architecture and Thumb<sup>®</sup>-2 ISA. The Cortex M0+ is 100% instruction set compatible with its predecessor, the Cortex-M0 core, and upward compatible to Cortex-M3 and M4 cores. The ARM Cortex-M0+ implemented is revision r0p1. For more information refer to http://www.arm.com.

## 7.1.1. Cortex M0+ Configuration

#### Table 7-1. Cortex M0+ Configuration

| Features                         | Configurable option          | Device configuration  |

|----------------------------------|------------------------------|-----------------------|

| Interrupts                       | External interrupts 0-32     | 28                    |

| Data endianness                  | Little-endian or big-endian  | Little-endian         |

| SysTick timer                    | Present or absent            | Present               |

| Number of watchpoint comparators | 0, 1, 2                      | 2                     |

| Number of breakpoint comparators | 0, 1, 2, 3, 4                | 4                     |

| Halting debug support            | Present or absent            | Present               |

| Multiplier                       | Fast or small                | Fast (single cycle)   |

| Single-cycle I/O port            | Present or absent            | Present               |

| Wake-up interrupt controller     | Supported or not supported   | Not supported         |

| Vector Table Offset Register     | Present or absent            | Present               |

| Unprivileged/Privileged support  | Present or absent            | Absent <sup>(1)</sup> |

| Memory Protection Unit           | Not present or 8-region      | Not present           |

| Reset all registers              | Present or absent            | Absent                |

| Instruction fetch width          | 16-bit only or mostly 32-bit | 32-bit                |

#### Note:

1. All software run in privileged mode only.

The ARM Cortex-M0+ core has two bus interfaces:

- Single 32-bit AMBA-3 AHB-Lite system interface that provides connections to peripherals and all system memory, which includes flash and RAM.

- Single 32-bit I/O port bus interfacing to the PORT with 1-cycle loads and stores.

# 7.1.2. Cortex-M0+ Peripherals

- System Control Space (SCS)

- The processor provides debug through registers in the SCS. Refer to the Cortex-M0+ Technical Reference Manual for details (www.arm.com).

- System Timer (SysTick)

# 7.4. High-Speed Bus System

#### 7.4.1. Features

High-Speed Bus Matrix has the following features:

- Symmetric crossbar bus switch implementation

- Allows concurrent accesses from different masters to different slaves

- 32-bit data bus

- Operation at a one-to-one clock frequency with the bus masters

#### 7.4.2. Configuration

#### Table 7-4. Bus Matrix Masters

| Bus Matrix Masters          | Master ID |

|-----------------------------|-----------|

| CM0+ - Cortex M0+ Processor | 0         |

| DSU - Device Service Unit   | 1         |

#### Table 7-5. Bus Matrix Slaves

| Bus Matrix Slaves     | Slave ID |

|-----------------------|----------|

| Internal Flash Memory | 0        |

| AHB-APB Bridge A      | 1        |

| AHB-APB Bridge B      | 2        |

| AHB-APB Bridge C      | 3        |

# 7.5. AHB-APB Bridge

The AHB-APB bridge is an AHB slave, providing an interface between the high-speed AHB domain and the low-power APB domain. It is used to provide access to the programmable control registers of peripherals (see *Product Mapping*).

AHB-APB bridge is based on AMBA APB Protocol Specification V2.0 (ref. as APB4) including:

- Wait state support

- Error reporting

- Transaction protection

- Sparse data transfer (byte, half-word and word)

Additional enhancements:

- Address and data cycles merged into a single cycle

- Sparse data transfer also apply to read access

to operate the AHB-APB bridge, the clock (CLK\_HPBx\_AHB) must be enabled. See *PM* – *Power Manager* for details.

Write-protect registers allow the user to disable a selected peripheral's write-protection without doing a read-modify-write operation. These registers are mapped into two I/O memory locations, one for clearing and one for setting the register bits. Writing a one to a bit in the Write Protect Clear register (WPCLR) will clear the corresponding bit in both registers (WPCLR and WPSET) and disable the write-protection for the corresponding bit in both registers (WPCLR and WPSET) and enable the write-protection for the corresponding bit in both registers (WPCLR and WPSET) and enable the write-protection for the corresponding bit in both registers (WPCLR and WPSET) and enable the write-protection for the corresponding bit in both registers (WPCLR and WPSET) and enable the write-protection for the corresponding peripheral. Both registers (WPCLR and WPSET) will return the same value when read.

If a peripheral is write-protected, and if a write access is performed, data will not be written, and the peripheral will return an access error (CPU exception).

The PAC also offers a safety feature for correct program execution, with a CPU exception generated on double write-protection or double unprotection of a peripheral. If a peripheral n is write-protected and a write to one in WPSET[n] is detected, the PAC returns an error. This can be used to ensure that the application follows the intended program flow by always following a write-protect with an unprotect, and vice versa. However, in applications where a write-protected peripheral is used in several contexts, e.g., interrupts, care should be taken so that either the interrupt can not happen while the main application or other interrupt levels manipulate the write-protection status, or when the interrupt handler needs to unprotect the peripheral, based on the current protection status, by reading WPSET.

# 7.7. Register Description

Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32bit register, and the 8-bit halves of a 16-bit register can be accessed directly. Refer to the Product Mapping for PAC locations.

#### **Related Links**

Product Mapping on page 19

#### 7.7.1. PAC0 Register Description

Name: WPCLR Offset: 0x00 **Reset:** 0x000000 Property: -Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset 15 9 8 Bit 14 13 12 11 10 Access Reset Bit 6 5 3 2 0 7 4 1 EIC RTC WDT GCLK SYSCTRL PM Access R/W R/W R/W R/W R/W R/W 0 0 0 0 0 0 Reset

#### Bit 6 – EIC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bit 5 – RTC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 4 – WDT

Writing a zero to these bits has no effect.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bit 3 – GCLK

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

|   | Value | Description                   |

|---|-------|-------------------------------|

| ( | 0     | Write-protection is disabled. |

|   | 1     | Write-protection is enabled.  |

#### Bit 2 – SYSCTRL

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 1 – PM

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### 7.7.2. PAC1 Register Description

Name: WPCLR Offset: 0x00 **Reset:** 0x000002 Property: -Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset 15 9 8 Bit 14 13 12 11 10 Access Reset Bit 6 5 3 2 0 7 4 1 МТВ PORT NVMCTRL DSU Access R/W R/W R/W R/W 0 0 0 1 Reset

#### Bit 6 – MTB

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

### Bit 3 – PORT

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 2 – NVMCTRL

Writing a zero to these bits has no effect.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bit 1 – DSU

Writing a zero to these bits has no effect.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bit 16 – ADC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bits 15,14,13,12,11,10,9,8 - TCx

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bits 7,6,5,4,3,2 – SERCOMx

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 1 – EVSYS

Writing a zero to these bits has no effect.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

7.7.3.2. Write Protect Set

Name:

WPSET

Offset:

0x04

Reset:

0x00800000

Property:

| Bit    | 31      | 30      | 29      | 28      | 27      | 26      | 25    | 24  |

|--------|---------|---------|---------|---------|---------|---------|-------|-----|

| Access |         |         |         |         |         |         |       |     |

| Reset  |         |         |         |         |         |         |       |     |

| Bit    | 23      | 22      | 21      | 20      | 19      | 18      | 17    | 16  |

|        |         |         |         |         | PTC     | DAC     | AC    | ADC |

| Access |         |         | •       |         | R/W     | R/W     | R/W   | R/W |

| Reset  |         |         |         |         | 0       | 0       | 0     | 0   |

|        |         |         |         |         |         |         |       |     |

| Bit    | 15      | 14      | 13      | 12      | 11      | 10      | 9     | 8   |

|        | TC7     | TC6     | TC5     | TC4     | TC3     | TC2     | TC1   | TC0 |

| Access | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W   | R/W |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0       | 0     | 0   |

|        |         |         |         |         |         |         |       |     |

| Bit    | 7       | 6       | 5       | 4       | 3       | 2       | 1     | 0   |

|        | SERCOM5 | SERCOM4 | SERCOM3 | SERCOM2 | SERCOM1 | SERCOM0 | EVSYS |     |

| Access | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W   |     |

| Reset  | 0       | 0       | 0       | 0       | 0       | 0       | 0     |     |

#### Bit 19 – PTC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bit 18 – DAC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

# Bit 17 – AC

Writing a zero to these bits has no effect.

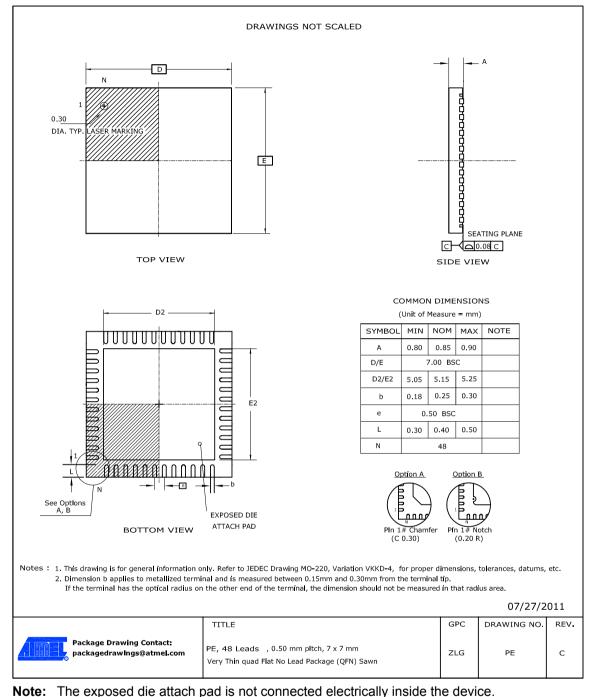

#### Table 8-5. Device and Package Maximum Weight

| 200 | mg |

|-----|----|

|     |    |

#### Table 8-6. Package Charateristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|

#### Table 8-7. Package Reference

| JEDEC Drawing Reference | MO-220 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

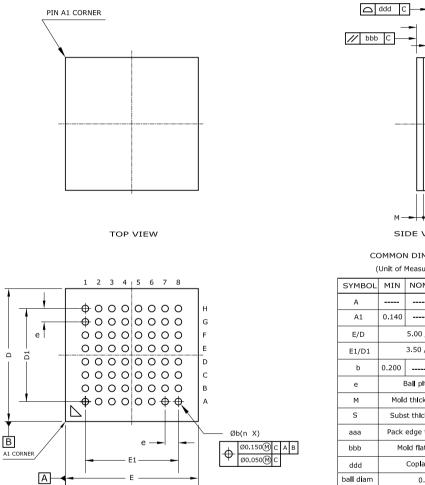

#### 8.2.3. 64-ball UFBGA

#### COMMON DIMENSIONS

| (         | Unit of I | Measure            | = mm)     |         |

|-----------|-----------|--------------------|-----------|---------|

| SYMBOL    | MIN       | NOM                | МАХ       | NOTE    |

| А         |           |                    | 0.650     |         |

| A1        | 0.140     |                    | 0.240     |         |

| E/D       |           | 5.00/5             | 5.00      |         |

| E1/D1     |           | 3.50 / 3           | 8.50      |         |

| b         | 0.200     |                    | 0.300     |         |

| е         | E         | Ball pltch         | n:0.50    | 0       |

| м         | Molo      | d thickne          | ess : 0.2 | 250 ref |

| S         | Subs      | st th <b>i</b> ckn | ess:0.    | 136 ref |

| aaa       | Pack      | edge to            | erance    | : 0.100 |

| bbb       | Mo        | old flatne         | ess:0.:   | 100     |

| ddd       |           | Copla :            | 0.100     |         |

| ball diam |           | 0.25               | 50        |         |

| n         |           | 64                 |           |         |

Notes : 1. This drawing is for general information only. Refer to JEDEC Drawing MO-280, Variation UCCBB for proper dimensions, tolerances, datums, etc. 2. Array as seen from the bottom of the package.

Dimension A includes stand-off height A1, package body thickness, and lid height, but does not include attached features.

Dimension b is measured at the maximum ball diameter, parallel to primary datum C.

Table 8-8. Device and Package Maximum Weight

BOTTOM VIEW

☐ aaa(4X)

| 27.4 | mg |

|------|----|

|------|----|

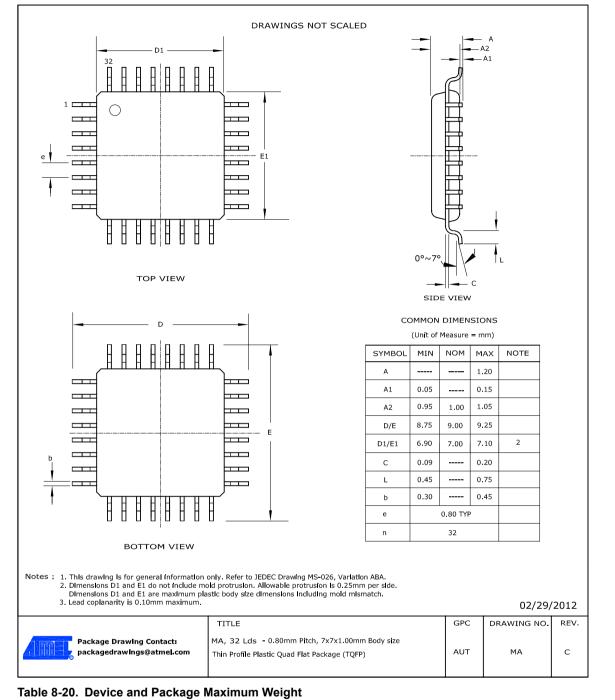

#### Table 8-11. Device and Package Maximum Weight

| 140 | mg |

|-----|----|

|     |    |

#### Table 8-12. Package Characteristics

| Moisture Sensitivity Level    | MSL3   |

|-------------------------------|--------|

| Table 8-13. Package Reference |        |

| JEDEC Drawing Reference       | MS-026 |

| JESD97 Classification         | E3     |

|  |  |  | · · · · · · · · · · · · · · · · · · · |

|--|--|--|---------------------------------------|

|  |  |  |                                       |

|  |  |  |                                       |

#### Table 8-14. Device and Package Maximum Weight

|--|

#### Table 8-15. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|                            |      |

8.2.7. 32 pin TQFP

| 100 | mg |

|-----|----|

#### Table 8-21. Package Charateristics

| Moisture Sensitivity Level | MSL3 |  |

|----------------------------|------|--|

|                            |      |  |

Atmel SAM D20E / SAM D20G / SAM D20J Summary [DATASHEET] 47 Atmel-42129P-SAM D20\_Datasheet\_Summary-09/2016

#### Table 8-27. Package Characteristics

| Moisture Sensitivity Level    | MSL1   |  |  |  |

|-------------------------------|--------|--|--|--|

| Table 8-28. Package Reference |        |  |  |  |

| JEDEC Drawing Reference       | MO-220 |  |  |  |

| JESD97 Classification         | E1     |  |  |  |

# 8.3. Soldering Profile

The following table gives the recommended soldering profile from J-STD-20.

Table 8-29.

| Profile Feature                            | Green Package  |

|--------------------------------------------|----------------|

| Average Ramp-up Rate (217°C to peak)       | 3°C/s max.     |

| Preheat Temperature 175°C ±25°C            | 150-200°C      |

| Time Maintained Above 217°C                | 60-150s        |

| Time within 5°C of Actual Peak Temperature | 30s            |

| Peak Temperature Range                     | 260°C          |

| Ramp-down Rate                             | 6°C/s max.     |

| Time 25°C to Peak Temperature              | 8 minutes max. |

A maximum of three reflow passes is allowed per component.