#

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 83                                                                                    |

| Program Memory Size        | 192KB (192K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 10K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                  |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 100-LQFP                                                                              |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1165agc-ueu-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

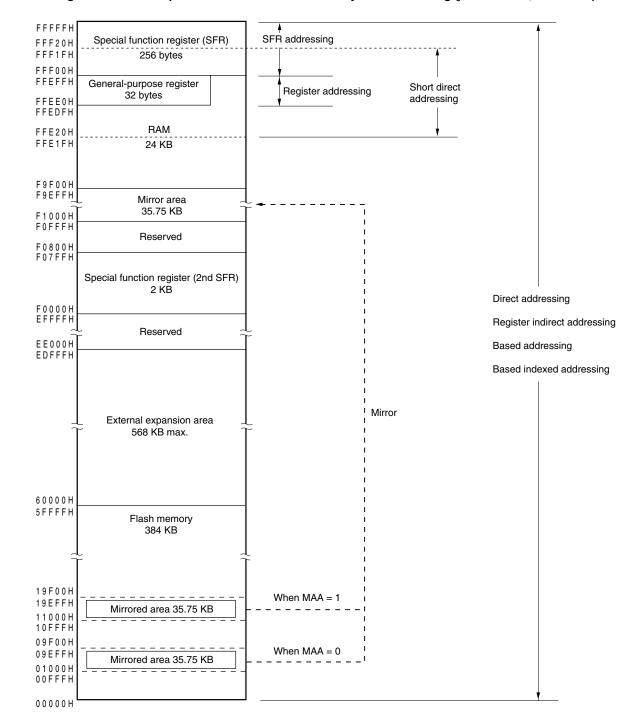

#### <R> Figure 3-14. Correspondence Between Data Memory and Addressing (µPD78F1167, 78F1167A)

| Address | Special Function Register (SFR) Name             | Symbol       | R/W | Manip        | ulable Bit   | Range        | After Reset |

|---------|--------------------------------------------------|--------------|-----|--------------|--------------|--------------|-------------|

|         |                                                  |              |     | 1-bit        | 8-bit        | 16-bit       |             |

| F0017H  | A/D port configuration register                  | ADPC         | R/W | -            | $\checkmark$ | -            | 10H         |

| F0030H  | Pull-up resistor option register 0               | PU0          | R/W |              |              | -            | 00H         |

| F0031H  | Pull-up resistor option register 1               | PU1          | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F0033H  | Pull-up resistor option register 3               | PU3          | R/W |              | $\checkmark$ | -            | 00H         |

| F0034H  | Pull-up resistor option register 4               | PU4          | R/W |              | $\checkmark$ | -            | 00H         |

| F0035H  | Pull-up resistor option register 5               | PU5          | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F0036H  | Pull-up resistor option register 6               | PU6          | R/W | $\checkmark$ | $\checkmark$ | _            | 00H         |

| F0037H  | Pull-up resistor option register 7               | PU7          | R/W |              | $\checkmark$ | -            | 00H         |

| F0038H  | Pull-up resistor option register 8               | PU8          | R/W |              | $\checkmark$ | -            | 00H         |

| F003CH  | Pull-up resistor option register 12              | PU12         | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F003DH  | Pull-up resistor option register 13              | PU13         | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F003EH  | Pull-up resistor option register 14              | PU14         | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F0040H  | Port input mode register 0                       | PIM0         | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F0044H  | Port input mode register 4                       | PIM4         | R/W |              | $\checkmark$ | -            | 00H         |

| F004EH  | Port input mode register 14                      | PIM14        | R/W |              | $\checkmark$ | -            | 00H         |

| F0050H  | Port output mode register 0                      | POM0         | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F0054H  | Port output mode register 4                      | POM4         | R/W | $\checkmark$ | $\checkmark$ | _            | 00H         |

| F005EH  | Port output mode register 14                     | POM14        | R/W | $\checkmark$ | $\checkmark$ | _            | 00H         |

| F0060H  | Noise filter enable register 0                   | NFEN0        | R/W | $\checkmark$ | $\checkmark$ | -            | 00H         |

| F0061H  | Noise filter enable register 1                   | NFEN1        | R/W |              | $\checkmark$ | -            | 00H         |

| F00F0H  | Peripheral enable register 0                     | PER0         | R/W |              | $\checkmark$ | -            | 00H         |

| F00F1H  | Peripheral enable register 1                     | PER1         | R/W |              | $\checkmark$ | -            | 00H         |

| F00F2H  | Internal high-speed oscillator trimming register | HIOTRM       | R/W | -            | $\checkmark$ | -            | 10H         |

| F00F3H  | Operation speed mode control register            | OSMC         | R/W | -            | $\checkmark$ | -            | 00H         |

| F00F4H  | Regulator mode control register                  | RMC          | R/W | -            | $\checkmark$ | -            | 00H         |

| F00FEH  | BCD adjust result register                       | BCDADJ       | R   | -            | $\checkmark$ | -            | Undefined   |

| F0100H  | Serial status register 00                        | SSR00L SSR00 | R   | _            |              | $\checkmark$ | 0000H       |

| F0101H  |                                                  | _            |     | -            | _            |              |             |

| F0102H  | Serial status register 01                        | SSR01L SSR01 | R   | -            |              |              | 0000H       |

| F0103H  |                                                  | _            |     | _            | -            |              |             |

| F0104H  | Serial status register 02                        | SSR02L SSR02 | R   | -            | $\checkmark$ |              | 0000H       |

| F0105H  |                                                  | _            |     | -            | -            |              |             |

| F0106H  | Serial status register 03                        | SSR03L SSR03 | R   | -            | $\checkmark$ |              | 0000H       |

| F0107H  |                                                  | _            |     | -            | -            |              |             |

| F0108H  | Serial flag clear trigger register 00            | SIR00L SIR00 | R/W | -            | $\checkmark$ |              | 0000H       |

| F0109H  |                                                  | _            |     | -            | -            |              |             |

| F010AH  | Serial flag clear trigger register 01            | SIR01L SIR01 | R/W | I            | $\checkmark$ | $\checkmark$ | 0000H       |

| F010BH  | ]                                                | _            |     | I            | -            |              |             |

| F010CH  | Serial flag clear trigger register 02            | SIR02L SIR02 | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       |

| F010DH  | ]                                                | _            |     | I            | _            |              |             |

| F010EH  | Serial flag clear trigger register 03            | SIR03L SIR03 | R/W | I            | $\checkmark$ | $\checkmark$ | 0000H       |

| F010FH  |                                                  |              |     | _            | _            |              |             |

Table 3-6. Extended SFR (2nd SFR) List (1/5)

#### 3.3.4 Register direct addressing

# [Function]

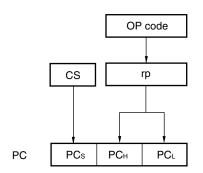

Register direct addressing stores in the program counter (PC) the contents of a general-purpose register pair (AX/BC/DE/HL) and CS register of the current register bank specified with the instruction word as 20-bit data, and specifies the program address. Register direct addressing can be applied only to the CALL AX, BC, DE, HL, and BR AX instructions.

| Address: FF | FA3H Afte | r reset: 07H | R/W   |                     |            |                        |                  |            |  |

|-------------|-----------|--------------|-------|---------------------|------------|------------------------|------------------|------------|--|

| Symbol      | 7         | 6            | 5     | 4                   | 3          | 2                      | 1                | 0          |  |

| OSTS        | 0         | 0            | 0     | 0                   | 0          | OSTS2                  | OSTS1            | OSTS0      |  |

|             |           |              |       |                     |            |                        |                  |            |  |

|             | OSTS2     | OSTS1        | OSTS0 |                     | Oscillatio | on stabilization tim   | ne selection     |            |  |

|             |           |              |       |                     |            | $f_x = 10 \text{ MHz}$ | fx =             | 20 MHz     |  |

|             | 0         | 0            | 0     | 2 <sup>8</sup> /fx  |            | 25.6 <i>μ</i> s        | Setting          | prohibited |  |

|             | 0         | 0            | 1     | 2 <sup>9</sup> /fx  |            | 51.2 <i>μ</i> s        | 25.6 <i>μ</i> s  |            |  |

|             | 0         | 1            | 0     | 2 <sup>10</sup> /fx |            | 102.4 <i>μ</i> s       | 51.2 <i>μ</i> s  |            |  |

|             | 0         | 1            | 1     | 2 <sup>11</sup> /fx |            | 204.8 <i>µ</i> s       | 102.4 <i>μ</i>   | S          |  |

|             | 1         | 0            | 0     | 2 <sup>13</sup> /fx |            | 819.2 <i>μ</i> s       | 409.6 <i>µ</i> t | S          |  |

|             | 1         | 0            | 1     | 2 <sup>15</sup> /fx |            | 3.27 ms                | 1.64 ms          |            |  |

|             | 1         | 1            | 0     | 2 <sup>17</sup> /fx |            | 13.11 ms               | 6.55 ms          |            |  |

|             | 1         | 1            | 1     | 2 <sup>18</sup> /fx |            | 26.21 ms               | 13.11 m          | S          |  |

#### Figure 6-5. Format of Oscillation Stabilization Time Select Register (OSTS)

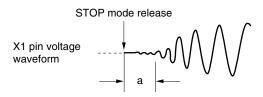

Cautions 1. To set the STOP mode when the X1 clock is used as the CPU clock, set the OSTS register before executing the STOP instruction.

- 2. Setting the oscillation stabilization time to 20  $\mu$ s or less is prohibited.

- 3. To change the setting of the OSTS register, be sure to confirm that the counting operation of the OSTC register has been completed.

- 4. Do not change the value of the OSTS register during the X1 clock oscillation stabilization time.

- 5. The oscillation stabilization time counter counts up to the oscillation stabilization time set by OSTS.

In the following cases, set the oscillation stabilization time of OSTS to the value greater than or equal to the count value which is to be checked by the OSTC register.

- If the X1 clock starts oscillation while the internal high-speed oscillation clock or subsystem clock is being used as the CPU clock.

- If the STOP mode is entered and then released while the internal high-speed oscillation clock is being used as the CPU clock with the X1 clock oscillating. (Note, therefore, that only the status up to the oscillation stabilization time set by OSTS is set to OSTC after the STOP mode is released.)

- 6. The X1 clock oscillation stabilization wait time does not include the time until clock oscillation starts ("a" below).

Remark fx: X1 clock oscillation frequency

# (15) Port mode registers 0, 1, 3, 4, 13, 14 (PM0, PM1, PM3, PM4, PM13, PM14)

These registers set input/output of ports 0, 1, 3, 4, 13, and 14 in 1-bit units.

When using the P01/T000, P16/T001/TI01/INTP5/EX30, P17/T002/TI02/EX31, P31/T003/TI03/INTP4, P42/T004/TI04, P46/T005/TI05/INTP1, P131/T006/TI06, and P145/T007/TI07 pins for timer output, set PM01, PM16, PM17, PM31, PM42, PM46, PM131, and PM145 and the output latches of P01, P16, P17, P31, P42, P46, P131, and P145 to 0.

When using the P00/TI00, P16/T001/TI01/INTP5/EX30, P17/T002/TI02/EX31, P31/T003/TI03/INTP4, P42/T004/TI04, P46/T005/TI05/INTP1, P131/T006/TI06, and P145/T007/TI07 pins for timer input, set PM00, PM16, PM17, PM31, PM42, PM46, PM131, and PM145 to 1. At this time, the output latches of P00, P16, P17, P31, P42, P46, P131, and P145 may be 0 or 1.

PM0, PM1, PM3, PM4, PM13, and PM14 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets these registers to FFH.

#### Figure 7-23. Format of Port Mode Registers 0, 1, 3, 4, 13, and 14 (PM0, PM1, PM3, PM4, PM13, PM14)

| Address: FFF | 20H After re | eset: FFH R/V | N                            |               |                  |                 |           |       |  |

|--------------|--------------|---------------|------------------------------|---------------|------------------|-----------------|-----------|-------|--|

| Symbol       | 7            | 6             | 5                            | 4             | 3                | 2               | 1         | 0     |  |

| PM0          | 1            | PM06          | PM05                         | PM04          | PM03             | PM02            | PM01      | PM00  |  |

|              |              |               |                              |               | <u>.</u>         |                 |           |       |  |

| Address: FFF | 21H After re | eset: FFH R/V | N                            |               |                  |                 |           |       |  |

| Symbol       | 7            | 6             | 5                            | 4             | 3                | 2               | 1         | 0     |  |

| PM1          | PM17         | PM16          | PM15                         | PM14          | PM13             | PM12            | PM11      | PM10  |  |

|              |              |               |                              |               |                  |                 |           |       |  |

| Address: FFF | 23H After re | eset: FFH R/V | N                            |               |                  |                 |           |       |  |

| Symbol       | 7            | 6             | 5                            | 4             | 3                | 2               | 1         | 0     |  |

| PM3          | 1            | 1             | 1                            | 1             | 1                | 1               | PM31      | PM30  |  |

|              |              |               |                              |               |                  |                 |           |       |  |

| Address: FFF | 24H After re | eset: FFH R/V | N                            |               |                  |                 |           |       |  |

| Symbol       | 7            | 6             | 5                            | 4             | 3                | 2               | 1         | 0     |  |

| PM4          | PM47         | PM46          | PM45                         | PM44          | PM43             | PM42            | PM41      | PM40  |  |

|              |              |               |                              |               |                  |                 |           |       |  |

| Address: FFF | 2DH After r  | eset: FEH R/  | W                            |               |                  |                 |           |       |  |

| Symbol       | 7            | 6             | 5                            | 4             | 3                | 2               | 1         | 0     |  |

| PM13         | 1            | 1             | 1                            | 1             | 1                | 1               | PM131     | 0     |  |

|              |              |               |                              |               |                  |                 |           |       |  |

| Address: FFF | 2EH After re | eset: FFH R/\ | Ν                            |               |                  |                 |           |       |  |

| Symbol       | 7            | 6             | 5                            | 4             | 3                | 2               | 1         | 0     |  |

| PM14         | 1            | 1             | PM145                        | PM144         | PM143            | PM142           | PM141     | PM140 |  |

|              |              |               |                              |               |                  |                 |           |       |  |

|              | PMmn         |               | Pmn pin                      | I/O mode sele | ction (m = 0, 1, | 3, 4, 13, 14; n | = 0 to 7) |       |  |

|              | 0            | Output mode   | (output buffer o             | on)           |                  |                 |           |       |  |

|              | 1            | Input mode (o | put mode (output buffer off) |               |                  |                 |           |       |  |

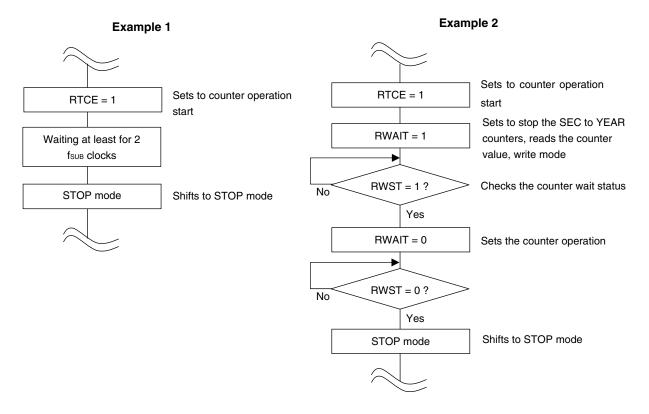

#### 8.4.2 Shifting to STOP mode after starting operation

Perform one of the following processing when shifting to STOP mode immediately after setting RTCE to 1.

However, after setting RTCE to 1, this processing is not required when shifting to STOP mode after the first INTRTC interrupt has occurred.

- Shifting to STOP mode when at least two subsystem clocks (fsuB) (about 62 μ s) have elapsed after setting RTCE to 1 (see Figure 8-20, Example 1).

- Checking by polling RWST to become 1, after setting RTCE to 1 and then setting RWAIT to 1. Afterward, setting RWAIT to 0 and shifting to STOP mode after checking again by polling that RWST has become 0 (see Figure 8-20, Example 2).

#### 13.4 Operation Stop Mode

Each serial interface of serial array unit has the operation stop mode.

In this mode, serial communication cannot be executed, thus reducing the power consumption.

P04/SCK10/SCL10, In addition. the P02/SO10/TxD1, P03/SI10/SDA10/RxD1, P10/SCK00/EX24, P11/SI00/BxD0/EX25. P12/SO00/TxD0/EX26. P13/TxD3/EX27, P43/SCK01. P44/SI01. P45/SO01. P142/SCK20/SCL20, P143/SI20/SDA20/RxD2, or P144/SO20/TxD2 pin can be used as ordinary port pins in this mode.

#### 13.4.1 Stopping the operation by units

The stopping of the operation by units is set by using peripheral enable register 0 (PER0).

PER0 is used to enable or disable use of each peripheral hardware macro. Clock supply to a hardware macro that is not used is stopped in order to reduce the power consumption and noise.

To stop the operation of serial array unit 0, set bit 2 (SAU0EN) to 0.

To stop the operation of serial array unit 1, set bit 3 (SAU1EN) to 0.

#### Figure 13-22. Peripheral Enable Register 0 (PER0) Setting When Stopping the Operation by Units

~

#### (a) Peripheral enable register 0 (PER0) ... Set only the bit of SAUm to be stopped to 0. 4

|      | 7     | 0     | 5              | 4              | 3      | 2      | I | 0      |

|------|-------|-------|----------------|----------------|--------|--------|---|--------|

| PER0 | RTCEN | DACEN | ADCEN          | <b>IIC0EN</b>  | SAU1EN | SAU0EN |   | TAU0EN |

|      | ×     | ×     | ×              | ×              | 0/1    | 0/1    | 0 | 0/1    |

|      |       | C     | ontrol of SAU  |                |        |        |   |        |

|      |       | 0     | : Stops supply | of input clock | (      |        |   |        |

|      |       | 4     | . Cumpling inn | ut ala al      |        |        |   |        |

1: Supplies input clock

-

- Cautions 1. If SAUmEN = 0, writing to a control register of serial array unit m is ignored, and, even if the register is read, only the default value is read (except for input switch control register (ISC), noise filter enable register (NFEN0), port input mode registers (PIM0, PIM4, PIM14), port output mode registers (POM0, POM4, POM14), port mode registers (PM0, PM1, PM4, PM14), and port registers (P0, P1, P4, P14)).

- 2. Be sure to clear bit 1 of the PER0 register to 0.

**Remark** m: Unit number (m = 0, 1), : Setting disabled (fixed by hardware)

x: Bits not used with serial array units (depending on the settings of other peripheral functions) 0/1: Set to 0 or 1 depending on the usage of the user

#### 13.5.7 Calculating transfer clock frequency

The transfer clock frequency for 3-wire serial I/O (CSI00, CSI01, CSI10, CSI20) communication can be calculated by the following expressions.

#### (1) Master

(Transfer clock frequency) = {Operation clock (MCK) frequency of target channel} ÷ (SDRmn[15:9] + 1) ÷ 2 [Hz]

#### (2) Slave

(Transfer clock frequency) = {Frequency of serial clock (SCK) supplied by master}<sup>Note</sup> [Hz]

Note The permissible maximum transfer clock frequency is fmck/6.

- **Remarks 1.** The value of SDRmn[15:9] is the value of bits 15 to 9 of the SDRmn register (0000000B to 1111111B) and therefore is 0 to 127.

- **2.** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2)

The operation clock (MCK) is determined by serial clock select register m (SPSm) and bit 15 (CKSmn) of serial mode register mn (SMRmn).

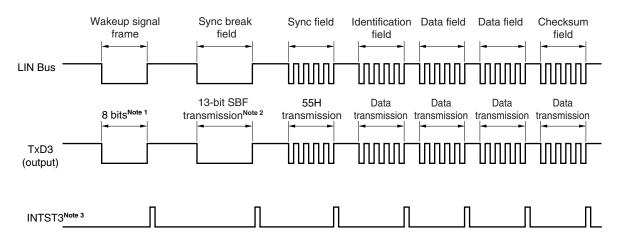

#### Figure 13-85. Transmission Operation of LIN

Notes 1. The baud rate is set so as to satisfy the standard of the wakeup signal and data of 00H is transmitted.

A sync break field is defined to have a width of 13 bits and output a low level. Where the baud rate for main transfer is N [bps], therefore, the baud rate of the sync break field is calculated as follows.

(Baud rate of sync break field) = 9/13 × N

By transmitting data of 00H at this baud rate, a sync break field is generated.

3. INTST3 is output upon completion of transmission. INTST3 is also output when SBF transmission is executed.

Remark The interval between fields is controlled by software.

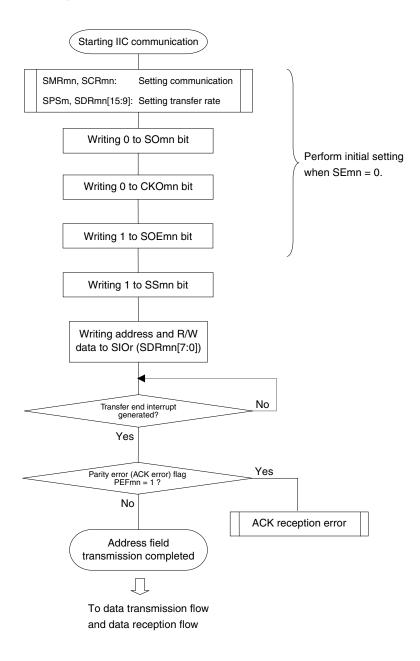

#### Figure 13-96. Flowchart of Address Field Transmission

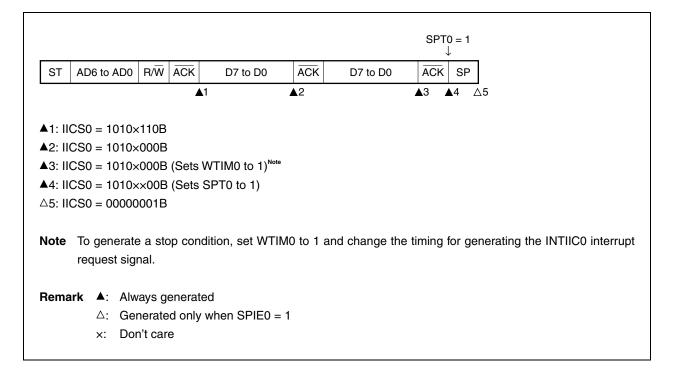

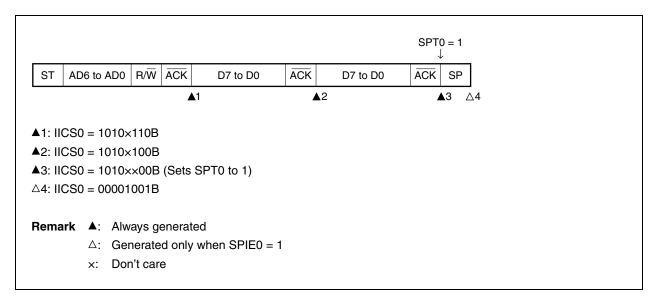

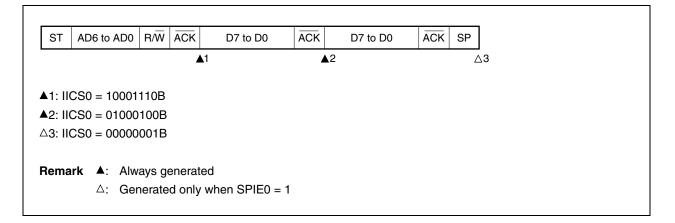

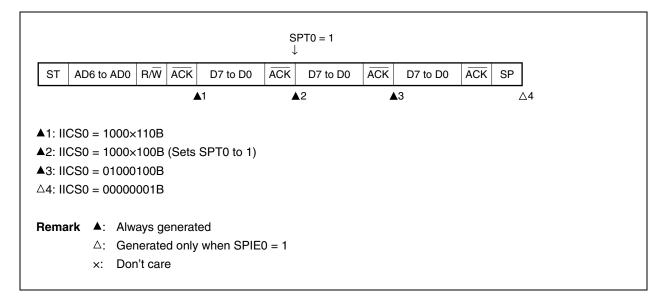

#### (c) Start ~ Code ~ Data ~ Data ~ Stop (extension code transmission)

# (i) When WTIM0 = 0

(ii) When WTIM0 = 1

(ii) When WTIM0 = 1

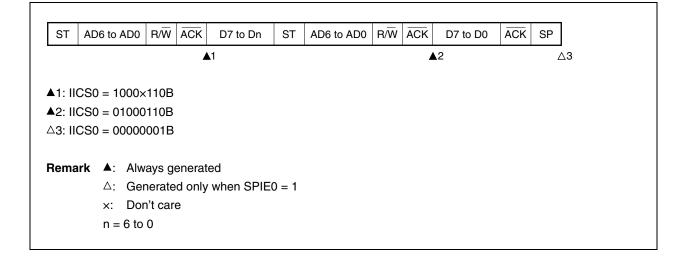

#### (d) When loss occurs due to restart condition during data transfer

### (i) Not extension code (Example: does not match with SVA0)

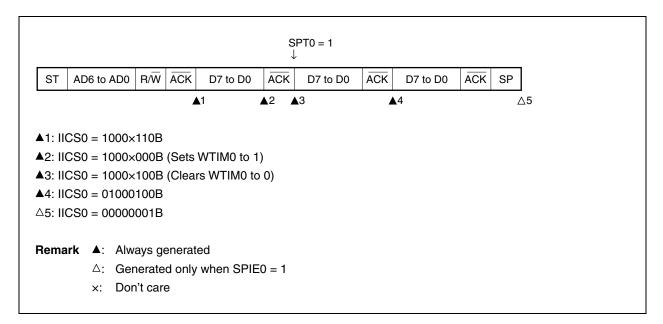

- (h) When arbitration loss occurs due to low-level data when attempting to generate a stop condition

- (i) When WTIM0 = 0

# (ii) When WTIM0 = 1

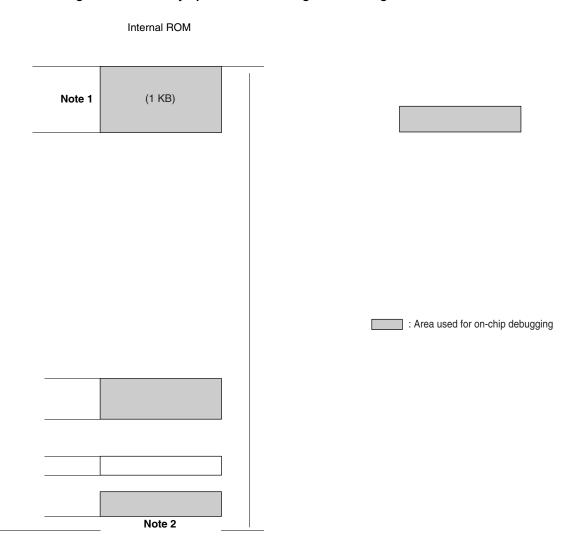

# Figure 26-2. Memory Spaces Where Debug Monitor Programs Are Allocated

#### DC Characteristics (1/16)

| $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, 1.8 \text{ V} \le \text{AV}_{REF0} \le \text{V}_{DD}, 1.8 \text{ V} \le \text{AV}_{REF0} \le$ | $-1 \leq V DD$ , |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Vss = EVsso = EVss1 = AVss = 0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| Parameter              | Symbol | Conditions                                                             |                                       | MIN. | TYP. | MAX.  | Unit |

|------------------------|--------|------------------------------------------------------------------------|---------------------------------------|------|------|-------|------|

| Output current,        | Іон1   | Per pin for P00 to P06, P10 to P17, 4.                                 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -3.0  | mA   |

| high <sup>Note 1</sup> |        | P30, P31, P40 to P47, P50 to P57,                                      | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -1.0  | mA   |

|                        |        | P64 to P67, P70 to P77, P80 to P87,<br>P120, P130, P131, P140 to P145  | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -1.0  | mA   |

|                        |        | P120, P130, P131, P140 to P145<br>(When duty = 70% <sup>Note 2</sup> ) | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -20.0 | mA   |

|                        |        |                                                                        | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -10.0 | mA   |

|                        |        |                                                                        | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -5.0  | mA   |

|                        |        | Total of P05, P06, P10 to P17, P30,                                    | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -30.0 | mA   |

|                        |        | P31, P50 to P57, P64 to P67,                                           | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -19.0 | mA   |

|                        |        | P70 to P77, P80 to P87<br>(When duty = 70% <sup>Note 2</sup> )         | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -10.0 | mA   |

|                        |        | Total of all pins                                                      | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -50.0 | mA   |

|                        |        | (When duty = $60\%^{\text{Note 2}}$ )                                  | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -29.0 | mA   |

|                        |        |                                                                        | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -15.0 | mA   |

|                        | Іон2   | Per pin for P20 to P27, P150 to P157                                   | $AV_{\text{REF0}} \leq V_{\text{DD}}$ |      |      | -0.1  | mA   |

|                        |        | Per pin for P110, P111                                                 | $AV_{\text{REF1}} \leq V_{\text{DD}}$ |      |      | -0.1  | mA   |

**Notes 1.** Value of current at which the device operation is guaranteed even if the current flows from EV<sub>DD0</sub> or EV<sub>DD1</sub> pin to an output pin.

Specification under conditions where the duty factor is 60% or 70%.

The output current value that has changed the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

• Total output current of pins =  $(I_{OH} \times 0.7)/(n \times 0.01)$

<Example> Where n = 50% and  $I_{OH} = -20.0 \text{ mA}$

Total output current of pins =  $(-20.0 \times 0.7)/(50 \times 0.01) = -28.0$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

#### Caution P02 to P04, P43, P45, P142 to P144 do not output high level in N-ch open-drain mode.

# DC Characteristics (13/16)

# μPD78F1167, 78F1167A, 78F1168, 78F1168A

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{Vdd} = \text{EV}\text{dd} = \text{EV}\text{dd} = \text{EV}\text{dd} \le 5.5 \text{ V}, 1.8 \text{ V} \le \text{AV}\text{ReF0} \le \text{Vdd}, 1.8 \text{ V} \le \text{AV}\text{ReF1} \le \text{Vdd}, \text{Vss} = \text{EV}\text{ss0} = \text{EV}\text{ss1} = \text{AV}\text{ss} = 0 \text{ V})$

| Parameter | Symbol     | Conditions                                    |                                               |                          | MIN. | TYP. | MAX. | Unit |

|-----------|------------|-----------------------------------------------|-----------------------------------------------|--------------------------|------|------|------|------|

| Supply    | DD1 Note 1 | Operating                                     | fsuв = 32.768 kHz <sup>Note 2</sup> ,         | $V_{DD} = 5.0 V$         |      | 6.4  | 36.0 | μA   |

| current   |            | mode                                          | $T_{A} = -40 \text{ to } +70^{\circ}\text{C}$ | $V_{DD} = 3.0 V$         |      | 6.4  | 36.0 | μA   |

|           |            |                                               |                                               | V <sub>DD</sub> = 2.0 V  |      | 6.3  | 32.8 | μA   |

|           |            |                                               | fsuв = 32.768 kHz <sup>Note 2</sup> ,         | $V_{DD} = 5.0 \text{ V}$ |      | 6.4  | 51.0 | μA   |

|           |            | $T_{A} = -40 \text{ to } +85^{\circ}\text{C}$ | $V_{DD} = 3.0 V$                              |                          | 6.4  | 51.0 | μA   |      |

|           |            |                                               |                                               | V <sub>DD</sub> = 2.0 V  |      | 6.3  | 47.8 | μA   |

- **Notes 1.** Total current flowing into V<sub>DD</sub>, EV<sub>DD0</sub>, EV<sub>DD1</sub>, AV<sub>REF0</sub>, and AV<sub>REF1</sub>, including the input leakage current flowing when the level of the input pin is fixed to V<sub>DD</sub> or V<sub>SS</sub>. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, D/A converter, LVI circuit, I/O port, and on-chip pull-up/pull-down resistors.

- **2.** When internal high-speed oscillator and high-speed system clock are stopped. When watchdog timer is stopped.

Remarks 1. fsuB: Subsystem clock frequency (XT1 clock oscillation frequency)

**2.** Temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

(3) Serial interface: Serial array unit (6/18)

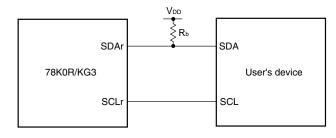

#### Simplified I<sup>2</sup>C mode connection diagram (during communication at same potential)

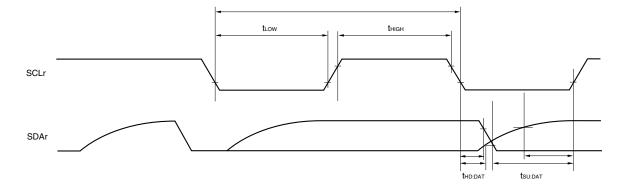

# Simplified I<sup>2</sup>C mode serial transfer timing (during communication at same potential)

Caution Select the normal input buffer and the N-ch open-drain output (VDD tolerance) mode for SDAr and the normal output mode for SCLr by using the PIMg and POMg registers.

**Remarks 1.**  $R_b[\Omega]$ : Communication line (SDAr) pull-up resistance,

Cb[F]: Communication line (SCLr, SDAr) load capacitance

- **2.** r: IIC number (r = 10, 20), g: PIM and POM number (g = 0, 14)

- 3. fmck: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of the SMRmn register. m: Unit number (m = 0, 1), n: Channel number (n = 0, 2), mn = 02, 10)

# (3) Serial interface: Serial array unit (17/18)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, \text{ V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS} = 0 \text{ V})$

| Parameter                     | Symbol  | Conditions                                                                                                                                                           | MIN.         | MAX.                | Unit |

|-------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------|

| SCLr clock frequency          | fsc∟    | $ \begin{aligned} &4.0 \; V \leq V_{DD} \leq 5.5 \; V, \\ &2.7 \; V \leq V_b \leq 4.0 \; V, \\ &C_b = 100 \; pF, \; R_b = 1.4 \; k\Omega \end{aligned} $             |              | 400 <sup>Note</sup> | kHz  |

|                               |         | $\label{eq:VDD} \begin{split} & 2.7 \; V \leq V_{DD} \leq 4.0 \; V, \\ & 2.3 \; V \leq V_b \leq 2.7 \; V, \\ & C_b = 100 \; pF, \; R_b = 2.7 \; k\Omega \end{split}$ |              | 400 <sup>Note</sup> | kHz  |

| Hold time when SCLr = "L"     | tLOW    | $ \begin{aligned} &4.0 \; V \leq V_{DD} \leq 5.5 \; V, \\ &2.7 \; V \leq V_b \leq 4.0 \; V, \\ &C_b = 100 \; pF, \; R_b = 1.4 \; k\Omega \end{aligned} $             | 1065         |                     | ns   |

|                               |         | $\label{eq:VDD} \begin{split} & 2.7 \; V \leq V_{DD} \leq 4.0 \; V, \\ & 2.3 \; V \leq V_b \leq 2.7 \; V, \\ & C_b = 100 \; pF, \; R_b = 2.7 \; k\Omega \end{split}$ | 1065         |                     | ns   |

| Hold time when SCLr = "H"     | tнівн   | $ \begin{array}{l} 4.0 \; V \leq V_{DD} \leq 5.5 \; V, \\ 2.7 \; V \leq V_b \leq 4.0 \; V, \\ C_b = 100 \; pF, \; R_b = 1.4 \; k\Omega \end{array} $                 | 445          |                     | ns   |

|                               |         | $\label{eq:VDD} \begin{split} & 2.7 \; V \leq V_{DD} \leq 4.0 \; V, \\ & 2.3 \; V \leq V_b \leq 2.7 \; V, \\ & C_b = 100 \; pF, \; R_b = 2.7 \; k\Omega \end{split}$ | 445          |                     | ns   |

| Data setup time (reception)   | tsu:dat | $ \begin{aligned} &4.0 \ V \leq V_{DD} \leq 5.5 \ V, \\ &2.7 \ V \leq V_b \leq 4.0 \ V, \\ &C_b = 100 \ pF, \ R_b = 1.4 \ k\Omega \end{aligned} $                    | 1/fмск + 190 |                     | ns   |

|                               |         | $\label{eq:VDD} \begin{array}{l} 2.7 \; V \leq V_{DD} \leq 4.0 \; V, \\ 2.3 \; V \leq V_b \leq 2.7 \; V, \\ C_b = 100 \; pF, \; R_b = 2.7 \; k\Omega \end{array}$    | 1/fмск + 190 |                     | ns   |

| Data hold time (transmission) | thd:dat | $ \begin{aligned} & 4.0 \; V \leq V_{DD} \leq 5.5 \; V, \\ & 2.7 \; V \leq V_b \leq 4.0 \; V, \\ & C_b = 100 \; pF, \; R_b = 1.4 \; k\Omega \end{aligned} $          | 0            | 160                 | ns   |

|                               |         | $\label{eq:VDD} \begin{array}{l} 2.7 \; V \leq V_{DD} \leq 4.0 \; V, \\ 2.3 \; V \leq V_b \leq 2.7 \; V, \\ C_b = 100 \; pF, \; R_b = 2.7 \; k\Omega \end{array}$    | 0            | 160                 | ns   |

#### (h) During communication at different potential (2.5 V, 3 V) (simplified I<sup>2</sup>C mode)

<R> Note The value must also be fmck/4 or less.

# Caution Select the TTL input buffer and the N-ch open-drain output (VDD tolerance) mode for SDAr and the N-ch open-drain output (VDD tolerance) mode for SCLr by using the PIMg and POMg registers.

**Remarks 1.**  $R_b[\Omega]$ : Communication line (SDAr, SCLr) pull-up resistance,

Cb[F]: Communication line (SDAr, SCLr) load capacitance, Vb[V]: Communication line voltage

- **2.** r: IIC number (r = 10, 20), g: PIM, POM number (g = 0, 14)

- 3. fmck: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of the SMRmn register. m: Unit number (m = 0, 1), n: Channel number (n = 0, 2), mn = 02, 10)

**4.** V<sub>IH</sub> and V<sub>IL</sub> below are observation points for the AC characteristics of the serial array unit when communicating at different potentials in simplified I<sup>2</sup>C mode.

4.0 V  $\leq$  V\_{\text{DD}}  $\leq$  5.5 V, 2.7 V  $\leq$  V\_{\text{b}}  $\leq$  4.0 V: VIH = 2.2 V, VIL = 0.8 V

$2.7~V \leq V_{\text{DD}} \leq 4.0~V,~2.3~V \leq V_{\text{b}} \leq 2.7~V;~V_{\text{IH}} = 2.0~V,~V_{\text{IL}} = 0.5~V$

# A.1 Software Package

| SP78K0R                       | Development tools (software) common to the 78K0R microcontrollers are combined in |

|-------------------------------|-----------------------------------------------------------------------------------|

| 78K0R Series software package | this package.                                                                     |

|                               | Part number: $\mu$ S××××SP78K0R                                                   |

Remark xxxx in the part number differs depending on the host machine and OS used.

#### $\mu S \times \times \times S P78 K0 R$

| **** | Host Machine          | OS                         | Supply Medium |

|------|-----------------------|----------------------------|---------------|

| AB17 | PC-9800 series,       | Windows (Japanese version) | CD-ROM        |

| BB17 | IBM PC/AT compatibles | Windows (English version)  |               |

# A.2 Language Processing Software

| RA78K0R<br>Assembler package            | This assembler converts programs written in mnemonics into object codes executable with a microcontroller.<br>This assembler is also provided with functions capable of automatically creating symbol tables and branch instruction optimization.<br>This assembler should be used in combination with a device file (DF781188).<br>< <b>Precaution when using RA78K0R in PC environment&gt;</b><br>This assembler package is a DOS-based application. It can also be used in Windows, however, by using the Project Manager (included in assembler package) on Windows. |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | Part number: µS××××RA78K0R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CC78K0R<br>C compiler package           | This compiler converts programs written in C language into object codes executable with a microcontroller.<br>This compiler should be used in combination with an assembler package and device file (both sold separately).<br><precaution cc78k0r="" environment="" in="" pc="" using="" when=""><br/>This C compiler package is a DOS-based application. It can also be used in Windows, however, by using the Project Manager (included in assembler package) on Windows.</precaution>                                                                                |

|                                         | Part number: µS××××CC78K0R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DF781188 <sup>Note</sup><br>Device file | This file contains information peculiar to the device.<br>This device file should be used in combination with a tool (RA78K0R, CC78K0R, SM+ for 78K0R, and ID78K0R-QB) (all sold separately).<br>The corresponding OS and host machine differ depending on the tool to be used.                                                                                                                                                                                                                                                                                          |

|                                         | Part number: µS××××DF781188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Note The DF781188 can be used in common with the RA78K0R, CC78K0R, SM+ for 78K0R, and ID78K0R-QB. Download the DF781188 from the download site for development tools (http://www.necel.com/micro/ods/eng/index.html).