#

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 83                                                                                    |

| Program Memory Size        | 256КВ (256К х 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 12K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                  |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 100-LQFP                                                                              |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1166agc-ueu-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Special Function Register (SFR) Name          | Symbol                                   |      | Symbol |              | R/W          | Manipulable Bit Range |       | Range | After Reset |

|---------|-----------------------------------------------|------------------------------------------|------|--------|--------------|--------------|-----------------------|-------|-------|-------------|

|         |                                               |                                          |      |        | 1-bit        | 8-bit        | 16-bit                |       |       |             |

| FFFEEH  | Priority specification flag register 11L      | PR11L                                    | PR11 | R/W    | $\checkmark$ | $\checkmark$ |                       | FFH   |       |             |

| FFFEFH  | Priority specification flag register 11H      | PR11H                                    |      | R/W    | $\checkmark$ | $\checkmark$ |                       | FFH   |       |             |

| FFFF0H  | Multiplication input data register A          | MULA                                     |      | R/W    | -            | -            |                       | 0000H |       |             |

| FFFF1H  |                                               |                                          |      |        |              |              |                       |       |       |             |

| FFFF2H  | Multiplication input data register B          | ultiplication input data register B MULB |      | R/W    | -            | -            | $\checkmark$          | 0000H |       |             |

| FFFF3H  |                                               |                                          |      |        |              |              |                       |       |       |             |

| FFFF4H  | Higher multiplication result storage register | MULOH                                    |      | R      | -            | -            |                       | 0000H |       |             |

| FFFF5H  |                                               |                                          |      |        |              |              |                       |       |       |             |

| FFFF6H  | Lower multiplication result storage register  |                                          |      | R      | -            | -            |                       | 0000H |       |             |

| FFFF7H  |                                               |                                          |      |        |              |              |                       |       |       |             |

| FFFFEH  | Processor mode control register               | PMC                                      |      | R/W    | $\checkmark$ | $\checkmark$ | -                     | 00H   |       |             |

| FFFFFH  | Memory extension mode control register        | MEM                                      |      | R/W    | $\checkmark$ | $\checkmark$ | -                     | 00H   |       |             |

Table 3-5. SFR List (5/5)

Remark For extended SFRs (2nd SFRs), see Table 3-6 Extended SFR (2nd SFR) List.

| Address | Special Function Register (SFR) Name               | Syn    | nbol  | R/W | Manipu       | After Reset  |              |       |

|---------|----------------------------------------------------|--------|-------|-----|--------------|--------------|--------------|-------|

|         |                                                    |        |       |     | 1-bit        | 8-bit        | 16-bit       |       |

| F014CH  | Serial flag clear trigger register 12              | SIR12L | SIR12 | R/W | -            |              | $\checkmark$ | 0000H |

| F014DH  |                                                    | _      |       |     | -            | -            |              |       |

| F014EH  | Serial flag clear trigger register 13              | SIR13L | SIR13 | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H |

| F014FH  |                                                    | -      |       |     | -            | -            |              |       |

| F0150H  | Serial mode register 10                            | SMR10  |       | R/W | -            | -            | $\checkmark$ | 0020H |

| F0151H  |                                                    |        |       |     |              |              |              |       |

| F0152H  | Serial mode register 11                            | SMR11  |       | R/W | -            | -            | $\checkmark$ | 0020H |

| F0153H  |                                                    |        |       |     |              |              |              |       |

| F0154H  | Serial mode register 12                            | SMR12  |       | R/W | -            | -            | $\checkmark$ | 0020H |

| F0155H  |                                                    |        |       |     |              |              |              |       |

| F0156H  | Serial mode register 13                            | SMR13  |       | R/W | _            | -            | $\checkmark$ | 0020H |

| F0157H  |                                                    |        |       |     |              |              |              |       |

| F0158H  | Serial communication operation setting register 10 |        | R/W   | -   | -            | $\checkmark$ | 0087H        |       |

| F0159H  |                                                    |        |       |     |              |              |              |       |

| F015AH  | Serial communication operation setting register 11 | SCR11  |       | R/W | -            | -            | $\checkmark$ | 0087H |

| F015BH  |                                                    |        |       |     |              |              |              |       |

| F015CH  | Serial communication operation setting register 12 | SCR12  |       | R/W | -            | -            | $\checkmark$ | 0087H |

| F015DH  |                                                    |        |       |     |              |              |              |       |

| F015EH  | Serial communication operation setting register 13 | SCR13  |       | R/W | -            | -            | $\checkmark$ | 0087H |

| F015FH  |                                                    |        |       |     |              |              |              |       |

| F0160H  | Serial channel enable status register 1            | SE1L   | SE1   | R   | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H |

| F0161H  |                                                    | -      |       |     | -            | -            |              |       |

| F0162H  | Serial channel start register 1                    | SS1L   | SS1   | R/W | $\checkmark$ |              | $\checkmark$ | 0000H |

| F0163H  |                                                    | -      |       |     | _            | _            |              |       |

| F0164H  | Serial channel stop register 1                     | ST1L   | ST1   | R/W | $\checkmark$ |              | $\checkmark$ | 0000H |

| F0165H  |                                                    | -      |       |     | -            | -            |              |       |

| F0166H  | Serial clock select register 1                     | SPS1L  | SPS1  | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H |

| F0167H  |                                                    | -      |       |     | -            | -            |              |       |

| F0168H  | Serial output register 1                           | SO1    |       | R/W | -            | -            | $\checkmark$ | 0F0FH |

| F0169H  |                                                    |        |       |     |              |              |              |       |

| F016AH  | Serial output enable register 1                    | SOE1L  | SOE1L | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H |

| F016BH  |                                                    | -      |       |     | -            | -            |              |       |

| F0174H  | Serial output level register 1                     | SOL1L  | SOL1L | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H |

| F0175H  |                                                    |        |       |     | -            | -            |              |       |

| F0180H  | Timer counter register 00                          | TCR00  |       | R   | -            | -            | $\checkmark$ | FFFFH |

| F0181H  |                                                    |        |       |     |              |              |              |       |

| F0182H  | Timer counter register 01                          | TCR01  |       | R   | -            | -            | $\checkmark$ | FFFFH |

| F0183H  |                                                    |        |       |     |              |              |              |       |

| F0184H  | Timer counter register 02                          | TCR02  |       | R   | -            | -            | $\checkmark$ | FFFFH |

| F0185H  |                                                    |        |       |     |              |              |              |       |

| F0186H  | Timer counter register 03                          | TCR03  |       | R   | -            | -            | $\checkmark$ | FFFFH |

| F0187H  |                                                    |        |       |     |              |              |              |       |

# Table 3-6. Extended SFR (2nd SFR) List (3/5)

#### 11.5.2 Registers used by temperature sensors

The following four types of registers are used when using a temperature sensor.

- Peripheral enable register 0 (PER0)

- A/D converter mode register (ADM)

- Analog input channel specification register (ADS)

- 10-bit A/D conversion result register (ADCR)

Caution Setting of the A/D port configuration register (ADPC), port mode register 2 (PM2) and port register 2 (P2) is not required when using the temperature sensor. There is no problem if the pin function is set as digital I/O.

#### (1) Peripheral enable register 0 (PER0)

Use the PER0 register in the same manner as during A/D converter basic operation (see **11.3 (1) Peripheral** enable register 0 (PER0)).

#### (2) A/D converter mode register (ADM)

Use the ADM register in the same manner as during A/D converter basic operation (see **11.3 (2)** A/D converter mode register (ADM)).

However, selection of the A/D conversion time when a temperature sensor is used varies as shown in Table 11-5.

| A/D Co | onverter                            | Mode F | Register | (ADM) |                  | Conversio          | on Time Selection  |                    | Conversion Clock |

|--------|-------------------------------------|--------|----------|-------|------------------|--------------------|--------------------|--------------------|------------------|

| FR2    | FR1                                 | FR0    | LV1      | LV0   |                  | fclк = 2 MHz       | fclк = 8 MHz       | fclк = 20 MHz      | (fad)            |

| 0      | 0                                   | 0      | 0        | 1     | <b>480/f</b> ськ | Setting prohibited | 60.0 <i>µ</i> s    | 24.0 <i>µ</i> s    | fclк/12          |

| 0      | 0                                   | 1      | 0        | 1     | <b>320/f</b> ськ |                    | 40.0 <i>µ</i> s    | Setting prohibited | fclk/8           |

| 0      | 1                                   | 0      | 0        | 1     | 240/fclк         |                    | 30.0 <i>µ</i> s    |                    | fclk/6           |

| 0      | 1                                   | 1      | 0        | 1     | 160/fclк         |                    | Setting prohibited |                    | fclk/4           |

| 1      | 0                                   | 0      | 0        | 1     | 120/fclк         | 60.0 <i>µ</i> s    |                    |                    | fclk/3           |

| 1      | 0                                   | 1      | 0        | 1     | <b>80/f</b> ськ  | 40.0 <i>µ</i> s    |                    |                    | fclk/2           |

| 1      | 1                                   | 1      | 0        | 1     | <b>40/f</b> ськ  | Setting prohibited |                    |                    | fclĸ             |

|        | Other than above Setting prohibited |        |          |       |                  |                    |                    |                    |                  |

#### Table 11-5. Selection of A/D Conversion Time When Using Temperature Sensor

(1) 2.7 V  $\leq$  AV<sub>REF0</sub>  $\leq$  5.5 V

Cautions 1. Set the conversion times so as to satisfy the following condition.

fad = 0.6 to 1.8 MHz

- 2. When rewriting FR2 to FR0, LV1, and LV0 to other than the same data, stop A/D conversion (ADCS = 0) beforehand.

- 3. The above conversion time does not include clock frequency errors. Select conversion time, taking clock frequency errors into consideration.

**Remark** fclk: CPU/peripheral hardware clock frequency

#### (9) Serial channel start register m (SSm)

SSm is a trigger register that is used to enable starting communication/count by each channel. When 1 is written a bit of this register (SSmn), the corresponding bit (SEmn) of serial channel enable status register m (SEm) is set to 1. Because SSmn is a trigger bit, it is cleared immediately when SEmn = 1. SSm can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of SSm can be set with an 1-bit or 8-bit memory manipulation instruction with SSmL. Reset signal generation clears this register to 0000H.

#### Figure 13-12. Format of Serial Channel Start Register m (SSm)

Address: F0122H, F0123H (SS0), F0162H, F0163H (SS1) After reset: 0000H R/W

| Symbol | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3        | 2        | 1        | 0        |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|----------|----------|----------|----------|

| SSm    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | SSm<br>3 | SSm<br>2 | SSm<br>1 | SSm<br>0 |

| SSmn | Operation start trigger of channel n                                                                                                                                            |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | No trigger operation                                                                                                                                                            |

| 1    | Sets SEmn to 1 and enters the communication wait status (if a communication operation is already under execution, the operation is stopped and the start condition is awaited). |

#### Caution Be sure to clear bits 15 to 4 to "0".

**Remarks 1.** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3)

2. When the SSm register is read, 0000H is always read.

(3) Processing flow (in single-reception mode)

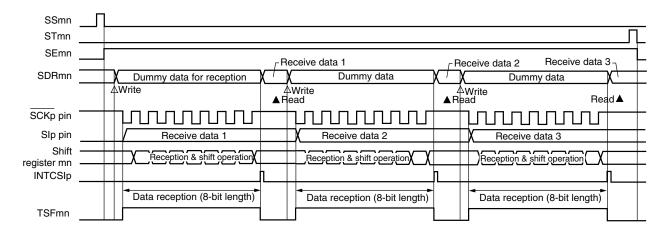

Figure 13-36. Timing Chart of Master Reception (in Single-Reception Mode) (Type 1: DAPmn = 0, CKPmn = 0)

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2), p: CSI number (p = 00, 01, 10, 20)

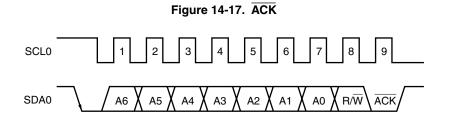

When the local address is received,  $\overline{ACK}$  is automatically generated, regardless of the value of ACKE0. When an address other than that of the local address is received,  $\overline{ACK}$  is not generated (NACK).

When an extension code is received, ACK is generated if ACKE0 is set to 1 in advance.

How ACK is generated when data is received differs as follows depending on the setting of the wait timing.

- When 8-clock wait state is selected (bit 3 (WTIM0) of IICC0 register = 0): By setting ACKE0 to 1 before releasing the wait state, ACK is generated at the falling edge of the eighth clock of the SCL0 pin.

- When 9-clock wait state is selected (bit 3 (WTIM0) of IICC0 register = 1): ACK is generated by setting ACKE0 to 1 in advance.

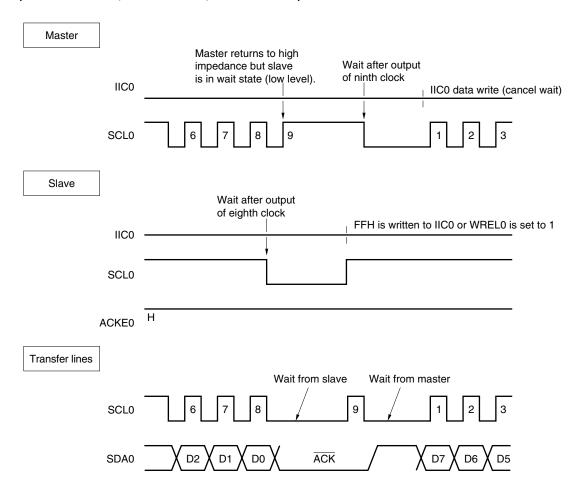

#### 14.5.7 Wait

The wait is used to notify the communication partner that a device (master or slave) is preparing to transmit or receive data (i.e., is in a wait state).

Setting the SCL0 pin to low level notifies the communication partner of the wait state. When wait state has been canceled for both the master and slave devices, the next data transfer can begin.

#### Figure 14-19. Wait (1/2)

(1) When master device has a nine-clock wait and slave device has an eight-clock wait (master transmits, slave receives, and ACKE0 = 1)

#### Figure 17-2. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H, IF2L, IF2H) (2/2)

| Address: FFI | -D1H After | reset: 00H | R/W |   |   |   |   |

|--------------|------------|------------|-----|---|---|---|---|

| Symbol       | 7          | 6          | 5   | 4 | 3 | 2 | 1 |

| IF2H         | 0          | 0          | 0   | 0 | 0 | 0 | 0 |

| XXIFX | Interrupt request flag                                   |  |  |  |  |  |

|-------|----------------------------------------------------------|--|--|--|--|--|

| 0     | No interrupt request signal is generated                 |  |  |  |  |  |

| 1     | Interrupt request is generated, interrupt request status |  |  |  |  |  |

#### Cautions 1. Be sure to clear bits 1 to 7 of IF2H to 0.

4

- 2. When operating a timer, serial interface, or A/D converter after standby release, operate it once after clearing the interrupt request flag. An interrupt request flag may be set by noise.

- 3. When manipulating a flag of the interrupt request flag register, use a 1-bit memory manipulation instruction (CLR1). When describing in C language, use a bit manipulation instruction such as "IF0L.0 = 0;" or "\_asm("clr1 IF0L, 0");" because the compiled assembler must be a 1-bit memory manipulation instruction (CLR1).

If a program is described in C language using an 8-bit memory manipulation instruction such as "IF0L &= 0xfe;" and compiled, it becomes the assembler of three instructions. mov a, IF0L and a, #0FEH mov IF0L, a

In this case, even if the request flag of another bit of the same interrupt request flag register (IF0L) is set to 1 at the timing between "mov a, IF0L" and "mov IF0L, a", the flag is cleared to 0 at "mov IF0L, a". Therefore, care must be exercised when using an 8-bit memory manipulation instruction in C language.

#### (2) Interrupt mask flag registers (MK0L, MK0H, MK1L, MK1H, MK2L, MK2H)

The interrupt mask flags are used to enable/disable the corresponding maskable interrupt servicing. MK0L, MK0H, MK1L, MK1H, MK2L, and MK2H can be set by a 1-bit or 8-bit memory manipulation instruction. When MK0L and MK0H, MK1L and MK1H, and MK2L and MK2H are combined to form 16-bit registers MK0, MK1, and MK2, they can be set by a 16-bit memory manipulation instruction. Reset signal generation sets these registers to FFH.

# **Remark** If an instruction that writes data to this register is executed, the number of instruction execution clocks increases by 2 clocks.

<0> PIF11

|                                       | Hardware                                                                                                                                 | Status After Reset<br>Acknowledgment <sup>Note 1</sup> |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Real-time counter                     | Subcount register (RSUBC)                                                                                                                | 0000H                                                  |

|                                       | Second count register (SEC)                                                                                                              | 00H                                                    |

|                                       | Minute count register (MIN)                                                                                                              | 00H                                                    |

|                                       | Hour count register (HOUR)                                                                                                               | 12H                                                    |

|                                       | Day count register (DAY)                                                                                                                 | 01H                                                    |

|                                       | Week count register (WEEK)                                                                                                               | 00H                                                    |

|                                       | Month count register (MONTH)                                                                                                             | 01H                                                    |

|                                       | Year count register (YEAR)                                                                                                               | 00H                                                    |

|                                       | Watch error correction register (SUBCUD)                                                                                                 | 00H                                                    |

|                                       | Alarm minute register (ALARMWM)                                                                                                          | 00H                                                    |

|                                       | Alarm hour register (ALARMWH)                                                                                                            | 12H                                                    |

|                                       | Alarm week register ALARMWW)                                                                                                             | 00H                                                    |

|                                       | Real-time counter control register 0 (RTCC0)                                                                                             | 00H                                                    |

|                                       | Real-time counter control register 1 (RTCC1)                                                                                             | 00H                                                    |

|                                       | Real-time counter control register 2 (RTCC2)                                                                                             | 00H                                                    |

| Clock output/buzzer output controller | Clock output select registers 0, 1 (CKS0, CKS1)                                                                                          | 00H                                                    |

| Watchdog timer                        | Enable register (WDTE)                                                                                                                   | 1AH/9AH <sup>Note 2</sup>                              |

| A/D converter                         | 10-bit A/D conversion result register (ADCR)                                                                                             | 0000H                                                  |

|                                       | 8-bit A/D conversion result register (ADCRH)                                                                                             | 00H                                                    |

|                                       | Mode register (ADM)                                                                                                                      | 00H                                                    |

|                                       | Analog input channel specification register (ADS)                                                                                        | 00H                                                    |

|                                       | A/D port configuration register (ADPC)                                                                                                   | 10H                                                    |

| D/A converter                         | 8-bit D/A conversion value setting registers 0, 1 (DACS0, DACS1)                                                                         | 00H                                                    |

|                                       | D/A converter mode register (DAM)                                                                                                        | 00H                                                    |

| Serial array unit (SAU)               | Serial data registers 00, 01, 02, 03, 10, 11, 12, 13 (SDR00, SDR01, SDR02, SDR03, SDR10, SDR11, SDR12, SDR13)                            | 0000H                                                  |

|                                       | Serial status registers 00, 01, 02, 03, 10, 11, 12, 13 (SSR00, SSR01, SSR02, SSR03, SSR10, SSR11, SSR12, SSR13)                          | 0000H                                                  |

|                                       | Serial flag clear trigger registers 00, 01, 02, 03, 10, 11, 12, 13 (SIR00, SIR01, SIR02, SIR03, SIR10, SIR11, SIR12, SIR13)              | 0000H                                                  |

|                                       | Serial mode registers 00, 01, 02, 03, 10, 11, 12, 13 (SMR00, SMR01, SMR02, SMR03, SMR10, SMR11, SMR12, SMR13)                            | 0020H                                                  |

|                                       | Serial communication operation setting registers 00, 01, 02, 03, 10, 11, 12, 13 (SCR00, SCR01, SCR02, SCR03, SCR10, SCR11, SCR12, SCR13) | 0087H                                                  |

|                                       | Serial channel enable status registers 0, 1 (SE0, SE1)                                                                                   | 0000H                                                  |

|                                       | Serial channel start registers 0, 1 (SS0, SS1)                                                                                           | 0000H                                                  |

|                                       | Serial channel stop registers 0, 1 (ST0, ST1)                                                                                            | 0000H                                                  |

|                                       | Serial clock select registers 0, 1 (SPS0, SPS1)                                                                                          | 0000H                                                  |

|                                       | Serial output registers 0, 1 (SO0, SO1)                                                                                                  | 0F0FH                                                  |

|                                       | Serial output registers 0, 1 (SO0, SO1)                                                                                                  | 0000H                                                  |

|                                       | Serial output level registers 0, 1 (SOL0, SOL1)                                                                                          | 0000H                                                  |

|                                       | Input switch control register (ISC)                                                                                                      | 00H                                                    |

| Table 20-2. | <b>Hardware Statuses</b> | After Reset | Acknowledg | ament ( | 2/3) |

|-------------|--------------------------|-------------|------------|---------|------|

|             |                          |             |            |         |      |

**Notes 1.** During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware statuses become undefined. All other hardware statuses remain unchanged after reset.

2. The reset value of WDTE is determined by the option byte setting.

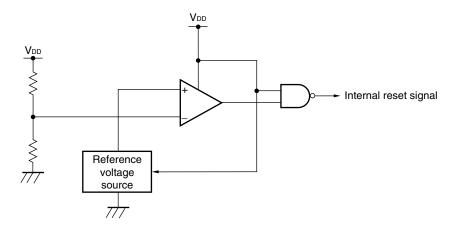

# 21.2 Configuration of Power-on-Clear Circuit

The block diagram of the power-on-clear circuit is shown in Figure 21-1.

#### 21.3 Operation of Power-on-Clear Circuit

An internal reset signal is generated on power application. When the supply voltage (V<sub>DD</sub>) exceeds the detection voltage (V<sub>POC</sub> = 1.59 V ±0.09 V), the reset status is released.

# Caution If the low-voltage detector (LVI) is set to ON by an option byte by default, the reset signal is not released until the supply voltage (V<sub>DD</sub>) exceeds 2.07 V ±0.2 V.

• The supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>POC</sub> = 1.59 V ±0.09 V) are compared. When V<sub>DD</sub> < V<sub>POC</sub>, the internal reset signal is generated.

The timing of generation of the internal reset signal by the power-on-clear circuit and low-voltage detector is shown below.

- (2) When detecting level of input voltage from external input pin (EXLVI)

- When starting operation

- <1> Mask the LVI interrupt (LVIMK = 1).

- <2> Set bit 2 (LVISEL) of the low-voltage detection register (LVIM) to 1 (detects level of input voltage from external input pin (EXLVI)).

- Clear bit 1 (LVIMD) of LVIM to 0 (generates interrupt signal when the level is detected) (default value).

- <3> Set bit 7 (LVION) of LVIM to 1 (enables LVI operation).

- <4> Use software to wait for the following periods of time (Total 410  $\mu$ s).

- Operation stabilization time (10 µs (MAX.))

- Minimum pulse width (200 µs (MIN.))

- Detection delay time (200 µs (MAX.))

- <5> Confirm that "input voltage from external input pin (EXLVI) ≥ detection voltage (VEXLVI = 1.21 V (TYP.))" when detecting the falling edge of EXLVI, or "input voltage from external input pin (EXLVI) < detection voltage (VEXLVI = 1.21 V (TYP.))" when detecting the rising edge of EXLVI, at bit 0 (LVIF) of LVIM.</p>

- <6> Clear the interrupt request flag of LVI (LVIIF) to 0.

- <7> Release the interrupt mask flag of LVI (LVIMK).

- <8> Execute the EI instruction (when vector interrupts are used).

Figure 22-10 shows the timing of the interrupt signal generated by the low-voltage detector. The numbers in this timing chart correspond to <1> to <7> above.

#### Caution The input voltage from the external input pin (EXLVI) must be EXLVI < $V_{DD}$ .

- When stopping operation Either of the following procedures must be executed.

- When using 8-bit memory manipulation instruction: Write 00H to LVIM.

- When using 1-bit memory manipulation instruction: Clear LVION to 0.

| Instruction | Mnemonic        | Operands           | Bytes | Clo    | ocks                              | Operation                               |   | Flag | J  |

|-------------|-----------------|--------------------|-------|--------|-----------------------------------|-----------------------------------------|---|------|----|

| Group       |                 |                    |       | Note 1 | Note 2                            |                                         | Z | AC   | CY |

| 16-bit      | MOVW            | AX, ES:[HL + byte] | 3     | 2      | 5                                 | $AX \leftarrow ((ES, HL) + byte)$       |   |      | -  |

| data        |                 | ES:[HL + byte], AX | 3     | 2      | -                                 | $((ES, HL) + byte) \leftarrow AX$       |   |      |    |

| transfer    |                 | AX, ES:word[B]     | 4     | 2      | 5                                 | $AX \leftarrow ((ES, B) + word)$        |   |      |    |

|             |                 | ES:word[B], AX     | 4     | 2      | -                                 | $((ES,B) + word) \leftarrow AX$         |   |      |    |

|             |                 | AX, ES:word[C]     | 4     | 2      | 5                                 | $AX \leftarrow ((ES, C) + word)$        |   |      |    |

|             | ES:word[C], AX  | 4                  | 2     | -      | $((ES,C) + word) \leftarrow AX$   |                                         |   |      |    |

|             | AX, ES:word[BC] | 4                  | 2     | 5      | $AX \leftarrow ((ES, BC) + word)$ |                                         |   |      |    |

|             |                 | ES:word[BC], AX    | 4     | 2      | -                                 | $((ES, BC) + word) \leftarrow AX$       |   |      |    |

|             |                 | BC, ES:!addr16     | 4     | 2      | 5                                 | $BC \leftarrow (ES, addr16)$            |   |      |    |

|             |                 | DE, ES:laddr16     | 4     | 2      | 5                                 | $DE \leftarrow (ES, addr16)$            |   |      |    |

|             |                 | HL, ES:!addr16     | 4     | 2      | 5                                 | $HL \leftarrow (ES, addr16)$            |   |      |    |

|             | XCHW            | AX, rp Note 3      | 1     | 1      | -                                 | $AX \leftarrow \rightarrow rp$          |   |      |    |

|             | ONEW            | AX                 | 1     | 1      | -                                 | AX ← 0001H                              |   |      |    |

|             |                 | BC                 | 1     | 1      | -                                 | BC ← 0001H                              |   |      |    |

|             | CLRW            | AX                 | 1     | 1      | -                                 | AX ← 0000H                              |   |      |    |

|             |                 | BC                 | 1     | 1      | -                                 | BC ← 0000H                              |   |      |    |

| 8-bit       | ADD             | A, #byte           | 2     | 1      | -                                 | A, CY $\leftarrow$ A + byte             | × | ×    | ×  |

| operation   |                 | saddr, #byte       | 3     | 2      | -                                 | (saddr), CY $\leftarrow$ (saddr) + byte | × | ×    | ×  |

|             |                 | A, r               | 2     | 1      | -                                 | A, CY $\leftarrow$ A + r                | × | ×    | ×  |

|             |                 | r, A               | 2     | 1      | -                                 | r, CY ← r + A                           | × | ×    | ×  |

|             |                 | A, saddr           | 2     | 1      | -                                 | A, CY $\leftarrow$ A + (saddr)          | × | ×    | ×  |

|             |                 | A, !addr16         | 3     | 1      | 4                                 | A, CY $\leftarrow$ A + (addr16)         | × | ×    | ×  |

|             |                 | A, [HL]            | 1     | 1      | 4                                 | A, CY $\leftarrow$ A + (HL)             | × | ×    | ×  |

|             |                 | A, [HL + byte]     | 2     | 1      | 4                                 | A, CY $\leftarrow$ A + (HL + byte)      | × | ×    | ×  |

|             |                 | A, [HL + B]        | 2     | 1      | 4                                 | A, CY $\leftarrow$ A + (HL + B)         | × | ×    | ×  |

|             |                 | A, [HL + C]        | 2     | 1      | 4                                 | $A, CY \leftarrow A + (HL + C)$         | × | ×    | ×  |

|             |                 | A, ES:!addr16      | 4     | 2      | 5                                 | A, CY $\leftarrow$ A + (ES, addr16)     | × | ×    | ×  |

|             |                 | A, ES:[HL]         | 2     | 2      | 5                                 | $A,CY \leftarrow A + (ES,HL)$           | × | ×    | ×  |

|             |                 | A, ES:[HL + byte]  | 3     | 2      | 5                                 | $A,CY \leftarrow A + ((ES, HL) + byte)$ | × | ×    | ×  |

|             |                 | A, ES:[HL + B]     | 3     | 2      | 5                                 | $A,CY \leftarrow A + ((ES,HL) + B)$     | × | ×    | ×  |

|             |                 | A, ES:[HL + C]     | 3     | 2      | 5                                 | $A,CY \leftarrow A + ((ES, HL) + C)$    | × | ×    | ×  |

| Table 28-5. | Operation | List (6/17) |

|-------------|-----------|-------------|

|-------------|-----------|-------------|

Notes 1. When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

2. When the program memory area is accessed.

**3.** Except rp = AX

4. Except r = A

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the system clock control register (CKC).

- 2. This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum (except when branching to the external memory area).

- 3. In products where the external memory area is adjacent to the internal flash area, the number of waits is added to the number of instruction execution clocks placed in the last address (16-byte max.) in the flash memory, in order to use the external bus interface function. This should be done because, during prereading of the instruction code, an external memory wait being inserted due to an external memory area exceeding the flash space is accessed. For the number of waits, refer to 5.4 Number of Instruction Wait Clocks for Data Access.

| Instruction | Mnemonic | Operands          | Bytes | Clo    | ocks   | Operation                                    |   | Flag | ļ  |

|-------------|----------|-------------------|-------|--------|--------|----------------------------------------------|---|------|----|

| Group       |          |                   |       | Note 1 | Note 2 |                                              | Z | AC   | CY |

| 8-bit       | SUBC     | A, #byte          | 2     | 1      | -      | A, CY $\leftarrow$ A – byte – CY             | × | ×    | ×  |

| operation   |          | saddr, #byte      | 3     | 2      | -      | (saddr), CY $\leftarrow$ (saddr) – byte – CY | × | ×    | ×  |

|             |          | A, r              | 2     | 1      | -      | A, CY $\leftarrow$ A – r – CY                | × | ×    | ×  |

|             |          | r, A              | 2     | 1      | -      | $r, CY \leftarrow r - A - CY$                | × | ×    | ×  |

|             |          | A, saddr          | 2     | 1      | _      | A, CY $\leftarrow$ A – (saddr) – CY          | × | ×    | ×  |

|             |          | A, !addr16        | 3     | 1      | 4      | A, CY $\leftarrow$ A – (addr16) – CY         | × | ×    | ×  |

|             |          | A, [HL]           | 1     | 1      | 4      | $A, CY \leftarrow A - (HL) - CY$             | × | ×    | ×  |

|             |          | A, [HL + byte]    | 2     | 1      | 4      | A, CY $\leftarrow$ A – (HL + byte) – CY      | × | ×    | ×  |

|             |          | A, [HL + B]       | 2     | 1      | 4      | $A, CY \leftarrow A - (HL + B) - CY$         | × | ×    | ×  |

|             |          | A, [HL + C]       | 2     | 1      | 4      | $A, CY \leftarrow A - (HL + C) - CY$         | × | ×    | ×  |

|             |          | A, ES:laddr16     | 4     | 2      | 5      | A, CY $\leftarrow$ A – (ES:addr16) – CY      | × | ×    | ×  |

|             |          | A, ES:[HL]        | 2     | 2      | 5      | A, CY $\leftarrow$ A – (ES:HL) – CY          | × | ×    | ×  |

|             |          | A, ES:[HL + byte] | 3     | 2      | 5      | A, CY $\leftarrow$ A – ((ES:HL) + byte) – CY | × | ×    | ×  |

|             |          | A, ES:[HL + B]    | 3     | 2      | 5      | $A, CY \leftarrow A - ((ES:HL) + B) - CY$    | × | ×    | ×  |

|             |          | A, ES:[HL + C]    | 3     | 2      | 5      | $A, CY \leftarrow A - ((ES:HL) + C) - CY$    | × | ×    | ×  |

|             | AND      | A, #byte          | 2     | 1      | -      | $A \leftarrow A \land byte$                  | × |      |    |

|             |          | saddr, #byte      | 3     | 2      | -      | $(saddr) \leftarrow (saddr) \land byte$      | × |      |    |

|             |          | A, r Note 3       | 2     | 1      | -      | $A \leftarrow A \wedge r$                    | × | -    |    |

|             |          | r, A              | 2     | 1      | -      | $r \leftarrow r \land A$                     | × |      |    |

|             |          | A, saddr          | 2     | 1      | -      | $A \leftarrow A \land (saddr)$               | × |      |    |

|             |          | A, !addr16        | 3     | 1      | 4      | $A \leftarrow A \land (addr16)$              | × |      |    |

|             |          | A, [HL]           | 1     | 1      | 4      | $A \leftarrow A \land (HL)$                  | × |      |    |

|             |          | A, [HL + byte]    | 2     | 1      | 4      | $A \leftarrow A \land (HL + byte)$           | × |      |    |

|             |          | A, [HL + B]       | 2     | 1      | 4      | $A \leftarrow A \land (HL + B)$              | × |      |    |

|             |          | A, [HL + C]       | 2     | 1      | 4      | $A \leftarrow A \land (HL + C)$              | × |      |    |

|             |          | A, ES:laddr16     | 4     | 2      | 5      | $A \leftarrow A \land (ES:addr16)$           | × |      |    |

|             |          | A, ES:[HL]        | 2     | 2      | 5      | $A \leftarrow A \land (ES:HL)$               | × |      |    |

|             |          | A, ES:[HL + byte] | 3     | 2      | 5      | $A \leftarrow A \land ((ES:HL) + byte)$      | × |      |    |

|             |          | A, ES:[HL + B]    | 3     | 2      | 5      | $A \leftarrow A \land ((ES:HL) + B)$         | × |      |    |

|             |          | A, ES:[HL + C]    | 3     | 2      | 5      | $A \leftarrow A \land ((ES:HL) + C)$         | × |      |    |

**Notes 1.** When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

2. When the program memory area is accessed.

3. Except r = A

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the system clock control register (CKC).

- **2.** This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum (except when branching to the external memory area).

- 3. In products where the external memory area is adjacent to the internal flash area, the number of waits is added to the number of instruction execution clocks placed in the last address (16-byte max.) in the flash memory, in order to use the external bus interface function. This should be done because, during prereading of the instruction code, an external memory wait being inserted due to an external memory area exceeding the flash space is accessed. For the number of waits, refer to 5.4 Number of Instruction Wait Clocks for Data Access.

Standard Products

# DC Characteristics (7/16)

| $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, 1.8 \text{ V} \le \text{AV}_{\text{REF0}} \le \text{V}_{DD}, 1.8 \text{ V} \le \text{AV}_{\text{REF1}} = \text{AV}_{\text{REF1}} = \text{AV}_{\text{REF1}} = \text{AV}_{\text{REF1}} $ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vss = EVss0 = EVss1 = AVss = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Parameter                                                     | Symbol | Condition                                                                                                                          | ns                      | MIN. | TYP. | MAX. | Unit |

|---------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------|------|------|

| On-chip pull-up<br>resistance                                 | Ru     | P00 to P06, P10 to P17, P30,<br>P31, P40 to P47, P50 to P57,<br>P64 to P67, P70 to P77,<br>P80 to P87, P120, P131,<br>P140 to P145 | Vı = Vss, In input port | 10   | 20   | 100  | kΩ   |

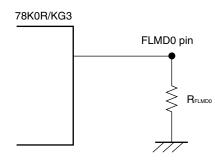

| FLMD0 pin<br>external pull-down<br>resistance <sup>∾ote</sup> | Rflmdo | When enabling the self-programmed software                                                                                         | ning mode setting with  | 100  |      |      | kΩ   |

Note It is recommended to leave the FLMD0 pin open. If the pin is required to be pulled down externally, set  $R_{FLMD0}$  to 100 k $\Omega$  or more.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

Standard Products

### (3) Serial interface: Serial array unit (14/18)

<R>

$(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS} = 0 \text{ V})$

| Parameter                                       | Symbol | C                                                                                              | Conditions                                      | MIN.         | TYP. | MAX.            | Unit |

|-------------------------------------------------|--------|------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------|------|-----------------|------|

| SCKp cycle time                                 | tксү2  | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                                                         | 13.6 MHz < fмск                                 | 10/fмск      |      |                 | ns   |

|                                                 |        | $2.7~V \leq V_b \leq 4.0~V$                                                                    | 6.8 MHz < fмск ≤ 13.6 MHz                       | 8/fмск       |      |                 | ns   |

|                                                 |        |                                                                                                | fмск ≤ 6.8 MHz                                  | 6/fмск       |      |                 | ns   |

|                                                 |        | $2.7~V \leq V_{\text{DD}} < 4.0~V,$                                                            | 18.5 MHz < fмск                                 | 16/fмск      |      |                 | ns   |

|                                                 |        | $2.3~V \leq V_b \leq 2.7~V$                                                                    | 14.8 MHz < fмск $\leq$ 18.5 MHz                 | 14/fмск      |      |                 | ns   |

|                                                 |        |                                                                                                | 11.1 MHz < fмск $\leq$ 14.8 MHz                 | 12/fмск      |      |                 | ns   |

|                                                 |        |                                                                                                | 7.4 MHz < fмск ≤ 11.1 MHz                       | 10/fмск      |      |                 | ns   |

|                                                 |        |                                                                                                | $3.7 \text{ MHz} < f_{MCK} \le 7.4 \text{ MHz}$ | 8/fмск       |      |                 | ns   |

|                                                 |        |                                                                                                | fмск ≤ 3.7 MHz                                  | 6/fмск       |      |                 | ns   |

| SCKp high-/low-level                            | tкн2,  | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                                                         | $2.7~V \leq V_b \leq 4.0~V$                     | fксү2/2 – 20 |      |                 | ns   |

| width                                           | tĸ∟2   | $2.7~V \leq V_{\text{DD}} < 4.0~V,$                                                            | $2.3~V \leq V_b \leq 2.7~V$                     | fксү2/2 – 35 |      |                 | ns   |

| SIp setup time<br>(to SCKp↑) <sup>№te 1</sup>   | tsik2  |                                                                                                |                                                 | 90           |      |                 | ns   |

| SIp hold time<br>(from SCKp↑) <sup>Note 2</sup> | tksi2  |                                                                                                |                                                 | 1/fмск + 50  |      |                 | ns   |

| Delay time from<br>SCKp↓ to SOp                 | tkso2  | $\begin{array}{l} 4.0 \ V \leq V_{DD} \leq 5.5 \ V, \\ C_b = 30 \ pF, \ R_b = 1.4 \end{array}$ |                                                 |              |      | 2/fмск +<br>120 | ns   |

| output <sup>Note 3</sup>                        |        | $\begin{array}{l} 2.7 \ V \leq V_{DD} < 4.0 \ V, \\ C_b = 30 \ pF, \ R_b = 2.7 \end{array}$    |                                                 |              |      | 2/fмск +<br>230 | ns   |

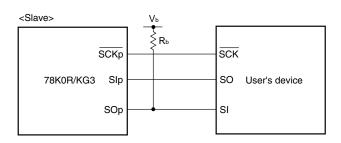

(g) During communication at different potential (2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input)

- **Notes 1.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to  $\overline{SCKp}\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **2.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from  $\overline{SCKp}\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **3.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp<sup>↑</sup>" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

#### CSI mode connection diagram (during communication at different potential)

(Caution and Remarks are given on the next page.)

(A) Grade Products

# (3) Serial interface: Serial array unit (11/18)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS} = 0 \text{ V})$

(f) During communication at different potential (2.5 V, 3 V) (CSI mode) (master mode, SCKp... internal clock output) (1/2)

| Parameter                                                        | Symbol | Conditions                                                                                                                                                                                      | MIN.                  | TYP. | MAX. | Unit |

|------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|------|

| SCKp cycle time                                                  | tксү1  |                                                                                                                                                                                                 | 400 <sup>Note 1</sup> |      |      | ns   |

|                                                                  |        | $\label{eq:VDD} \begin{split} 2.7 \ V &\leq V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \leq V_{\text{b}} \leq 2.7 \ V, \\ C_{\text{b}} &= 30 \ pF, \ R_{\text{b}} = 2.7 \ k\Omega \end{split}$          | 800 <sup>Note 1</sup> |      |      | ns   |

| SCKp high-level width                                            | tкнı   | $\begin{array}{l} 4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V, \\ C_b = 30 \ pF, \ R_b = 1.4 \ k\Omega \end{array}$                                                       | tксү1/2 — 75          |      |      | ns   |

|                                                                  |        | $\begin{array}{l} 2.7 \; V \leq V_{\text{DD}} < 4.0 \; V,  2.3 \; V \leq V_{\text{b}} \leq 2.7 \; V, \\ C_{\text{b}} = 30 \; pF, \; R_{\text{b}} = 2.7 \; k\Omega \end{array}$                  | tксү1/2 – 170         |      |      | ns   |

| SCKp low-level width                                             | tĸL1   | $\begin{array}{l} \label{eq:VDD} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \ 2.7 \ V \leq V_{\text{b}} \leq 4.0 \ V, \\ C_{\text{b}} = 30 \ pF, \ R_{\text{b}} = 1.4 \ k\Omega \end{array}$      | tkcy1/2-20            |      |      | ns   |

|                                                                  |        | $\label{eq:VDD} \begin{split} 2.7 \ V &\leq V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \leq V_{\text{b}} \leq 2.7 \ V, \\ C_{\text{b}} &= 30 \ pF, \ R_{\text{b}} = 2.7 \ k\Omega \end{split}$          | tkcy1/2-35            |      |      | ns   |

| SIp setup time<br>(to SCKp <sup>↑</sup> ) Note 2                 | tsıĸı  | $\begin{array}{l} 4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V, \\ C_b = 30 \ pF, \ R_b = 1.4 \ k\Omega \end{array}$                                                       | 150                   |      |      | ns   |

|                                                                  |        | $\label{eq:VDD} \begin{array}{l} 2.7 \; V \leq V_{\text{DD}} < 4.0 \; V, \; 2.3 \; V \leq V_{\text{b}} \leq 2.7 \; V, \\ C_{\text{b}} = 30 \; pF, \; R_{\text{b}} = 2.7 \; k\Omega \end{array}$ | 275                   |      |      | ns   |

| SIp hold time<br>(from SCKp <sup>↑</sup> ) Note 2                | tksi1  |                                                                                                                                                                                                 | 30                    |      |      | ns   |

|                                                                  |        | $\label{eq:VDD} \begin{split} 2.7 \ V &\leq V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \leq V_{\text{b}} \leq 2.7 \ V, \\ C_{\text{b}} &= 30 \ pF, \ R_{\text{b}} = 2.7 \ k\Omega \end{split}$          | 30                    |      |      | ns   |

| Delay time from $\overline{SCKp}\downarrow$ to SOp output Note 2 | tkso1  | $\begin{array}{l} \label{eq:VDD} \mbox{4.0 V} \le V_{\text{DD}} < 5.5 \ V, \ 2.7 \ V \le V_{\text{b}} \le 4.0 \ V, \\ C_{\text{b}} = 30 \ pF, \ R_{\text{b}} = 1.4 \ k\Omega \end{array}$       |                       |      | 120  | ns   |

|                                                                  |        | $\label{eq:VDD} \begin{split} & 2.7 \ V \leq V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \leq V_{\text{b}} \leq 2.7 \ V, \\ & C_{\text{b}} = 30 \ pF, \ R_{\text{b}} = 2.7 \ k\Omega \end{split}$        |                       |      | 215  | ns   |

**Notes 1.** The value must also be 4/fclk or more.

2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.

# Caution Select the TTL input buffer for SIp and the N-ch open-drain output (VDD tolerance) mode for SOp and SCKp by using the PIMg and POMg registers.

- **Remarks 1.** p: CSI number (p = 01, 10, 20), g: PIM and POM number (g = 0, 4, 14)

- **2.** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2)

- R<sub>b</sub>[Ω]: Communication line (SCKp, SOp) pull-up resistance, C<sub>b</sub>[F]: Communication line (SCKp, SOp) load capacitance, V<sub>b</sub>[V]: Communication line voltage

- **4.** V<sub>IH</sub> and V<sub>IL</sub> below are observation points for the AC characteristics of the serial array unit when communicating at different potentials in CSI mode.

$4.0~V \leq V_{\text{DD}} \leq 5.5~V,~2.7~V \leq V_{\text{b}} \leq 4.0~V;~V_{\text{IH}} = 2.2~V,~V_{\text{IL}} = 0.8~V$

$2.7~V \leq V_{\text{DD}} \leq 4.0~V,~2.3~V \leq V_{\text{b}} \leq 2.7~V;~V_{\text{IH}} = 2.0~V,~V_{\text{IL}} = 0.5~V$

**5.** CSI00 cannot communicate at different potential. Use CSI01, CSI10, and CSI20 for communication at different potential.

|           |                |                     | ľ                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (9/3          |      |

|-----------|----------------|---------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|

| Chapter   | Classification | Function            | Details of<br>Function                     | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pag           | le   |

| Chapter 7 | Soft           | Timer<br>array unit | TOM0: Timer<br>output mode                 | Be sure to clear bits 15 to 8 to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | p.253         |      |

| chap      |                | anay and            | register 0                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |      |

| 0         |                |                     | -                                          | Be sure to clear bits 7 to 2 to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | p.254         |      |