# E·X Renesas Electronics America Inc - UPD78F1166AGF-GAS-AX Datasheet

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 83                                                                                    |

| Program Memory Size        | 256КВ (256К х 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 12K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                  |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 100-LQFP                                                                              |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1166agf-gas-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

[MEMO]

Windows and Windows NT are registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

EEPROM is a trademark of NEC Electronics Corporation.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Caution: This product uses SuperFlash<sup>®</sup> technology licensed from Silicon Storage Technology, Inc.

- The information in this document is current as of July, 2009. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets,

etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or

types are available in every country. Please check with an NEC Electronics sales representative for

availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. In addition, NEC Electronics products are not taken measures to prevent radioactive rays in the product design. When customers use NEC Electronics products with their products, customers shall, on their own responsibility, incorporate sufficient safety measures such as redundancy, fire-containment and anti-failure features to their products in order to avoid risks of the damages to property (including public or social property) or injury (including death) to persons, as the result of defects of NEC Electronics products.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

| Address | Special Function Register (SFR) Name               | Syn    | nbol  | R/W | Manip        | ulable Bit   | Range        | After Reset |

|---------|----------------------------------------------------|--------|-------|-----|--------------|--------------|--------------|-------------|

|         |                                                    |        |       |     | 1-bit        | 8-bit        | 16-bit       |             |

| F0110H  | Serial mode register 00                            | SMR00  |       | R/W | -            | -            |              | 0020H       |

| F0111H  |                                                    |        |       |     |              |              |              |             |

| F0112H  | Serial mode register 01                            | SMR01  |       | R/W | -            | -            |              | 0020H       |

| F0113H  |                                                    |        |       |     |              |              |              |             |

| F0114H  | Serial mode register 02                            | SMR02  |       | R/W | _            | -            | $\checkmark$ | 0020H       |

| F0115H  |                                                    |        |       |     |              |              |              |             |

| F0116H  | Serial mode register 03                            | SMR03  |       | R/W | -            | -            | $\checkmark$ | 0020H       |

| F0117H  |                                                    |        |       |     |              |              |              |             |

| F0118H  | Serial communication operation setting register 00 | SCR00  |       | R/W | -            | -            | $\checkmark$ | 0087H       |

| F0119H  |                                                    |        |       |     |              |              |              |             |

| F011AH  | Serial communication operation setting register 01 | SCR01  |       | R/W | -            | -            | $\checkmark$ | 0087H       |

| F011BH  |                                                    |        |       |     |              |              |              |             |

| F011CH  | Serial communication operation setting register 02 | SCR02  |       | R/W | -            | -            | $\checkmark$ | 0087H       |

| F011DH  |                                                    |        |       |     |              |              |              |             |

| F011EH  | Serial communication operation setting register 03 | SCR03  |       | R/W | -            | -            | $\checkmark$ | 0087H       |

| F011FH  |                                                    |        |       |     |              |              |              |             |

| F0120H  | Serial channel enable status register 0            | SE0L   | SE0   | R   | $\checkmark$ |              | $\checkmark$ | 0000H       |

| F0121H  |                                                    | -      |       |     | -            | -            |              |             |

| F0122H  | Serial channel start register 0                    | SS0L   | SS0   | R/W | $\checkmark$ |              | $\checkmark$ | 0000H       |

| F0123H  |                                                    | -      |       |     | -            | -            |              |             |

| F0124H  | Serial channel stop register 0                     | STOL   | ST0   | R/W | $\checkmark$ |              | $\checkmark$ | 0000H       |

| F0125H  |                                                    | -      |       |     | -            | -            |              |             |

| F0126H  | Serial clock select register 0                     | SPS0L  | SPS0  | R/W | -            |              | $\checkmark$ | 0000H       |

| F0127H  |                                                    | -      |       |     | -            | -            |              |             |

| F0128H  | Serial output register 0                           | SO0    |       | R/W | -            | -            | $\checkmark$ | 0F0FH       |

| F0129H  |                                                    |        |       |     |              |              |              |             |

| F012AH  | Serial output enable register 0                    | SOE0L  | SOE0  | R/W | $\checkmark$ |              | $\checkmark$ | 0000H       |

| F012BH  |                                                    | -      |       |     | -            | -            |              |             |

| F0134H  | Serial output level register 0                     | SOL0L  | SOL0  | R/W | -            |              | $\checkmark$ | 0000H       |

| F0135H  |                                                    | -      |       |     | -            | -            |              |             |

| F0140H  | Serial status register 10                          | SSR10L | SSR10 | R   | -            | $\checkmark$ | $\checkmark$ | 0000H       |

| F0141H  |                                                    |        |       |     | -            | -            |              |             |

| F0142H  | Serial status register 11                          | SSR11L | SSR11 | R   | -            |              | $\checkmark$ | 0000H       |

| F0143H  |                                                    |        |       |     | -            | -            |              |             |

| F0144H  | Serial status register 12                          | SSR12L | SSR12 | R   | -            |              | $\checkmark$ | 0000H       |

| F0145H  |                                                    | -      |       |     | -            | -            |              |             |

| F0146H  | Serial status register 13                          | SSR13L | SSR13 | R   | _            |              | $\checkmark$ | 0000H       |

| F0147H  |                                                    | -      |       |     | _            | -            |              |             |

| F0148H  | Serial flag clear trigger register 10              | SIR10L | SIR10 | R/W | -            |              | $\checkmark$ | 0000H       |

| F0149H  |                                                    |        |       |     | -            | -            |              |             |

| F014AH  | Serial flag clear trigger register 11              | SIR11L | SIR11 | R/W | _            |              | $\checkmark$ | 0000H       |

| F014BH  |                                                    | -      |       |     | -            | -            |              |             |

### Table 3-6. Extended SFR (2nd SFR) List (2/5)

### 3.3 Instruction Address Addressing

### 3.3.1 Relative addressing

### [Function]

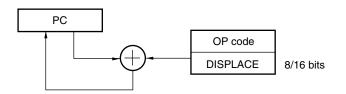

Relative addressing stores in the program counter (PC) the result of adding a displacement value included in the instruction word (signed complement data: -128 to +127 or -32768 to +32767) to the program counter (PC)'s value (the start address of the next instruction), and specifies the program address to be used as the branch destination. Relative addressing is applied only to branch instructions.

### Figure 3-22. Outline of Relative Addressing

### 3.3.2 Immediate addressing

### [Function]

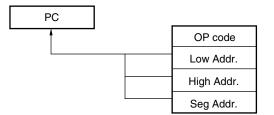

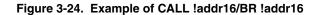

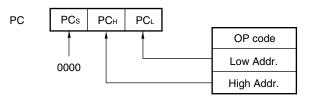

Immediate addressing stores immediate data of the instruction word in the program counter, and specifies the program address to be used as the branch destination.

For immediate addressing, CALL !!addr20 or BR !!addr20 is used to specify 20-bit addresses and CALL !addr16 or BR !addr16 is used to specify 16-bit addresses. 0000 is set to the higher 4 bits when specifying 16-bit addresses.

| Function Name | I/O    | Function                                                                                                                                                     | After Reset        | Alternate Function                   |

|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------|

| P60           | I/O    | Port 6.                                                                                                                                                      | Input port         | SCL0                                 |

| P61           |        | 8-bit I/O port.                                                                                                                                              |                    | SDA0                                 |

| P62           |        | Output of P60 to P63 can be set to N-ch open-drain output (6 V tolerance).                                                                                   |                    | -                                    |

| P63           |        | Input/output can be specified in 1-bit units.                                                                                                                |                    | -                                    |

| P64           |        | For only P64 to P67, use of an on-chip pull-up resistor can be                                                                                               |                    | RD                                   |

| P65           |        | specified by a software setting.                                                                                                                             |                    | WR0                                  |

| P66           |        |                                                                                                                                                              |                    | WR1                                  |

| P67           |        |                                                                                                                                                              |                    | ASTB                                 |

| P70 to P73    | I/O    | Port 7.<br>8-bit I/O port.                                                                                                                                   | Input port         | KR0/EX16 to KR3/<br>EX19             |

| P74 to P77    |        | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                               |                    | KR4/EX20/INTP8 to<br>KR7/EX23/INTP11 |

| P80 to P87    | I/O    | Port 8.<br>8-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting. | Input port         | EX0 to EX7                           |

| P110          | I/O    | Port 11.                                                                                                                                                     | Input port         | ANO0                                 |

| P111          |        | 2-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                             |                    | ANO1                                 |

| P120          | I/O    | Port 12.                                                                                                                                                     | Input port         | INTP0/EXLVI                          |

| P121          | Input  | 1-bit I/O port and 4-bit input port.                                                                                                                         |                    | X1                                   |

| P122          |        | For only P120, use of an on-chip pull-up resistor can be specified by a software setting.                                                                    |                    | X2/EXCLK                             |

| P123          |        | specifica by a software setting.                                                                                                                             |                    | XT1                                  |

| P124          |        |                                                                                                                                                              |                    | XT2                                  |

| P130          | Output | Port 13.<br>1-bit output port and 1-bit I/O port.                                                                                                            | Output port        | -                                    |

| P131          | I/O    | For only P131, use of an on-chip pull-up resistor can be specified by a software setting.                                                                    | Input port         | TI06/TO06                            |

| P140          | I/O    | Port 14.                                                                                                                                                     | Input port         | PCLBUZ0/INTP6                        |

| P141          |        | 6-bit I/O port.                                                                                                                                              |                    | PCLBUZ1/INTP7                        |

| P142          |        | Input of P142 and P143 can be set to TTL input buffer.<br>Output of P142 to P144 can be set to the N-ch open-drain                                           |                    | SCK20/SCL20                          |

| P143          |        | output ( $V_{DD}$ tolerance).                                                                                                                                |                    | SI20/RxD2/SDA20                      |

| P144          |        | Input/output can be specified in 1-bit units.                                                                                                                |                    | SO20/TxD2                            |

| P145          |        | Use of an on-chip pull-up resistor can be specified by a software setting.                                                                                   |                    | TI07/TO07                            |

| P150 to P157  | I/O    | Port 15.<br>8-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                 | Digital input port | ANI8 to ANI15                        |

| Table 4 | -2. P   | ort Fu | nction | s (2/2)     |

|---------|---------|--------|--------|-------------|

|         | - · · · |        |        | 3 ( 5 6 5 7 |

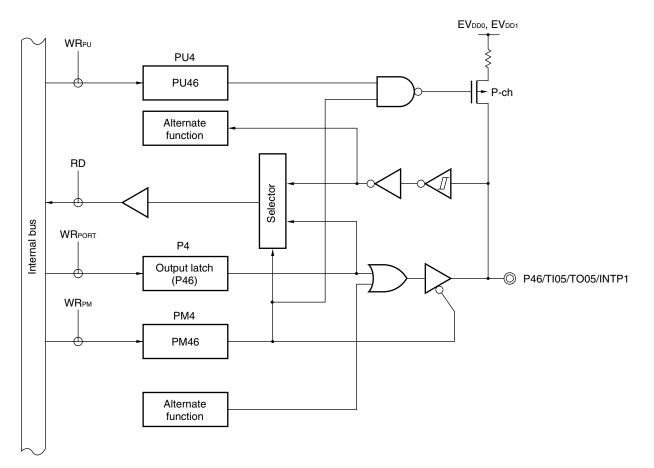

Figure 4-21. Block Diagram of P46

- P4: Port register 4

- PU4: Pull-up resistor option register 4

- PM4: Port mode register 4

- RD: Read signal

- WR××: Write signal

### (2) Setting procedure when using I/O pins of simplified IIC10 and IIC20 functions

- <1> After reset release, the port mode is the input mode (Hi-Z).

- <2> Externally pull up the pin to be used (on-chip pull-up resistor cannot be used).

In case of simplified IIC10: P03, P04 In case of simplified IIC20: P142, P143

- <3> Set the output latch of the corresponding port to 1.

- <4> Set the corresponding bit of the POMn register to 1 to set the N-ch open drain output (VDD withstand voltage) mode.

- <5> Set the corresponding bit of the PMn register to the output mode (data I/O is possible in the output mode).

At this time, the output data is high level, so the pin is in the Hi-Z state.

<6> Enable the operation of the serial array unit and set the mode to the simplified IIC mode.

**Remark** n = 0, 14

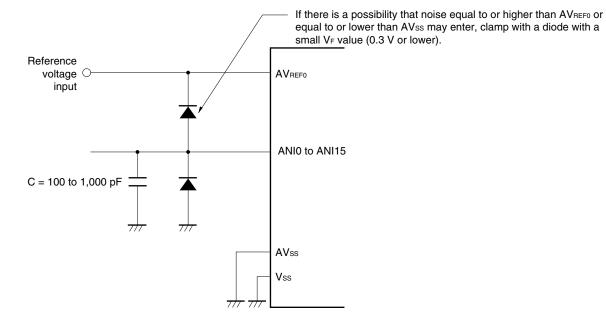

### Figure 11-26. Analog Input Pin Connection

### (6) ANI0/P20 to ANI7/P27 and ANI8/P150 to ANI15/P157

- <1> The analog input pins (ANI0 to ANI7) are also used as input port pins (P20 to P27). The analog input pins (ANI8 to ANI15) are also used as input port pins (P150 to P157). When A/D conversion is performed with any of ANI0 to ANI15 selected, do not access P20 to P27 and P150 to P157 while conversion is in progress; otherwise the conversion resolution may be degraded. It is recommended to select pins used as P20 to P27 and P150 to P157 starting with the ANI0/P20 that is the furthest from AV<sub>REF0</sub>.

- <2> If a digital pulse is applied to the pins adjacent to the pins currently used for A/D conversion, the expected value of the A/D conversion may not be obtained due to coupling noise. Therefore, do not apply a pulse to the pins adjacent to the pin undergoing A/D conversion.

### (7) Input impedance of ANI0 to ANI15 pins

This A/D converter charges a sampling capacitor for sampling during sampling time.

Therefore, only a leakage current flows when sampling is not in progress, and a current that charges the capacitor flows during sampling. Consequently, the input impedance fluctuates depending on whether sampling is in progress, and on the other states.

To make sure that sampling is effective, however, it is recommended to keep the output impedance of the analog input source to within 10 k $\Omega$ , and to connect a capacitor of about 100 pF to the ANI0 to ANI15 pins (see **Figure 11-26**).

### (8) AVREFO pin input impedance

A series resistor string of several tens of  $k\Omega$  is connected between the AV<sub>REF0</sub> and AV<sub>SS</sub> pins. Therefore, if the output impedance of the reference voltage source is high, this will result in a series connection to the series resistor string between the AV<sub>REF0</sub> and AV<sub>SS</sub> pins, resulting in a large reference voltage error.

### (11) Serial output enable register m (SOEm)

SOEm is a register that is used to enable or stop output of the serial communication operation of each channel.

Channel n that enables serial output cannot rewrite by software the value of SOmn of the serial output register m (SOm) to be described below, and a value reflected by a communication operation is output from the serial data output pin.

For channel n, whose serial output is stopped, the SOmn value of the SOm register can be set by software, and that value can be output from the serial data output pin. In this way, any waveform of the start condition and stop condition can be created by software.

SOEm can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of SOEm can be set with an 1-bit or 8-bit memory manipulation instruction with SOEmL. Reset signal generation clears this register to 0000H.

### Figure 13-14. Format of Serial Output Enable Register m (SOEm)

| Address: F01           | 2AH, F(       | 012BH       | After       | reset: 0       | 000H        | R/W       |        |   |   |   |        |   |   |          |        |          |

|------------------------|---------------|-------------|-------------|----------------|-------------|-----------|--------|---|---|---|--------|---|---|----------|--------|----------|

| Symbol                 | 15            | 14          | 13          | 12             | 11          | 10        | 9      | 8 | 7 | 6 | 5      | 4 | 3 | 2        | 1      | 0        |

| SOE0                   | 0             | 0           | 0           | 0              | 0           | 0         | 0      | 0 | 0 | 0 | 0      | 0 | 0 | SOE      | SOE    | SOE      |

|                        |               |             |             |                |             |           |        |   |   |   |        |   |   | 02       | 01     | 00       |

|                        |               |             |             |                |             |           |        |   |   |   |        |   |   |          |        |          |

|                        |               |             |             |                |             |           |        |   |   |   |        |   |   |          |        |          |

| Address: F01           | 6AH, F(       | 016BH       | After       | reset: 0       | 000H        | R/W       |        |   |   |   |        |   |   |          |        |          |

| Address: F01<br>Symbol | 6AH, F(<br>15 | 016BH<br>14 | After<br>13 | reset: 0<br>12 | 0000H<br>11 | R/W<br>10 | 9      | 8 | 7 | 6 | 5      | 4 | 3 | 2        | 1      | 0        |

|                        |               |             |             |                |             |           | 9<br>0 | 8 | 7 | 6 | 5<br>0 | 4 | 3 | 2<br>SOE | 1      | 0<br>SOE |

| Symbol                 | 15            | 14          | 13          | 12             | 11          | 10        | -      | - | - | - | -      | - | - | 1        | 1<br>0 |          |

| Symbol                 | 15            | 14          | 13          | 12             | 11          | 10        | -      | - | - | - | -      | - | - | SOE      | 1      | SOE      |

| SOE | Serial output enable/disable of channel n         |

|-----|---------------------------------------------------|

| mn  |                                                   |

| 0   | Stops output by serial communication operation.   |

| 1   | Enables output by serial communication operation. |

Caution Be sure to clear bits 15 to 3 of SOE0, and bits 15 to 3 and 1 of SOE1 to "0".

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2), mn = 00 to 02, 10, 12

### (3) Processing flow (in single-reception mode)

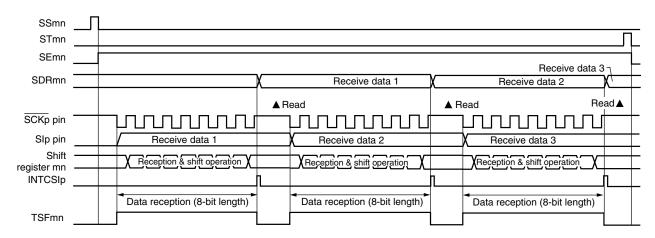

Figure 13-60. Timing Chart of Slave Reception (in Single-Reception Mode) (Type 1: DAPmn = 0, CKPmn = 0)

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2), p: CSI number (p = 00, 01, 10, 20)

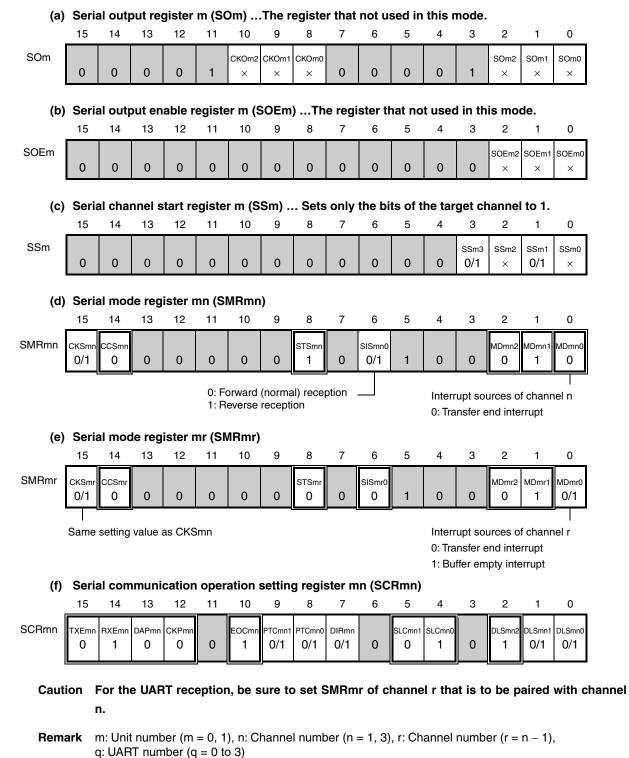

### (1) Register setting

<R>

# Figure 13-79. Example of Contents of Registers for UART Reception of UART (UART0, UART1, UART2, UART3) (1/2)

$\square$ : Setting is fixed in the UART reception mode,  $\square$ : Setting disabled (set to the initial value) ×: Bit that cannot be used in this mode (set to the initial value when not used in any mode) 0/1: Set to 0 or 1 depending on the usage of the user

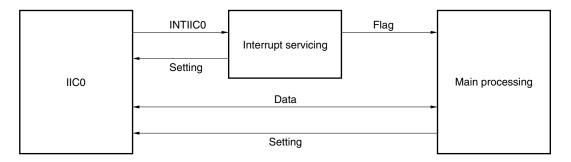

### (3) Slave operation

The processing procedure of the slave operation is as follows.

Basically, the slave operation is event-driven. Therefore, processing by the INTIIC0 interrupt (processing that must substantially change the operation status such as detection of a stop condition during communication) is necessary.

In the following explanation, it is assumed that the extension code is not supported for data communication. It is also assumed that the INTIIC0 interrupt servicing only performs status transition processing, and that actual data communication is performed by the main processing.

Therefore, data communication processing is performed by preparing the following three flags and passing them to the main processing instead of INTIIC0.

### <1> Communication mode flag

This flag indicates the following two communication statuses.

- Clear mode: Status in which data communication is not performed

- Communication mode: Status in which data communication is performed (from valid address detection to stop condition detection, no detection of ACK from master, address mismatch)

### <2> Ready flag

This flag indicates that data communication is enabled. Its function is the same as the INTIICO interrupt for ordinary data communication. This flag is set by interrupt servicing and cleared by the main processing. Clear this flag by interrupt servicing when communication is started. However, the ready flag is not set by interrupt servicing when the first data is transmitted. Therefore, the first data is transmitted without the flag being cleared (an address match is interpreted as a request for the next data).

### <3> Communication direction flag

This flag indicates the direction of communication. Its value is the same as TRC0.

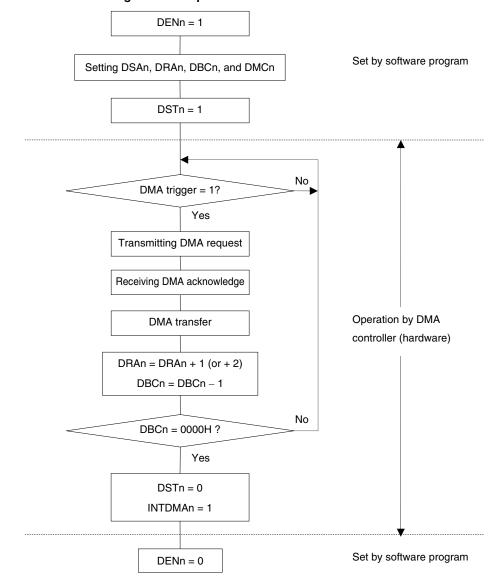

Figure 16-6. Operation Procedure

**Remark** n: DMA channel number (n = 0, 1)

### 17.4.3 Multiple interrupt servicing

Multiple interrupt servicing occurs when another interrupt request is acknowledged during execution of an interrupt. Multiple interrupt servicing does not occur unless the interrupt request acknowledgment enabled state is selected (IE = 1). When an interrupt request is acknowledged, interrupt request acknowledgment becomes disabled (IE = 0). Therefore, to enable multiple interrupt servicing, it is necessary to set (1) the IE flag with the EI instruction during interrupt servicing to enable interrupt acknowledgment.

Moreover, even if interrupts are enabled, multiple interrupt servicing may not be enabled, this being subject to interrupt priority control. Two types of priority control are available: default priority control and programmable priority control is used for multiple interrupt servicing.

In the interrupt enabled state, if an interrupt request with a priority equal to or higher than that of the interrupt currently being serviced is generated, it is acknowledged for multiple interrupt servicing. If an interrupt with a priority lower than that of the interrupt currently being serviced is generated during interrupt servicing, it is not acknowledged for multiple interrupt servicing. Interrupt requests that are not enabled because interrupts are in the interrupt disabled state or because they have a lower priority are held pending. When servicing of the current interrupt ends, the pending interrupt request is acknowledged following execution of at least one main processing instruction execution.

Table 17-5 shows relationship between interrupt requests enabled for multiple interrupt servicing and Figure 17-10 shows multiple interrupt servicing examples.

| Multiple Interru       | ot Request           |                               |        | Mas                           | kable Inte | rrupt Requ                    | iest   |                               |        | Software             |

|------------------------|----------------------|-------------------------------|--------|-------------------------------|------------|-------------------------------|--------|-------------------------------|--------|----------------------|

|                        |                      | Priority Level 0<br>(PR = 00) |        | Priority Level 1<br>(PR = 01) |            | Priority Level 2<br>(PR = 10) |        | Priority Level 3<br>(PR = 11) |        | Interrupt<br>Request |

| Interrupt Being Servic | ed                   | IE = 1                        | IE = 0 | IE = 1                        | IE = 0     | IE = 1                        | IE = 0 | IE = 1                        | IE = 0 |                      |

| Maskable interrupt     | ISP1 = 0<br>ISP0 = 0 | 0                             | ×      | ×                             | ×          | ×                             | ×      | ×                             | ×      | 0                    |

|                        | ISP1 = 0<br>ISP0 = 1 | 0                             | ×      | 0                             | ×          | ×                             | ×      | ×                             | ×      | 0                    |

|                        | ISP1 = 1<br>ISP0 = 0 | 0                             | ×      | 0                             | ×          | 0                             | ×      | ×                             | ×      | 0                    |

|                        | ISP1 = 1<br>ISP0 = 1 | 0                             | ×      | 0                             | ×          | 0                             | ×      | 0                             | ×      | 0                    |

| Software interrupt     |                      | 0                             | ×      | 0                             | ×          | 0                             | ×      | 0                             | ×      | 0                    |

Table 17-5. Relationship Between Interrupt Requests Enabled for Multiple Interrupt Servicing During Interrupt Servicing

Remarks 1. O: Multiple interrupt servicing enabled

- 2. ×: Multiple interrupt servicing disabled

- 3. ISP0, ISP1, and IE are flags contained in the PSW.

- ISP1 = 0, ISP0 = 0: An interrupt of level 1 or level 0 is being serviced.

- ISP1 = 0, ISP0 = 1: An interrupt of level 2 is being serviced.

- ISP1 = 1, ISP0 = 0: An interrupt of level 3 is being serviced.

- ISP1 = 1, ISP0 = 1: Wait for An interrupt acknowledgment.

- IE = 0: Interrupt request acknowledgment is disabled.

- IE = 1: Interrupt request acknowledgment is enabled.

- 4. PR is a flag contained in PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, and PR12H.

- PR = 00: Specify level 0 with  $\times$  PR1 $\times$  = 0,  $\times$  PR0 $\times$  = 0 (higher priority level)

- PR = 01: Specify level 1 with  $\times PR1 \times = 0$ ,  $\times PR0 \times = 1$

- PR = 10: Specify level 2 with  $\times PR1 \times = 1$ ,  $\times PR0 \times = 0$

- PR = 11: Specify level 3 with  $\times$  PR1 $\times$  = 1,  $\times$  PR0 $\times$  = 1 (lower priority level)

- (b) When LVI default start function enabled is set (option byte: LVIOFF = 0)

- When starting operation

- <1> Start in the following initial setting state.

- Set bit 7 (LVION) of LVIM to 1 (enables LVI operation)

- Clear bit 2 (LVISEL) of the low-voltage detection register (LVIM) to 0 (detects level of supply voltage (V<sub>DD</sub>))

- Set the low-voltage detection level selection register (LVIS) to 0EH (default value: VLVI = 2.07 V  $\pm 0.1$  V).

- Set bit 1 (LVIMD) of LVIM to 1 (generates reset when the level is detected)

- Set bit 0 (LVIF) of LVIM to 0 (Detects falling edge "Supply voltage (V\_DD)  $\geq$  detection voltage (V\_LVI)")

- <2> Clear bit 1 (LVIMD) of LVIM to 0 (generates interrupt signal when the level is detected) (default value).

- <3> Release the interrupt mask flag of LVI (LVIMK).

- <4> Execute the EI instruction (when vector interrupts are used).

Figure 22-9 shows the timing of the interrupt signal generated by the low-voltage detector. The numbers in this timing chart correspond to <1> to <3> above.

- When stopping operation Either of the following procedures must be executed.

- When using 8-bit memory manipulation instruction: Write 00H to LVIM.

- When using 1-bit memory manipulation instruction: Clear LVION to 0.

- Cautions 1. Even when the LVI default start function is used, if it is set to LVI operation prohibition by the software, it operates as follows:

- Does not perform low-voltage detection during LVION = 0.

- If a reset is generated while LVION = 0, LVION will be re-set to 1 when the CPU starts after reset release. There is a period when low-voltage detection cannot be performed normally, however, when a reset occurs due to WDT and illegal instruction execution. This is due to the fact that while the pulse width detected by LVI must be 200 µs max., LVION = 1 is set upon reset occurrence, and the CPU starts operating without waiting for the LVI stabilization time.

- When the LVI default start function (bit 0 (LVIOFF) of 000C1H = 0) is used, the LVIRF flag may become 1 from the beginning due to the power-on waveform.

For details of RESF, see CHAPTER 20 RESET FUNCTION.

Standard Products

## DC Characteristics (2/16) (TA = -40 to +85°C, 1.8 V $\leq$ VDD = EVDD0 = EVDD1 $\leq$ 5.5 V, 1.8 V $\leq$ AVREF0 $\leq$ VDD, 1.8 V $\leq$ AVREF1 $\leq$ VDD, VSS = EVSS0 = EVSS1 = AVSS = 0 V)

| Parameter             | Symbol | Conditions                                                                                     |                                                           | MIN. | TYP. | MAX. | Unit |

|-----------------------|--------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| Output current,       | IOL1   | Per pin for P00 to P02, P05, P06,                                                              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 8.5  | mA   |

| Iow <sup>Note 1</sup> |        | P10 to P17, P30, P31, P40 to P47,                                                              | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 1.0  | mA   |

|                       |        | P50 to P57, P64 to P67, P70 to P77,<br>P80 to P87, P120, P130, P131,<br>P140, P141, P144, P145 | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      |      | 0.5  | mA   |

|                       |        | Per pin for P03, P04, P142, P143                                                               | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 8.5  | mA   |

|                       |        |                                                                                                | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 1.5  | mA   |

|                       |        |                                                                                                | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 0.6  | mA   |

|                       |        | Per pin for P60 to P63                                                                         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 15.0 | mA   |

|                       |        |                                                                                                | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 3.0  | mA   |

|                       |        |                                                                                                | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 2.0  | mA   |

|                       |        | Total of P00 to P04, P40 to P47,                                                               | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 20.0 | mA   |

|                       |        | P120, P130, P131, P140 to P145                                                                 | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 15.0 | mA   |

|                       |        | (When duty = 70% <sup>Note 2</sup> )                                                           | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 9.0  | mA   |

|                       |        | Total of P05, P06, P10 to P17, P30,                                                            | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 45.0 | mA   |

|                       |        | P31, P50 to P57, P60 to P67,                                                                   | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 35.0 | mA   |

|                       |        | P70 to P77, P80 to P87<br>(When duty = 70% <sup>Note 2</sup> )                                 | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 20.0 | mA   |

|                       |        | Total of all pins                                                                              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 65.0 | mA   |

|                       |        | (When duty = $60\%^{Note 2}$ )                                                                 | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 50.0 | mA   |

|                       |        |                                                                                                | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 29.0 | mA   |

|                       | IOL2   | Per pin for P20 to P27, P150 to P157                                                           | $AV_{\text{REF0}} \leq V_{\text{DD}}$                     |      |      | 0.4  | mA   |

|                       |        | Per pin for P110, P111                                                                         | $AV_{REF1} \leq V_{DD}$                                   |      |      | 0.4  | mA   |

**Notes 1.** Value of current at which the device operation is guaranteed even if the current flows from an output pin to EVsso, EVss1, Vss, and AVss pin.

Specification under conditions where the duty factor is 60% or 70%.

The output current value that has changed the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

- Total output current of pins =  $(I_{OL} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 50% and IoL = 20.0 mA

Total output current of pins =  $(20.0 \times 0.7)/(50 \times 0.01) = 28.0 \text{ mA}$

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

### (3) Serial interface: Serial array unit (5/18)

### (d) During communication at same potential (simplified l<sup>2</sup>C mode)

### • Conventional-specification products (µPD78F116x)

### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, \text{ V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS} = 0 \text{ V})$

|         | Parameter                     | Symbol  | Conditions                                                                                                                                                                  | MIN.         | MAX.                | Unit |

|---------|-------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------|

| <r></r> | SCLr clock frequency          | fscL    | $\begin{array}{l} 2.7 \; V \leq V_{\text{DD}} \leq 5.5 \; V, \\ C_{\text{b}} = 100 \; pF, \; R_{\text{b}} = 3 \; k\Omega \end{array} \end{array} \label{eq:constraint}$     |              | 400 <sup>Note</sup> | kHz  |

|         | Hold time when SCLr = "L"     | tLOW    | $\begin{array}{l} 2.7 \; V \leq V_{\text{DD}} \leq 5.5 \; V, \\ C_{\text{b}} = 100 \; pF, \; R_{\text{b}} = 3 \; k\Omega \end{array} \end{array} \label{eq:constraint}$     | 995          |                     | ns   |

|         | Hold time when SCLr = "H"     | tніgн   | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} = 100 \ p\text{F}, \ R_{\text{b}} = 3 \ k\Omega \end{array} \end{array} \label{eq:eq:eq:energy}$ | 995          |                     | ns   |

|         | Data setup time (reception)   | tsu:dat | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} = 100 \ p\text{F}, \ R_{\text{b}} = 3 \ k\Omega \end{array} \end{array} \label{eq:constraint}$   | 1/fмск + 120 |                     | ns   |

|         | Data hold time (transmission) | thd:dat | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} = 100 \ p\text{F}, \ R_{\text{b}} = 3 \ k\Omega \end{array} \end{array} \label{eq:constraint}$   | 0            | 160                 | ns   |

<R> Note The value must also be fmck/4 or less.

### • Expanded-specification products (µPD78F116xA)

### $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \leq \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \leq 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS} = 0 \text{ V})$

|   | Parameter                     | Symbol  | Conditions                                                                                                                                                                             | MIN.         | MAX.                | Unit |

|---|-------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------|

| • | SCLr clock frequency          | fsc∟    | $\label{eq:VDD} \begin{split} 2.7 \ V &\leq V_{\text{DD}} \leq 5.5 \ V, \\ C_b &= 100 \ pF, \ R_b = 3 \ k\Omega \end{split}$                                                           |              | 400 <sup>Note</sup> | kHz  |

|   |                               |         | $\label{eq:VDD} \begin{array}{l} 1.8 \ V \leq V_{\text{DD}} < 2.7 \ V \\ C_{\text{b}} = 100 \ pF, \ R_{\text{b}} = 5 \ k\Omega \end{array}$                                            |              | 300 <sup>Note</sup> | kHz  |

|   | Hold time when SCLr = "L"     | t∟ow    | $\label{eq:VDD} \begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} = 100 \ pF, \ R_{\text{b}} = 3 \ k\Omega \end{array}$                                        | 995          |                     | ns   |

|   |                               |         | $\label{eq:VDD} \begin{split} 1.8 \ V &\leq V_{\text{DD}} < 2.7 \ V \\ C_{\text{b}} &= 100 \ p\text{F}, \ R_{\text{b}} = 5 \ k\Omega \end{split}$                                      | 1500         |                     | ns   |

|   | Hold time when SCLr = "H"     | tнıgн   | $\label{eq:VDD} \begin{split} 2.7 \ V &\leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} &= 100 \ p\text{F}, \ R_{\text{b}} = 3 \ k\Omega \end{split}$                                  | 995          |                     | ns   |

|   |                               |         | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} < 2.7 \mbox{ V} \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k} \Omega \end{array}$                       | 1500         |                     | ns   |

|   | Data setup time (reception)   | tsu:dat | $\label{eq:VDD} \begin{split} 2.7 \ V &\leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} &= 100 \ p\text{F}, \ R_{\text{b}} = 3 \ k\Omega \end{split}$                                  | 1/fмск + 120 |                     | ns   |

|   |                               |         | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} < 2.7 \mbox{ V} \\ C_{\mbox{b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{b}} = 5 \mbox{ k} \Omega \end{array}$     | 1/fмск + 230 |                     | ns   |

|   | Data hold time (transmission) | thd:dat | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ C_{\mbox{b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{b}} = 3 \mbox{ k} \Omega \end{array}$ | 0            | 160                 | ns   |

|   |                               |         | $\label{eq:linear} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} < 2.7 \mbox{ V} \\ C_{\mbox{b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{b}} = 5  k\Omega \end{array}$          | 0            | 210                 | ns   |

<R> Note The value must also be fmck/4 or less.

(Remarks are given on the next page.)

(A) Grade Products

| Manufacturer  | Part Number       | SMD/         | Frequency | Recommended   | Circuit Constants | Oscillation Vo | oltage Range |

|---------------|-------------------|--------------|-----------|---------------|-------------------|----------------|--------------|

|               |                   | Lead         | (MHz)     | C1 (pF)       | C2 (pF)           | MIN. (V)       | MAX. (V)     |

| Murata        | CSTCE12M0G55-R0   | SMD          | 12.0      | Internal (33) | Internal (33)     | 1.8            | 5.5          |

| Manufacturing | CSTCE16M0V53-R0   | SMD          | 16.0      | Internal (15) | Internal (15)     | 1.8            |              |

| Co., Ltd.     | CSTLS16M0X51-B0   | Lead         |           | Internal (5)  | Internal (5)      | 1.8            |              |

|               | CSTCE20M0V53-R0   | SMD          | 20.0      | Internal (15) | Internal (15)     | 1.9            |              |

|               | CSTCG20M0V53-R0   | Small<br>SMD |           | Internal (15) | Internal (15)     | 2.0            |              |

|               | CSTLS20M0X51-B0   | Lead         |           | Internal (5)  | Internal (5)      | 1.9            |              |

| TOKO, Inc.    | DCRHYC(P)12.00A   | Lead         | 12.0      | Internal (22) | Internal (22)     | 1.8            | 5.5          |

|               | DCRHZ(P)16.00A-15 | Lead         | 16.0      | Internal (15) | Internal (15)     |                |              |

|               | DCRHZ(P)20.00A-15 | Lead         | 20.0      | Internal (15) | Internal (15)     | 2.0            |              |

|               | DECRHZ20.00       | SMD          |           | Internal (10) | Internal (10)     | 1.8            |              |

### (3) X1 oscillation: Ceramic resonator (AMPH = 1, RMC = 00H, $T_A = -40$ to +85°C)

- Caution The oscillator constants shown above are reference values based on evaluation in a specific environment by the resonator manufacturer. If it is necessary to optimize the oscillator characteristics in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit.

- <R>

When doing so, check the conditions for using the AMPH bit, RMC register, and whether to enter or exit the STOP mode.

The oscillation voltage and oscillation frequency only indicate the oscillator characteristic. Use the 78K0R/KG3 so that the internal operation conditions are within the specifications of the DC and AC characteristics.

(A) Grade Products

## DC Characteristics (2/16) (TA = -40 to +85°C, 1.8 V $\leq$ VDD = EVDD0 = EVDD1 $\leq$ 5.5 V, 1.8 V $\leq$ AVREF0 $\leq$ VDD, 1.8 V $\leq$ AVREF1 $\leq$ VDD, VSS = EVSS0 = EVSS1 = AVSS = 0 V)

| Parameter             | Symbol | Conditions                                                                                     |                                                           | MIN. | TYP. | MAX. | Unit |

|-----------------------|--------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| Output current,       | IOL1   | Per pin for P00 to P02, P05, P06,                                                              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 8.5  | mA   |

| IOW <sup>Note 1</sup> |        | P10 to P17, P30, P31, P40 to P47,                                                              | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 1.0  | mA   |

|                       |        | P50 to P57, P64 to P67, P70 to P77,<br>P80 to P87, P120, P130, P131,<br>P140, P141, P144, P145 | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      |      | 0.5  | mA   |

|                       |        | Per pin for P03, P04, P142, P143                                                               | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 8.5  | mA   |

|                       |        |                                                                                                | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 1.5  | mA   |

|                       |        |                                                                                                | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 0.6  | mA   |

|                       |        | Per pin for P60 to P63                                                                         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 15.0 | mA   |

|                       |        |                                                                                                | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 3.0  | mA   |

|                       |        |                                                                                                | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 2.0  | mA   |

|                       |        | Total of P00 to P04, P40 to P47,                                                               | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 20.0 | mA   |

|                       |        | P120, P130, P131, P140 to P145<br>(When duty = 70% <sup>Note 2</sup> )                         | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 15.0 | mA   |

|                       |        |                                                                                                | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 9.0  | mA   |

|                       |        | Total of P05, P06, P10 to P17, P30,                                                            | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 45.0 | mA   |

|                       |        | P31, P50 to P57, P60 to P67,<br>P70 to P77, P80 to P87                                         | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 35.0 | mA   |

|                       |        | (When duty = $70\%^{\text{Note 2}}$ )                                                          | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 20.0 | mA   |

|                       |        | Total of all pins                                                                              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 65.0 | mA   |

|                       |        | (When duty = $60\%^{Note 2}$ )                                                                 | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 50.0 | mA   |

|                       |        |                                                                                                | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |      |      | 29.0 | mA   |

|                       | IOL2   | Per pin for P20 to P27, P150 to P157                                                           | $AV_{\text{REF0}} \leq V_{\text{DD}}$                     |      |      | 0.4  | mA   |

|                       |        | Per pin for P110, P111                                                                         | $AV_{\text{REF1}} \leq V_{\text{DD}}$                     |      |      | 0.4  | mA   |

**Notes 1.** Value of current at which the device operation is guaranteed even if the current flows from an output pin to EVsso, EVss1, Vss, and AVss pin.

Specification under conditions where the duty factor is 60% or 70%.

The output current value that has changed the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

- Total output current of pins =  $(I_{OL} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 50% and IoL = 20.0 mA

Total output current of pins =  $(20.0 \times 0.7)/(50 \times 0.01) = 28.0 \text{ mA}$

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

### Caution P02 to P04, P43, P45, P142 to P144 do not output high level in N-ch open-drain mode.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

### C.1 Major Revisions in This Edition

| Dava        | Description                                                                                                                                                                                                                                                           | (1/            |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Page        | Description                                                                                                                                                                                                                                                           | Classification |

| Throughout  |                                                                                                                                                                                                                                                                       |                |

| _           | Change of status of (A) grade products of the expanded-specification products from under development to mass production                                                                                                                                               | (b)            |

| CHAPTER 1   | OUTLINE                                                                                                                                                                                                                                                               |                |

| p.18        | Change of 1.1 Differences Between Conventional-Specification Products ( $\mu$ PD78F116x) and Expanded-Specification Products ( $\mu$ PD78F116xA)                                                                                                                      | (c)            |

| CHAPTER 3   | CPU ARCHITECTURE                                                                                                                                                                                                                                                      |                |

| p.62        | Change of Table 3-2. Internal ROM Capacity                                                                                                                                                                                                                            | (a)            |

| pp.67 to 73 | Change of Figure 3-9 to Figure 3-15 Correspondence Between Data Memory and Addressing                                                                                                                                                                                 | (c)            |

| p.75        | Addition of Caution to 3.2.1 (3) Stack pointer (SP)                                                                                                                                                                                                                   | (c)            |

| CHAPTER 4   | PORT FUNCTIONS                                                                                                                                                                                                                                                        |                |

| p.139       | Change of Figure 4-30. Block Diagram of P110 and P111                                                                                                                                                                                                                 | (c)            |

| CHAPTER 5   | EXTERNAL BUS INTERFACE                                                                                                                                                                                                                                                |                |

| p.175       | Addition of 5.6 Number of Instructed Wait Cycles According to External Wait Cycles                                                                                                                                                                                    | (c)            |

| CHAPTER 6   | CLOCK GENERATOR                                                                                                                                                                                                                                                       |                |

| pp.189, 190 | Addition of fMAINC to Figure 6-1. Block Diagram of Clock Generator and Remark                                                                                                                                                                                         | (c)            |

| p.191       | Change of description of AMPH bit in Figure 6-2. Format of Clock Operation Mode Control Register (CMC)                                                                                                                                                                | (c)            |

| p.199       | Change of description of RTCEN bit in Figure 6-7. Format of Peripheral Enable Register (1/2)                                                                                                                                                                          | (c)            |

| p.201       | Change of Caution 5 in Figure 6-8. Format of Operation Speed Mode Control Register (OSMC) and addition of Caution 4                                                                                                                                                   | (c)            |

| p.221       | Change of description of AMPH bit in Table 6-4. CPU Clock Transition and SFR Register Setting Examples (1/4) (2) and addition of Remark                                                                                                                               | (c)            |

| p.222       | Change of description of AMPH bit in Table 6-4. CPU Clock Transition and SFR Register Setting Examples (2/4) (4) and addition of Remark                                                                                                                               | (c)            |

| p.224       | Change of (9) CPU clock changing from subsystem clock (D) to high-speed system clock (C) in Table 6-4. CPU Clock Transition and SFR Register Setting Examples (4/4)                                                                                                   | (c)            |

| p.224       | Change of (11) • STOP mode (H) set while CPU is operating with internal high-speed<br>oscillation clock (B) • STOP mode (I) set while CPU is operating with high-speed system<br>clock (C) in Table 6-4. CPU Clock Transition and SFR Register Setting Examples (4/4) | (c)            |

| p.227       | Change of Table 6-6. Maximum Time Required for Main System Clock Switchover                                                                                                                                                                                           | (c)            |

| p.227       | Change of Table 6-8. Maximum Number of Clocks Required in Type 2                                                                                                                                                                                                      | (c)            |

| p.228       | Change of Table 6-9. Maximum Number of Clocks Required in Type 3 and addition of Remark                                                                                                                                                                               | (c)            |

| CHAPTER 7   | TIMER ARRAY UNIT                                                                                                                                                                                                                                                      |                |

| p.232       | Change of Figure 7-1. Block Diagram of Timer Array Unit                                                                                                                                                                                                               | (c)            |

| p.239       | Change of description of CKS0n bit in Figure 7-6. Format of Timer Mode Register 0n (TMR0n) (1/3)                                                                                                                                                                      | (a)            |

**Remark** "Classification" in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note,(d): Addition/change of package, part number, or management division, (e): Addition/change of related documents