Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                           |

| Number of I/O              | 93                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                              |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 120-VFBGA                                                                 |

| Supplier Device Package    | 120-BGA (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg995f1024-bga120t |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

wake-up time, makes it attractive to remain in low energy modes for long periods and thus saving energy consumption.

Tip

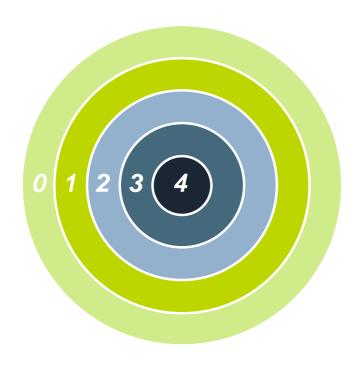

Throughout this document, the first figure in every module description contains an Energy Mode Indicator showing which energy mode(s) the module can operate (see Table 3.1 (p. 8) ).

Table 3.1. Energy Mode Description

| Energy Mode | Name                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 1 2 3 4   | EM0 – Energy Mode 0<br>(Run mode)        | In EM0, the CPU is running and consuming as little as 219 $\mu\text{A}/\text{MHz},$ when running code from flash. All peripherals can be active.                                                                                                                                                                                                                                                                                             |

| 0 1 2 3 4   | EM1 – Energy Mode 1<br>(Sleep Mode)      | In EM1, the CPU is sleeping and the power consumption is only 80 $\mu$ A/MHz. All peripherals, including DMA, PRS and memory system, are still available.                                                                                                                                                                                                                                                                                    |

| 01234       | EM2 – Energy Mode 2<br>(Deep Sleep Mode) | In EM2 the high frequency oscillator is turned off, but with the 32.768 kHz oscillator running, selected low energy peripherals (LCD, RTC, LETIMER, PCNT, LEUART, $1^2$ C, LESENSE, OPAMP, USB, WDOG and ACMP) are still available. This gives a high degree of autonomous operation with a current consumption as low as 1.1 $\mu$ A with RTC enabled. Power-on Reset, Brown-out Detection and full RAM and CPU retention is also included. |

| 01234       | EM3 - Energy Mode 3<br>(Stop Mode)       | In EM3, the low-frequency oscillator is disabled, but there is still full CPU and RAM retention, as well as Power-on Reset, Pin reset, EM4 wake-up and Brown-out Detection, with a consumption of only 0.8 $\mu$ A. The low-power ACMP, asynchronous external interrupt, PCNT, and I <sup>2</sup> C can wake-up the device. Even in this mode, the wake-up time is a few microseconds.                                                       |

| 01230       | EM4 – Energy Mode 4<br>(Shutoff Mode)    | In EM4, the current is down to 20 nA and all chip functionality is turned off except the pin reset, GPIO pin wake-up, GPIO pin retention, Backup RTC (including retention RAM) and the Power-On Reset. All pins are put into their reset state.                                                                                                                                                                                              |

# **3.5 Product Overview**

Table 3.2 (p. 8) shows a device overview of the EFM32GG Microcontroller Series, including peripheral functionality. For more information, the reader is referred to the device specific datasheets.

Table 3.2. EFM32GG Microcontroller Series

| EFM32GG Part<br># | Flash | RAM | GPIO(pins) | USB | ГСD | USART+UART | LEUART | l²C | Timer(PWM) | LETIMER | RTC | PCNT | Watchdog | ADC(pins) | DAC(pins) | ACMP(pins) | AES | EBI | LESENSE | Op-Amps | Package |

|-------------------|-------|-----|------------|-----|-----|------------|--------|-----|------------|---------|-----|------|----------|-----------|-----------|------------|-----|-----|---------|---------|---------|

| 230F512           | 512   | 128 | 56         | -   | -   | 3          | 2      | 2   | 4<br>(12)  | 1       | 1   | 3    | 1        | 1<br>(8)  | 2<br>(2)  | 2<br>(16)  | Y   | -   | Y       | 3       | QFN64   |

# **5 Memory and Bus System**

#### **Quick Facts**

#### What?

A low latency memory system, including low energy flash and RAM with data retention, makes extended use of low-power energymodes possible.

#### Why?

RAM retention reduces the need for storing data in flash and enables frequent use of the ultra low energy modes EM2 and EM3 with as little as  $0.8 \mu$ A current consumption.

#### How?

Low energy and non-volatile flash memory stores program and application data in all energy modes and can easily be reprogrammed in system. Low leakage RAM, with data retention in EM0 to EM3, removes the data restore time penalty, and the DMA ensures fast autonomous transfers with predictable response time.

# **5.1 Introduction**

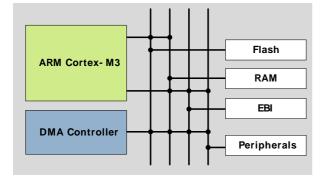

The EFM32GG contains an AMBA AHB Bus system allowing bus masters to access the memory mapped address space. A multilayer AHB bus matrix, using a Round-robin arbitration scheme, connects the master bus interfaces to the AHB slaves (Figure 5.1 (p. 16)). The bus matrix allows several AHB slaves to be accessed simultaneously. An AMBA APB interface is used for the peripherals, which are accessed through an AHB-to-APB bridge connected to the AHB bus matrix. The AHB bus masters are:

- Cortex-M3 ICode: Used for instruction fetches from Code memory (0x00000000 0x1FFFFFF).

- Cortex-M3 DCode: Used for debug and data access to Code memory (0x00000000 0x1FFFFFF).

- Cortex-M3 System: Used for instruction fetches, data and debug access to system space (0x20000000 0xDFFFFFF).

- DMA: Can access EBI, SRAM, Flash and peripherals (0x00000000 0xDFFFFFF).

- USB DMA: Can access EBI, SRAM and Flash (0x80000000 0xDFFFFFF, 0x00000000 0x3FFFFFF), and the AHB-peripherals: USB and AES.

# **10 EMU - Energy Management Unit**

### **Quick Facts**

#### What?

The EMU (Energy Management Unit) handles the different low energy modes in the EFM32GG microcontrollers.

#### Why?

The need for performance and peripheral functions varies over time in most applications. By efficiently scaling the available resources in real-time to match the demands of the application, the energy consumption can be kept at a minimum.

#### How?

With a broad selection of energy modes, a high number of low-energy peripherals available even in EM2, and short wakeup time (2 µs from EM2 and EM3), applications can dynamically minimize energy consumption during program execution.

# **10.1 Introduction**

The Energy Management Unit (EMU) manages all the low energy modes (EM) in EFM32GG microcontrollers. Each energy mode manages if the CPU and the various peripherals are available. The energy modes range from EM0 to EM4, where EM0, also called run mode, enables the CPU and all peripherals. The lowest recoverable energy mode, EM3, disables the CPU and most peripherals while maintaining wake-up and RAM functionality. EM4 disables everything except the POR, pin reset and optionally Backup RTC, 512 byte data retention, GPIO state retention, and EM4 reset wakeup request.

The various energy modes differ in:

- Energy consumption

- CPU activity

- Reaction time

- · Wake-up triggers

- Active peripherals

- · Available clock sources

Low energy modes EM1 to EM4 are enabled through the application software. In EM1-EM3, a range of wake-up triggers return the microcontroller back to EM0. EM4 can only return to EM0 by power on reset, external pin reset, EM4 GPIO wakeup request, or Backup RTC interrupt.

The EMU can also be used to turn off the power to unused SRAM blocks.

# **10.2 Features**

- Energy Mode control from software

- · Flexible wakeup from low energy modes

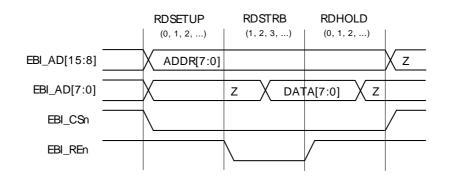

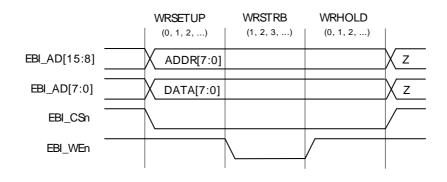

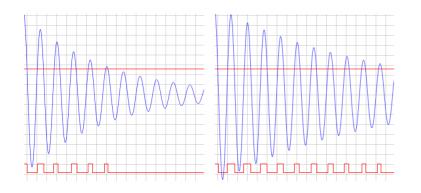

Figure 14.2. EBI Non-multiplexed 8-bit Data, 8-bit Address Read Operation

Figure 14.3. EBI Non-multiplexed 8-bit Data, 8-bit Address Write Operation

# 14.3.2 Multiplexed 16-bit Data, 16-bit Address Mode

In this mode, 16-bit address and 16-bit data is supported, but the utilization of an external latch is required. The 16-bit address and 16-bit data bits are multiplexed on the EBI\_AD lines. An illustration of such a setup is shown in Figure 14.4 (p. 179). This mode is set by programming the MODE field in the EBI\_CTRL register to D16A16ALE.

## Note

In this mode the 16-bit address is organized in 2-byte chunks at memory addresses aligned to 2-byte offsets. Consequently, the LSB of the 16-bit address will always be 0. In order to double the address space, the 16-bit address is internally shifted one bit to the right so that the LSB of the address driven into the EBI\_AD bus, i.e. the EBI\_AD[0]-bit, corresponds to the second least significant bit of the address, i.e. ADDR[1]. At the external device, the LSB of the address must be tied either low or high in order to create a full address.

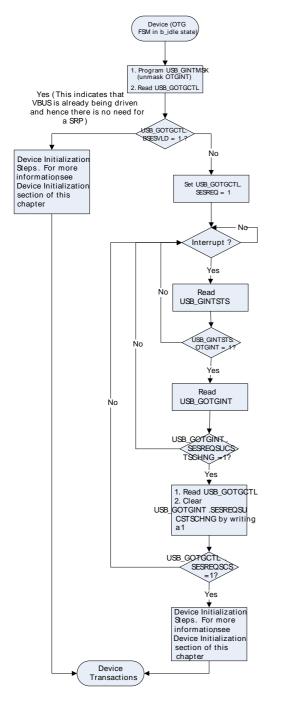

### Figure 15.33. SRP Initiation by the Core When Acting as a B-Device

#### Note

The programming flow illustrated in Figure 15.33 (p. 328) is similar to OTG revision 1.3. This is because the presence or absence of VBUS pulsing is transparent to the application.

## 15.4.6.2 OTG Revision 2.0 Host Negotiation Protocol

When the core is operating as A-device, the application must execute a GetStatus() operation to the B-device with a frequency of THOST\_REQ\_POLL to determine the state of the host request flag in the B-device. If the host request flag is set in B-device it must program the core to change its role within THOST\_REQ\_SUSP.

Figure 15.34 (p. 329) shows the programming steps that need to be performed by A-device's application (core as A-device) in order to change its role to device. In Figure 15.34 (p. 329), the A-device performs a role change, becomes a B-device and then reverts back to host (A-device) mode of operation.

# EFM°32

### ...the world's most energy friendly microcontrollers

|       | Name                                                                             | Reset                                                                                                                  | Acce                                    | ss Description                                                                                                  |

|-------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 31:25 | Reserved                                                                         | To ensure c                                                                                                            | ompatibility w                          | ith future devices, always write bits to 0. More information in Section 2.1 (p. 3)                              |

| 24:21 | FN                                                                               | 0x0                                                                                                                    | R                                       | Frame Number device only                                                                                        |

|       | This is the leas                                                                 | t significant 4 bits of the Fi                                                                                         | ame number                              | in which the packet is received on the USB.                                                                     |

| 20:17 | PKTSTS                                                                           | 0x0                                                                                                                    | R                                       | Packet Status (host or device)                                                                                  |

|       | Indicates the st                                                                 | tatus of the received packe                                                                                            | et.                                     |                                                                                                                 |

|       | Value                                                                            | Mode                                                                                                                   |                                         | Description                                                                                                     |

|       | 1                                                                                | GOUTNAK                                                                                                                |                                         | Device mode: Global OUT NAK (triggers an interrupt).                                                            |

|       | 2                                                                                | PKTRCV                                                                                                                 |                                         | Host mode: IN data packet received.                                                                             |

|       |                                                                                  |                                                                                                                        |                                         | Device mode: OUT data packet received.                                                                          |

|       | 3                                                                                | XFERCOMPL                                                                                                              |                                         | Host mode: IN transfer completed (triggers an interrupt).                                                       |

|       |                                                                                  |                                                                                                                        |                                         | Device mode: OUT transfer completed (triggers an interrupt).                                                    |

|       | 4                                                                                | SETUPCOMPL                                                                                                             |                                         | Device mode: SETUP transaction completed (triggers an interrupt).                                               |

|       | 5                                                                                | TGLERR                                                                                                                 |                                         | Host mode: Data toggle error (triggers an interrupt).                                                           |

|       | 6                                                                                | SETUPRCV                                                                                                               |                                         | Device mode: SETUP data packet received.                                                                        |

|       | 7                                                                                | CHLT                                                                                                                   |                                         | Host mode: Channel halted (triggers an interrupt).                                                              |

| 16:15 | DPID                                                                             | 0x0                                                                                                                    | R                                       | Data PID (host or device)                                                                                       |

|       |                                                                                  |                                                                                                                        |                                         | cket. Device mode: Indicates the Data PID of the received OUT data packet.                                      |

|       | Host mode: Inc                                                                   | licates the Data PID of the                                                                                            | received pac                            | Skel. Device mode. Indicates the Data indicate interfectived COT data packet.                                   |

|       | Host mode: Inc                                                                   | licates the Data PID of the                                                                                            | received pac                            |                                                                                                                 |

|       |                                                                                  |                                                                                                                        | received pac                            | · · ·                                                                                                           |

|       | Value                                                                            | Mode                                                                                                                   | received pac                            | Description                                                                                                     |

|       | Value<br>0                                                                       | Mode<br>DATA0                                                                                                          | received pac                            | Description DATA0 PID.                                                                                          |

|       | Value<br>0<br>1                                                                  | Mode<br>DATA0<br>DATA1                                                                                                 | received pac                            | Description DATA0 PID. DATA1 PID.                                                                               |

| 14:4  | Value<br>0<br>1<br>2                                                             | Mode<br>DATA0<br>DATA1<br>DATA2                                                                                        | R received pace                         | Description DATA0 PID. DATA1 PID. DATA2 PID.                                                                    |

| 14:4  | Value 0 1 2 3 BCNT                                                               | ModeDATA0DATA1DATA2MDATA                                                                                               | R                                       | Description DATA0 PID. DATA1 PID. DATA2 PID. MDATA PID. Byte Count (host or device)                             |

| 14:4  | Value<br>0<br>1<br>2<br>3<br>BCNT<br>Host mode: Inc                              | Mode<br>DATA0<br>DATA1<br>DATA2<br>MDATA<br>0x000                                                                      | R<br>e received IN                      | Description DATA0 PID. DATA1 PID. DATA2 PID. MDATA PID. Byte Count (host or device) I data packet.              |

| 14:4  | Value<br>0<br>1<br>2<br>3<br>BCNT<br>Host mode: Inc                              | Mode<br>DATA0<br>DATA1<br>DATA2<br>MDATA<br>0x000<br>dicates the byte count of th                                      | R<br>e received IN                      | Description DATA0 PID. DATA1 PID. DATA2 PID. MDATA PID. Byte Count (host or device) I data packet.              |

|       | Value<br>0<br>1<br>2<br>3<br>BCNT<br>Host mode: Inc<br>Device mode: I<br>CHEPNUM | Mode<br>DATA0<br>DATA1<br>DATA2<br>MDATA<br>0x000<br>dicates the byte count of th<br>ndicates the byte count of<br>0x0 | R<br>e received IN<br>the received<br>R | Description DATA0 PID. DATA1 PID. DATA2 PID. MDATA PID. Byte Count (host or device) I data packet. data packet. |

# 15.6.16 USB\_GRXSTSP - Receive Status Read and Pop Register

A read to the Receive Status Read and Pop register returns the contents of the top of the Receive FIFO and pops the top data entry out of the RxFIFO. The receive status contents must be interpreted differently in Host and Device modes. The core ignores the receive status pop/read when the receive FIFO is empty and returns a value of 0x00000000. The application must only pop the Receive Status FIFO when the Receive FIFO Non-Empty bit of the Core Interrupt register (USB\_GINTSTS.RXFLVL) is asserted.

| Offset  |                                              |                                                                                                             | Bi                   | t Positio | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |  |  |  |  |

|---------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| 0x3C020 | 31<br>30<br>29<br>28<br>27<br>27<br>25<br>25 | 24<br>23<br>22<br>21                                                                                        | 20<br>19<br>18<br>17 | 16<br>15  | 14         12         12         12         12         12         12         12         12         12         12         12         12         12         12         12         12         12         12         12         12         12         13         14         15         14         15         14         15         15         16         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17 | 0 7 10 3 |  |  |  |  |

| Reset   |                                              | 0×0                                                                                                         | 0×0                  | 0×0       | 000X0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0×0      |  |  |  |  |

| Access  |                                              | Ľ                                                                                                           | R                    | ĸ         | ٢                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ٣        |  |  |  |  |

| Name    |                                              | Z                                                                                                           | PKTSTS               | DIPID     | BCNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CHEPNUM  |  |  |  |  |

| Bit     | Name                                         | Reset Access Description                                                                                    |                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |  |  |  |  |

| 31:25   | Reserved                                     | To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3, |                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |  |  |  |  |

| Bit | Name                    | Reset                  | Access          | Description                                                                                                                                                             |

|-----|-------------------------|------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                         | ister (USB_GINTST      | S.PRTINT). This | to trigger an interrupt to the application using the Host Port Interrupt bit of<br>bit can be set only by the core and the application should write 1 to clear<br>rupt. |

| 0   | PRTCONNSTS              | 0                      | R               | Port Connect Status                                                                                                                                                     |

|     | When this bit is 1 a de | evice is attached to t | the port.       |                                                                                                                                                                         |

# 15.6.35 USB\_HCx\_CHAR - Host Channel x Characteristics Register

| Offset  |       |       | -      |    |          |    |    |    |    |    | -  |        |    |        | Bi      | t Po | siti  | on |       |    |    |    |   | • |   |   |       |   |   |   |   |   |

|---------|-------|-------|--------|----|----------|----|----|----|----|----|----|--------|----|--------|---------|------|-------|----|-------|----|----|----|---|---|---|---|-------|---|---|---|---|---|

| 0x3C500 | 31    | 30    | 29     | 28 | 27       | 26 | 25 | 24 | 23 | 22 | 21 | 20     | 19 | 18     | 17      | 16   | 15    | 14 | 13    | 12 | 11 | 10 | 6 | ω | 7 | 9 | 5     | 4 | ю | 2 | - | 0 |

| Reset   | 0     | 0     | 0      |    | 00<br>×0 |    |    |    |    |    |    | nxn    |    | 0×0    | 0       |      | 0     |    | 0x0   |    |    |    |   |   |   |   | 0×000 |   |   |   |   |   |

| Access  | RW1H  | RW1H  | RW     |    |          |    | RW |    |    |    |    | ۶<br>۲ |    | RW     | RW      |      | RW    |    | RW    |    |    |    |   |   |   |   | RW    |   |   |   |   |   |

| Name    | CHENA | CHDIS | ODDFRM |    | DEVADDR  |    |    |    |    |    |    | MC     |    | ЕРТҮРЕ | LSPDDEV |      | EPDIR |    | EPNUM |    |    |    |   |   |   |   | MPS   |   |   |   |   |   |

| 31       | Name              | Reset                                                 | Access                | Description                                                                                                                                              |

|----------|-------------------|-------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | CHENA             | 0                                                     | RW1H                  | Channel Enable                                                                                                                                           |

|          | This field is set | t by the application and cl                           | eared by the core.    | The state of this bit reflects the channel enable status.                                                                                                |

| 30       | CHDIS             | 0                                                     | RW1H                  | Channel Disable                                                                                                                                          |

|          |                   |                                                       |                       | data on a channel, even before the transfer for that channel is complete.<br>of before treating the channel as disabled.                                 |

| 29       | ODDFRM            | 0                                                     | RW                    | Odd Frame                                                                                                                                                |

|          |                   | (reset) by the application ic (isochronous and interr |                       | OTG host must perform a transfer in an odd frame. This field is applicable                                                                               |

| 28:22    | DEVADDR           | 0x00                                                  | RW                    | Device Address                                                                                                                                           |

|          | This field selec  | ts the specific device ser                            | ving as the data so   | urce or sink.                                                                                                                                            |

| 21:20    | MC                | 0x0                                                   | RW                    | Multi Count                                                                                                                                              |

|          | endpoint. For I   |                                                       | s field is used only  | umber of transactions that must be executed per frame for this periodic $\prime$ in DMA mode, and specifies the number packets to be fetched for this n. |

| 19:18    | EPTYPE            | 0x0                                                   | RW                    | Endpoint Type                                                                                                                                            |

|          | Indicates the tr  | ansfer type selected.                                 |                       |                                                                                                                                                          |

|          | Value             | Mode                                                  | Des                   | scription                                                                                                                                                |

|          | 0                 | CONTROL                                               | Cor                   | ntrol endpoint.                                                                                                                                          |

|          | 1                 | ISO                                                   | Isoc                  | chronous endpoint.                                                                                                                                       |

|          | 2                 | BULK                                                  | Bull                  | k endpoint.                                                                                                                                              |

|          | 3                 | INT                                                   | Inte                  | errupt endpoint.                                                                                                                                         |

| 17       | LSPDDEV           | 0                                                     | RW                    | Low-Speed Device                                                                                                                                         |

|          | This field is set | t by the application to indi                          | cate that this chanr  | nel is communicating to a low-speed device.                                                                                                              |

|          | Reserved          | To ensure                                             | compatibility with fu | uture devices, always write bits to 0. More information in Section 2.1 (p. 3)                                                                            |

| 16       |                   | 10 0110410                                            |                       | aure devices, always write bits to 0. Wore information in Section 2.1 (p. 5)                                                                             |

| 16<br>15 | EPDIR             | 0                                                     | RW                    | Endpoint Direction                                                                                                                                       |

|          |                   |                                                       |                       |                                                                                                                                                          |

|          |                   | 0                                                     | or OUT.               |                                                                                                                                                          |

| Bit   | Name               | Reset                    | Access              | Description                                                                   |

|-------|--------------------|--------------------------|---------------------|-------------------------------------------------------------------------------|

| 31:16 | Reserved           | To ensure co             | ompatibility with f | uture devices, always write bits to 0. More information in Section 2.1 (p. 3) |

| 15:0  | SPCAVAIL           | 0x0200                   | R                   | TxFIFO Space Available                                                        |

|       | Indicates the amou | nt of free space availab | ole in the Endpoi   | nt TxFIFO. Values are in terms of 32-bit words.                               |

# 15.6.60 USB\_DOEP0CTL - Device OUT Endpoint 0 Control Register

The application uses this register to control the behavior of each logical endpoint other than endpoint 0.

| Offset  |            |                                                                                                                                                                                                                                                                                   |                 |               |                   |           |              |               |               |              |        |            |                                 | Bi     | it Po        | ositi                | on         |           |               |       |        | ,     |       |       |       |       |       |      |       |       |          |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|-------------------|-----------|--------------|---------------|---------------|--------------|--------|------------|---------------------------------|--------|--------------|----------------------|------------|-----------|---------------|-------|--------|-------|-------|-------|-------|-------|-------|------|-------|-------|----------|

| 0x3CB00 | 31         | 30                                                                                                                                                                                                                                                                                | 29              | 28            | 27                | 26        | 25           | 24            | 23            | 22           | 21     | 20         | 19 19                           | 17     | 16           | 15                   | 4          | 13        | 12            | 1     | 10     | 6     | ø     | 2     | - 4   | 2     | 4     | t (* | , c   | v ,   | - 0      |

| Reset   | 0          | 0                                                                                                                                                                                                                                                                                 |                 |               | 0                 | 0         |              |               |               |              | 0      | 0          | 0X0                             | 0      |              | ~                    |            |           |               |       |        |       |       |       |       |       |       |      |       |       | 0x0      |

| Access  | RW1H       | ĸ                                                                                                                                                                                                                                                                                 |                 |               | M1                | W1        |              |               |               |              | RW1H   | RW         | ĸ                               | ъ      |              | ĸ                    |            |           |               |       |        |       |       |       |       |       |       |      |       |       | ĸ        |

| Name    | EPENA      | EPDIS                                                                                                                                                                                                                                                                             |                 |               | SNAK              | CNAK      |              |               |               |              | STALL  | SNP        | ЕРТҮРЕ                          | NAKSTS |              | USBACTEP             |            |           |               |       |        |       |       |       |       |       |       |      |       |       | MPS      |

| Bit     | Na         | ime                                                                                                                                                                                                                                                                               |                 |               |                   |           |              | Re            | eset          |              |        | A          | ccess                           | ;      | De           | scr                  | ipti       | on        |               |       |        |       |       |       |       |       |       |      |       |       |          |

| 31      | EP         | ENA                                                                                                                                                                                                                                                                               | ١               |               |                   |           |              | 0             |               |              |        | R          | W1H                             |        | En           | dpoi                 | nt E       | Ena       | ble           |       |        |       |       |       |       |       |       |      |       |       |          |

|         | this       | s bit l                                                                                                                                                                                                                                                                           | befo            | re se         | etting            | , an      | y of         | the           | follo         | wing         | inte   | rrup       | n has a<br>ts on th<br>transfei | is er  | ated<br>ndpo | the r<br>int: S      | ner<br>SET | nor<br>UP | y to<br>' Pha | ase   | Don    | e, Er |       |       |       |       |       |      |       |       |          |

| 30      |            | DIS<br>s bit                                                                                                                                                                                                                                                                      | is al           | lway          | s 0. <sup>-</sup> | The       | ap           | 0<br>plica    | tion          | cann         | ot di  | R<br>isabl | e contr                         | ol O   |              | d <b>poi</b><br>ndpo |            |           | able          | !     |        |       |       |       |       |       |       |      |       |       |          |

| 29:28   | Re         | Reserved To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p                                                                                                                                                                  |                 |               |                   |           |              |               |               |              |        |            |                                 |        |              | 1 (p. 3)             |            |           |               |       |        |       |       |       |       |       |       |      |       |       |          |

| 27      | SN         |                                                                                                                                                                                                                                                                                   |                 |               |                   |           |              |               |               |              |        |            |                                 |        |              |                      |            |           |               |       |        |       |       |       |       |       |       |      |       |       |          |

|         |            | SNAK0W1Set NAKA write to this bit sets the NAK bit for the endpoint. Using this bit, the application can control the transmission of NAK handshakes<br>on an endpoint. The core can also set bit on a Transfer Completed interrupt, or after a SETUP is received on the endpoint. |                 |               |                   |           |              |               |               |              |        |            |                                 |        |              |                      |            |           |               |       |        |       |       |       |       |       |       |      |       |       |          |

| 26      | CN         | AK                                                                                                                                                                                                                                                                                |                 |               |                   |           |              | 0             |               |              |        | W          | /1                              |        | Cle          | ar N                 | IAK        |           |               |       |        |       |       |       |       |       |       |      |       |       |          |

|         | Αv         | vrite                                                                                                                                                                                                                                                                             | to th           | nis bi        | t clea            | ars       | the          | NAK           | (bit f        | for th       | e er   | idpo       | int.                            |        |              |                      |            |           |               |       |        |       |       |       |       |       |       |      |       |       |          |

| 25:22   | Re         | serv                                                                                                                                                                                                                                                                              | ed              |               |                   |           |              | То            | ens           | ure c        | omp    | atib       | ility with                      | n futu | ire d        | evice                | es, a      | alw       | ays           | write | bits   | to 0  | . Mo  | re ir | nfori | mati  | on ir | n Se | ctior | n 2.1 | 1 (p. 3) |

| 21      | ST         | ALL                                                                                                                                                                                                                                                                               |                 |               |                   |           |              | 0             |               |              |        | R          | W1H                             |        | Ha           | ndsł                 | nake       | е         |               |       |        |       |       |       |       |       |       |      |       |       |          |

|         | OU         | T N                                                                                                                                                                                                                                                                               | AK is           |               | alor              | ig v      | ith 1        | this I        | oit, th       | ne S         |        |            | clears<br>takes p               |        |              |                      |            |           |               |       |        |       |       |       |       |       |       |      |       |       |          |

| 20      | SN         | Ρ                                                                                                                                                                                                                                                                                 |                 |               |                   |           |              | 0             |               |              |        | R          | W                               |        | Sn           | оор                  | Мо         | de        |               |       |        |       |       |       |       |       |       |      |       |       |          |

|         |            |                                                                                                                                                                                                                                                                                   |                 | figur<br>then |                   |           |              |               |               |              | o mo   | ode.       | In Sno                          | op m   | node         | , the                | cor        | re o      | loes          | not   | che    | ck tł | ne co | orreo | ctne  | iss c | of Ol | UT p | back  | ets   | before   |

| 19:18   | EP         | TYP                                                                                                                                                                                                                                                                               | Έ               |               |                   |           |              | 0x0           | )             |              |        | R          |                                 |        | En           | dpoi                 | nt T       | Гур       | е             |       |        |       |       |       |       |       |       |      |       |       |          |

|         | На         | rdco                                                                                                                                                                                                                                                                              | ded             | to 0.         | End               | lpoi      | nt 0         | is a          | lway          | sac          | ontr   | ol er      | ndpoint.                        |        |              |                      |            |           |               |       |        |       |       |       |       |       |       |      |       |       |          |

| 17      | NA         | KST                                                                                                                                                                                                                                                                               | S               |               |                   |           |              | 0             |               |              |        | R          |                                 |        | NA           | K St                 | atu        | s         |               |       |        |       |       |       |       |       |       |      |       |       |          |

|         | NA<br>is s | K ha<br>space                                                                                                                                                                                                                                                                     | andsl<br>e in 1 | hake          | s on<br>RxFII     | thi<br>FO | s er<br>to a | ndpo<br>Iccor | int. V<br>nmo | Nher<br>date | n eith | ner t      | < hands<br>he appl<br>ming pa   | icati  | on o         | r the                | cor        | re s      | ets           | this  | bit, t | he c  | ore   | stop  | os re | eceiv | ving  | data | a, ev | en i  | f there  |

| 16      | Re         | serv                                                                                                                                                                                                                                                                              | ed              |               |                   |           |              | То            | ens           | ure c        | omp    | atib       | ility with                      | n futu | ire d        | evice                | es, a      | alw       | ays           | write | bits   | to 0  | . Mo  | re ir | nfori | mati  | on ir | n Se | ctior | n 2.1 | 1 (p. 3) |

| 15      | US         | BAC                                                                                                                                                                                                                                                                               | TEF             | 5             |                   |           |              | 1             |               |              |        | R          |                                 |        | US           | B Ad                 | ctive      | e E       | ndp           | oint  |        |       |       |       |       |       |       |      |       |       |          |

|         | Thi        | s bit                                                                                                                                                                                                                                                                             | is al           | lway          | s 1, i            | indi      | catii        | ng th         | at a          | cont         | rol e  | ndp        | oint 0 is                       | s alw  | ays          | activ                | re in      | all       | con           | figu  | ratio  | ns a  | nd ir | terf  | ace   | s.    |       |      |       |       |          |

| Offset  |    |    |    |    |    |    |    |    |     |    |    |    |    |     | Di |         | oiti | - III |    |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---------|----|----|----|----|----|----|----|----|-----|----|----|----|----|-----|----|---------|------|-------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Unset   |    |    | 1  |    |    |    |    | -  |     |    | 1  |    |    |     | DI | t Po    | siti | on    |    |   | 1 |   |   |   |   |   |   |   |   |   |   |   |

| 0x49000 | 3  | 8  | 29 | 28 | 27 | 26 | 25 | 24 | 53  | 52 | 21 | 20 | 19 | 18  | 17 | 16      | 15   | 4     | 13 | 5 | 7 | 9 | 6 | œ | ~ | 9 | 2 | 4 | e | 2 | ~ | 0 |

| Reset   |    |    |    |    |    |    |    | ,  |     |    |    |    |    |     |    | *****   |      |       |    |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Access  |    |    |    |    |    |    |    |    |     |    |    |    |    |     |    | МЯ      |      |       |    |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Name    |    |    |    |    |    |    |    |    |     |    |    |    |    |     |    | EIEO12D |      |       |    |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Bit     | Na | me |    |    |    |    |    | Re | set |    |    | Δ  |    | 222 |    | De      | scri | intic | n  |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Bit  | Name                     | Reset              | Access | Description          |

|------|--------------------------|--------------------|--------|----------------------|

| 31:0 | FIFO12D                  | 0xXXXXXXXX         | RW     | Host Channel 12 FIFO |

|      | FIFO 12 push/pop region. | Used in slave mode | е.     |                      |

# 15.6.82 USB\_FIFO13Dx - Host Channel 13 FIFO

This register, available in Host mode, is used to read or write the FIFO space for channel 13, in a given direction. If a host channel is of type IN, the FIFO can only be read on the channel. Similarly, if a host channel is of type OUT, the FIFO can only be written on the channel.

| Offset      |    |         |    |    |          |          |    |    |    |    |    |    |     |    | Bi | t Po                                    | siti | on |    |    |   |    |   |   | ÷ |   |   |   |   |   |   |   |

|-------------|----|---------|----|----|----------|----------|----|----|----|----|----|----|-----|----|----|-----------------------------------------|------|----|----|----|---|----|---|---|---|---|---|---|---|---|---|---|

|             |    |         | 1  | 1  | <u> </u> | <u> </u> |    | 1  |    |    |    |    | 1 1 |    | 1  | 1                                       |      | 1  |    |    | 1 | 1  |   |   |   |   |   |   |   | 1 |   |   |

| 0x4A000     | 31 | 30      | 29 | 28 | 27       | 26       | 25 | 24 | 23 | 22 | 21 | 20 | 19  | 18 | 17 | 16                                      | 15   | 4  | 13 | 12 | 7 | 10 | 6 | 8 | 2 | 9 | 5 | 4 | ю | 2 | - | 0 |

| Reset       |    |         |    |    |          |          |    |    |    |    |    |    |     |    |    | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |      |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| Access      |    |         |    |    |          |          |    |    |    |    |    |    |     |    |    | 1010                                    |      |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| Name        |    | FIFO13D |    |    |          |          |    |    |    |    |    |    |     |    |    |                                         |      |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

|             |    |         |    |    |          |          |    |    |    |    |    |    |     |    |    |                                         |      |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| <b>D</b> 14 |    |         |    |    |          |          |    |    |    |    |    |    |     |    |    |                                         |      |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| Bit  | Name                                         | Reset      | Access | Description          |  |  |  |

|------|----------------------------------------------|------------|--------|----------------------|--|--|--|

| 31:0 | FIFO13D                                      | 0xXXXXXXXX | RW     | Host Channel 13 FIFO |  |  |  |

|      | FIFO 13 push/pop region. Used in slave mode. |            |        |                      |  |  |  |

When enabling the  $I^2C$ , the ABORT command or the Bus Idle Timeout feature must be applied prior to use even if the BUSY flag is not set.

# 16.3.3 Safely Disabling and Changing Slave Configuration

The I<sup>2</sup>C slave is partially asynchronous, and some precautions are necessary to always ensure a safe slave disable or slave configuration change. These measures should be taken, if (while the slave is enabled) the user cannot guarantee that an address match will not occur at the exact time of slave disable or slave configuration change.

Worst case consequences for an address match while disabling slave or changing configuration is that the slave may end up in an undefined state. To reset the slave back to a known state, the EN bit in I2Cn\_CTRL must be reset. This should be done regardless of whether the slave is going to be re-enabled or not.

## **16.3.4 Clock Generation**

The SCL signal generated by the  $I^2C$  master determines the maximum transmission rate on the bus. The clock is generated as a division of the peripheral clock, and is given by Equation 16.2 (p. 420) :

## f<sup>2</sup>C Maximum Transmission Rate

$$f_{SCL} = 1/(T_{low} + T_{high}), \qquad (16.2)$$

where

$T_{low}$  and  $T_{high}$  is the low and high periods of the clock signal respectively, given below. When the clock is not streched, the low and high periods of the clock signal are:

## <sup>2</sup>C High and Low Cycles Equations

$$\Gamma_{high} = (N_{high} \times (CLKDIV + 1))/f_{HFPERCLK},$$

$$T_{low} = (N_{low} \times (CLKDIV + 1))/f_{HFPERCLK}.$$

(16.3)

Equation 16.3 (p. 420) and Equation 16.2 (p. 420) does not apply for low clock division factors (0, 1 and 2) because of synchronization. For these clock division factors, the formulas for computing high and low periods of the clock signal are given in Table 16.2 (p. 420).

| CLKDIV | Standard (4:4)           |                          | Asymmetric (6:3          | )                        | Fast (11:6)              |                          |  |

|--------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--|

|        | T <sub>low</sub>         | T <sub>high</sub>        | T <sub>low</sub>         | T <sub>high</sub>        | T <sub>low</sub>         | T <sub>high</sub>        |  |

| 0      | 7/f <sub>HFPERCLK</sub>  | 7/f <sub>HFPERCLK</sub>  | 9/f <sub>HFPERCLK</sub>  | 6/f <sub>HFPERCLK</sub>  | 14/f <sub>HFPERCLK</sub> | 9/f <sub>HFPERCLK</sub>  |  |

| 1      | 10/f <sub>HFPERCLK</sub> | 10/f <sub>HFPERCLK</sub> | 14/f <sub>HFPERCLK</sub> | 8/f <sub>HFPERCLK</sub>  | 24/f <sub>HFPERCLK</sub> | 14/f <sub>HFPERCLK</sub> |  |

| 2      | 15/f <sub>HFPERCLK</sub> | 15/f <sub>HFPERCLK</sub> | 21/f <sub>HFPERCLK</sub> | 12/f <sub>HFPERCLK</sub> | 36/f <sub>HFPERCLK</sub> | 21/f <sub>HFPERCLK</sub> |  |

The values of N<sub>low</sub> and N<sub>high</sub> and thus the ratio between the high and low parts of the clock signal is controlled by CLHR in the I2Cn\_CTRL register. The available modes are summarized in Table 16.3 (p. 421) along with the highest I<sup>2</sup>C-bus frequencies in the given modes that can be achieved without violating the timing specifications of the I<sup>2</sup>C-bus. The maximum data hold time is dependent on the DIV and is given by:

## Maximum Data Hold Time

$$t_{HD,DAT-max} = (4+DIV)/f_{HFPERCLK}$$

Note

DIV must be set to 1 or higher during slave mode operation.

(16.4)

| Bit   | Name                                                                                                               | Reset                                                                                                                                                                   | Access                                                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | When set, the                                                                                                      | bus automatically goes id                                                                                                                                               | le on a bus idle tim                                                                                                                                       | eout, allowing new transfers to be initiated.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|       | Value                                                                                                              | Description                                                                                                                                                             | Description                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|       | 0                                                                                                                  | A bus idle time                                                                                                                                                         | out has no effect on th                                                                                                                                    | e bus state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|       | 1                                                                                                                  | A bus idle time                                                                                                                                                         | out tells the I <sup>2</sup> C modu                                                                                                                        | e that the bus is idle, allowing new transfers to be initiated.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 14    | Reserved                                                                                                           | To ensure                                                                                                                                                               | compatibility with fu                                                                                                                                      | ture devices, always write bits to 0. More information in Section 2.1 (p. 3                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|       |                                                                                                                    |                                                                                                                                                                         |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 3:12  | BITO<br>Use to generat<br>bus transaction<br>by BITO, it sets<br>idle timeout is<br>STOP condition                 | 0x0<br>te a timeout when SCL h<br>h, i.e. the BUSY flag is s<br>s the BITO interrupt flag.<br>active as long as BUSY<br>n is detected and when th                       | RW<br>as been high for a<br>et, a timer is starte<br>The BITO interrup<br>is set. It is thus st                                                            | Bus Idle Timeout<br>given amount time between a START and STOP condition. When ir<br>d whenever SCL goes high. When the timer reaches the value defin<br>flag will then be set periodically as long as SCL remains high. The b<br>opped automatically on a timeout if GIBITO is set. It is also stopped                                                                                                                                                                                                |  |  |  |  |  |

| 13:12 | BITO<br>Use to generat<br>bus transactior<br>by BITO, it sets<br>idle timeout is<br>STOP condition<br>a START cond | 0x0<br>te a timeout when SCL h<br>h, i.e. the BUSY flag is s<br>s the BITO interrupt flag.<br>active as long as BUSY<br>n is detected and when th<br>ition is detected. | RW<br>as been high for a<br>et, a timer is starte<br>The BITO interrup<br>is set. It is thus st<br>he ABORT comma                                          | Bus Idle Timeout<br>given amount time between a START and STOP condition. When in<br>d whenever SCL goes high. When the timer reaches the value define<br>flag will then be set periodically as long as SCL remains high. The b<br>opped automatically on a timeout if GIBITO is set. It is also stopped<br>id is issued. The timeout is activated whenever the bus goes BUSY, i.                                                                                                                      |  |  |  |  |  |