Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB           |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                            |

| Number of I/O              | 93                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                               |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 120-VFBGA                                                                  |

| Supplier Device Package    | 120-BGA (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg995f512g-e-bga120 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Timers/Counters

- 4x 16-bit Timer/Counter

- 3 Compare/Capture/PWM channels

- Dead-Time Insertion on TIMER0

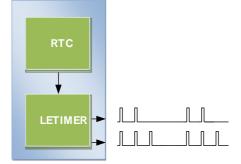

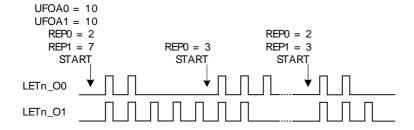

- 16-bit Low Energy Timer

- 1x 24-bit and 1x 32-bit Real-Time Counter

- 3× 8/16-bit Pulse Counter

- Asynchronous pulse counting/quadrature decoding

- Watchdog Timer with dedicated RC oscillator @ 50 nA

- Backup Power Domain

- RTC and retention registers in a separate power domain, available in all energy modes

- Operation from backup battery when main power drains out

- Ultra low power precision analog peripherals

- 12-bit 1 Msamples/s Analog to Digital Converter

- 8 input channels and on-chip temperature sensor

- Single ended or differential operation

- Conversion tailgating for predictable latency

- 12-bit 500 ksamples/s Digital to Analog Converter

- 2 single ended channels/1 differential channel

- Up to 3 Operational Amplifiers

- Supports rail-to-rail inputs and outputs

- Programmable gain

- 2× Analog Comparator

- Programmable speed/current

- · Capacitive sensing with up to 8 inputs

- · Supply Voltage Comparator

- Ultra low power sensor interface

- Autonomous sensor monitoring in Deep Sleep Mode

- Wide range of sensors supported, including LC sensors and capacitive buttons

### 3.3.2 System Features

- Ultra efficient Power-on Reset and Brown-Out Detector

- Debug Interface

- 2-pin Serial Wire Debug interface

- 1-pin Serial Wire Viewer

- Embedded Trace Module v3.5 (ETM)

- Temperature range -40 85°C

- Single power supply 1.98 3.8 V

- Packages

- QFN64

- TQFP64

- LQFP100

- LFBGA112

- VFBGA120

- Full wafer

# 3.4 Energy Modes

There are five different Energy Modes (EM0-EM4) in the EFM32GG, see Table 3.1 (p. 8). The EFM32GG is designed to achieve a high degree of autonomous operation in low energy modes. The intelligent combination of peripherals, RAM with data retention, DMA, low-power oscillators, and short

- Minimum 20 000 erase cycles

- More than 10 years data retention at 85°C

- Lock-bits for memory protection

- Data retention in any state

# **5.5 SRAM**

The primary task of the SRAM memory is to store application data. Additionally, it is possible to execute instructions from SRAM, and the DMA may used to transfer data between the SRAM, Flash and peripherals.

- Up to 128 kB memory

- Bit-band access support

- 32 kB blocks may be individually powered down when not in use

- Data retention of the entire memory in EM0 to EM3

# 5.6 Device Information (DI) Page

The DI page contains calibration values, a unique identification number and other useful data. See the table below for a complete overview.

#### Table 5.4. Device Information Page Contents

| DI Address | Register          | Description                                                        |

|------------|-------------------|--------------------------------------------------------------------|

| 0x0FE08020 | CMU_LFRCOCTRL     | Register reset value.                                              |

| 0x0FE08028 | CMU_HFRCOCTRL     | Register reset value.                                              |

| 0x0FE08030 | CMU_AUXHFRCOCTRL  | Register reset value.                                              |

| 0x0FE08040 | ADC0_CAL          | Register reset value.                                              |

| 0x0FE08048 | ADC0_BIASPROG     | Register reset value.                                              |

| 0x0FE08050 | DAC0_CAL          | Register reset value.                                              |

| 0x0FE08058 | DAC0_BIASPROG     | Register reset value.                                              |

| 0x0FE08060 | ACMP0_CTRL        | Register reset value.                                              |

| 0x0FE08068 | ACMP1_CTRL        | Register reset value.                                              |

| 0x0FE08078 | CMU_LCDCTRL       | Register reset value.                                              |

| 0x0FE080A0 | DAC0_OPACTRL      | Register reset value.                                              |

| 0x0FE080A8 | DAC0_OPAOFFSET    | Register reset value.                                              |

| 0x0FE080B0 | EMU_BUINACT       | Register reset value.                                              |

| 0x0FE080B8 | EMU_BUACT         | Register reset value.                                              |

| 0x0FE080C0 | EMU_BUBODBUVINCAL | Register reset value.                                              |

| 0x0FE080C8 | EMU_BUBODUNREGCAL | Register reset value.                                              |

| 0x0FE081B0 | DI_CRC            | [15:0]: DI data CRC-16.                                            |

| 0x0FE081B2 | CAL_TEMP_0        | [7:0] Calibration temperature (°C).                                |

| 0x0FE081B4 | ADC0_CAL_1V25     | [14:8]: Gain for 1V25 reference, [6:0]: Offset for 1V25 reference. |

| 0x0FE081B6 | ADC0_CAL_2V5      | [14:8]: Gain for 2V5 reference, [6:0]: Offset for 2V5 reference.   |

| Bit   | Name                   | Reset                      | Access            | Description                                                                                                                                 |

|-------|------------------------|----------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 31:17 | Reserved               | To ensure c                | ompatibility with | future devices, always write bits to 0. More information in Section 2.1 (p. 3)                                                              |

| 16    | PERIOD                 | 0                          | RW                | Sets the timebase period                                                                                                                    |

|       | Decides wheth<br>band. | ner TIMEBASE specifies the | e number of AUX   | Cycles in 1 us or 5 us. 5 us should only be used with 1 MHz AUXHFRCO                                                                        |

|       | Value                  | Mode                       | De                | escription                                                                                                                                  |

|       | 0                      | 1US                        | TI                | MEBASE period is 1 us.                                                                                                                      |

|       | 1                      | 5US                        | TI                | MEBASE period is 5 us.                                                                                                                      |

| 15:6  | Reserved               | To ensure c                | ompatibility with | future devices, always write bits to 0. More information in Section 2.1 (p. 3)                                                              |

| 5:0   | BASE                   | 0x10                       | RW                | Timebase used by MSC to time flash writes and erases                                                                                        |

|       |                        |                            |                   | he period given by MSC_TIMEBASE_PERIOD. I.e. 1.1 us or 5.5. us with<br>e timebase matches a 14 MHz AUXHFRCO, which is the default frequency |

of the AUXHFRCO.

# 7.5.17 MSC\_MASSLOCK - Mass Erase Lock Register

| Offset |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Bi | t Po | siti | on |    |    |    |    |   | . <u> </u> |        |   |   |   |   |   |   |   |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|------|----|----|----|----|----|---|------------|--------|---|---|---|---|---|---|---|

| 0x054  | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16   | 15   | 14 | 13 | 12 | 11 | 10 | 6 | 8          | 7      | 9 | 5 | 4 | с | 2 | - | 0 |

| Reset  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |   | 100000     | INNNN  |   |   |   |   |   |   |   |

| Access |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |   |            | 2<br>2 |   |   |   |   |   |   |   |

| Name   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |   |            |        |   |   |   |   |   |   |   |

| Bit   | Name     | Reset         | Access            | Description                                                                    |

|-------|----------|---------------|-------------------|--------------------------------------------------------------------------------|

| 31:16 | Reserved | To ensure com | patibility with i | future devices, always write bits to 0. More information in Section 2.1 (p. 3) |

| 15:0  | LOCKKEY  | 0x0001        | RW                | Mass Erase Lock                                                                |

Write any other value than the unlock code to lock access the the ERASEMAIN0 and ERASEMAIN1 commands. Write the unlock code 631A to enable access. When reading the register, bit 0 is set when the lock is enabled. Locked by default.

| Mode            | Value  | Description          |

|-----------------|--------|----------------------|

| Read Operation  |        |                      |

| UNLOCKED        | 0      | Mass erase unlocked. |

| LOCKED          | 1      | Mass erase locked.   |

| Write Operation |        |                      |

| LOCK            | 0      | Lock mass erase.     |

| UNLOCK          | 0x631A | Unlock mass erase.   |

| Bit | Name                 | Reset                  | Access               | Description                                                                                       |

|-----|----------------------|------------------------|----------------------|---------------------------------------------------------------------------------------------------|

| 5   | CHPROT               | 0                      | W                    | Channel Protection Control                                                                        |

|     |                      |                        |                      | rivileged or not. When CHPROT = 1 then HPROT is HIGH and the access the access is non-privileged. |

| 4:1 | Reserved             | To ensure co           | ompatibility with fu | ture devices, always write bits to 0. More information in Section 2.1 (p. 3)                      |

| 0   | EN                   | 0                      | W                    | Enable DMA                                                                                        |

|     | Set this bit to enab | le the DMA controller. |                      |                                                                                                   |

# 8.7.3 DMA\_CTRLBASE - Channel Control Data Base Pointer Register

|        | - <u>r</u> |        |       |    |    |    |    |     |               |      |    |    |     |     |    |      |            |       |     |       |      |     |       |       |    |   |   |   |   |   |   |               |

|--------|------------|--------|-------|----|----|----|----|-----|---------------|------|----|----|-----|-----|----|------|------------|-------|-----|-------|------|-----|-------|-------|----|---|---|---|---|---|---|---------------|

| Offset |            |        |       |    |    |    |    |     |               |      |    |    |     |     | Bi | t Po | siti       | on    |     |       |      |     |       |       |    |   |   |   |   |   |   |               |

| 0x008  | 31         | 30     | 29    | 28 | 27 | 26 | 25 | 24  | 23            | 22   | 21 | 20 | 19  | 18  | 17 | 16   | 15         | 4     | 13  | 12    | 7    | 10  | ი     | 8     | 2  | 9 | 5 | 4 | e | 2 | - | 0             |

| Reset  |            |        |       |    |    |    |    |     |               |      |    |    |     |     |    |      |            |       |     |       |      |     |       |       |    |   |   |   |   |   |   |               |

| Access |            | α<br>α |       |    |    |    |    |     |               |      |    |    |     |     |    |      |            |       |     |       |      |     |       |       |    |   |   |   |   |   |   |               |

| Name   |            |        |       |    |    |    |    |     |               |      |    |    |     |     |    |      | U I NEDAGE |       |     |       |      |     |       |       |    |   |   |   |   |   |   |               |

| Bit    | Na         | ime    |       |    |    |    |    | Re  | set           |      |    | A  | CCe | ess |    | De   | scri       | iptio | on  |       |      |     |       |       |    |   |   |   |   |   |   |               |

| 31:0   | СТ         | RLB.   | ASE   |    |    |    |    | 0x0 | 0000          | 0000 | )  | R  | W   |     |    | Ch   | anne       | el Co | ont | rol [ | Data | Bas | se Po | ointe | ər |   |   |   |   |   |   |               |

|        | to a       |        | atior |    |    |    |    |     | n sys<br>with |      |    |    |     |     |    |      |            |       |     |       |      |     |       |       |    |   |   |   |   |   |   | oint<br>[8:0] |

# 8.7.4 DMA\_ALTCTRLBASE - Channel Alternate Control Data Base Pointer Register

| Offset |     |          |      |    |    |    |     |      |      |    |    |     |     | Bi | t Po       | ositi       | on     |     |      |     |      |      |       |     |     |      |   |   |   |   |   |

|--------|-----|----------|------|----|----|----|-----|------|------|----|----|-----|-----|----|------------|-------------|--------|-----|------|-----|------|------|-------|-----|-----|------|---|---|---|---|---|

| 0x00C  | 31  | 30<br>29 | 28   | 27 | 26 | 25 | 24  | 23   | 22   | 21 | 20 | 19  | 18  | 17 | 16         | 15          | 14     | 13  | 12   | 7   | 10   | ი    | 8     | 7   | 9   | 5    | 4 | e | 7 | - | 0 |

| Reset  |     |          |      |    |    |    |     |      |      |    |    |     |     |    | 0010000000 |             |        |     |      |     |      |      |       |     |     |      |   |   |   |   |   |

| Access |     |          |      |    |    |    |     |      |      |    |    |     |     |    | ۵          | Ľ           |        |     |      |     |      |      |       |     |     |      |   |   |   |   |   |

| Name   |     |          |      |    |    |    |     |      |      |    |    |     |     |    |            | ALICINERASE |        |     |      |     |      |      |       |     |     |      |   |   |   |   |   |

| Bit    | Na  | me       |      |    |    |    | Re  | set  |      |    | A  | CCe | ess |    | De         | scri        | ptic   | on  |      |     |      |      |       |     |     |      |   |   |   |   |   |

| 31:0   | ALT | CTRLE    | BASE |    |    |    | 0x0 | 0000 | 0100 | )  | R  |     |     |    | Ch         | anne        | el Alt | ter | nate | Cor | ntro | l Da | ta Ba | ase | Poi | nter |   |   |   |   |   |

# 8.7.10 DMA\_CHREQMASKC - Channel Request Mask Clear Register

| Offset |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Bi | t Po | ositi | on |    |    |              |              |             |             |             |             |             |                    |             |             |                    |             |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|-------|----|----|----|--------------|--------------|-------------|-------------|-------------|-------------|-------------|--------------------|-------------|-------------|--------------------|-------------|

| 0x024  | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16   | 15    | 14 | 13 | 12 | 1            | 10           | 6           | 8           | 7           | 9           | 5           | 4                  | e           | 2           | -                  | 0           |

| Reset  |    |    |    | ·  |    |    |    |    |    |    |    |    |    | ·  |    | ·    |       |    |    |    | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0                  | 0           | 0           | 0                  | 0           |

| Access |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |      |       |    |    |    | W1           | W1           | W1          | W1          | W1          | W1          | W1          | W1                 | W1          | W1          | W1                 | W1          |

| Name   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |      |       |    |    |    | CH11REQMASKC | CH10REQMASKC | CH9REQMASKC | CHBREQMASKC | CH7REQMASKC | CH6REQMASKC | CH5REQMASKC | <b>CH4REQMASKC</b> | CH3REQMASKC | CH2REQMASKC | <b>CH1REQMASKC</b> | CHOREQMASKC |

| Bit   | Name                     | Reset              | Access                 | Description                                                                  |

|-------|--------------------------|--------------------|------------------------|------------------------------------------------------------------------------|

| 31:12 | Reserved                 | To ensure o        | compatibility with fut | ture devices, always write bits to 0. More information in Section 2.1 (p. 3) |

| 11    | CH11REQMASKC             | 0                  | W1                     | Channel 11 Request Mask Clear                                                |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

| 10    | CH10REQMASKC             | 0                  | W1                     | Channel 10 Request Mask Clear                                                |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

| 9     | CH9REQMASKC              | 0                  | W1                     | Channel 9 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

| 8     | CH8REQMASKC              | 0                  | W1                     | Channel 8 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

| 7     | CH7REQMASKC              | 0                  | W1                     | Channel 7 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

| 6     | CH6REQMASKC              | 0                  | W1                     | Channel 6 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

| 5     | CH5REQMASKC              | 0                  | W1                     | Channel 5 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

| 4     | CH4REQMASKC              | 0                  | W1                     | Channel 4 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | or this channel.       |                                                                              |

| 3     | CH3REQMASKC              | 0                  | W1                     | Channel 3 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

| 2     | CH2REQMASKC              | 0                  | W1                     | Channel 2 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | or this channel.       |                                                                              |

| 1     | CH1REQMASKC              | 0                  | W1                     | Channel 1 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | or this channel.       |                                                                              |

| 0     | CHOREQMASKC              | 0                  | W1                     | Channel 0 Request Mask Clear                                                 |

|       | Write to 1 to enable per | ipheral requests f | for this channel.      |                                                                              |

### ...the world's most energy friendly microcontrollers

| Bit | Name               | Reset                        | Access            | Description                         |  |

|-----|--------------------|------------------------------|-------------------|-------------------------------------|--|

|     | Write to 1 to obta | in high priority for this ch | annel. Reading re | eturns the channel priority status. |  |

| 1   | CH1PRIS            | 0                            | RW1               | Channel 1 High Priority Set         |  |

|     | Write to 1 to obta | in high priority for this ch | annel. Reading re | eturns the channel priority status. |  |

| 0   | CHOPRIS            | 0                            | RW1               | Channel 0 High Priority Set         |  |

|     | Write to 1 to obta | in high priority for this ch | annel. Reading re | eturns the channel priority status. |  |

# 8.7.16 DMA\_CHPRIC - Channel Priority Clear Register

| Offset | Bit Position                                                                                            |          |          |         |         |         |         |         |         |         |         |         |         |

|--------|---------------------------------------------------------------------------------------------------------|----------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0x03C  | 31<br>30<br>30<br>229<br>228<br>225<br>225<br>224<br>221<br>19<br>19<br>117<br>117<br>117<br>113<br>113 | 7        | 10       | 6       | ω       | 7       | 9       | 5       | 4       | ю       | 7       | -       | 0       |

| Reset  |                                                                                                         | 0        | 0        | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Access |                                                                                                         | W1       | W1       | W1      | W1      | W1      | W1      | W1      | W1      | W1      | W1      | W1      | W1      |

| Name   |                                                                                                         | CH11PRIC | CH10PRIC | CH9PRIC | CH8PRIC | CH7PRIC | CH6PRIC | CH5PRIC | CH4PRIC | CH3PRIC | CH2PRIC | CH1PRIC | CHOPRIC |

| Bit   | Name                  | Reset                      | Access              | Description                                                                  |

|-------|-----------------------|----------------------------|---------------------|------------------------------------------------------------------------------|

| 31:12 | Reserved              | To ensure co               | mpatibility with fu | ture devices, always write bits to 0. More information in Section 2.1 (p. 3) |

| 11    | CH11PRIC              | 0                          | W1                  | Channel 11 High Priority Clear                                               |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 10    | CH10PRIC              | 0                          | W1                  | Channel 10 High Priority Clear                                               |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 9     | CH9PRIC               | 0                          | W1                  | Channel 9 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 8     | CH8PRIC               | 0                          | W1                  | Channel 8 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 7     | CH7PRIC               | 0                          | W1                  | Channel 7 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 6     | CH6PRIC               | 0                          | W1                  | Channel 6 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 5     | CH5PRIC               | 0                          | W1                  | Channel 5 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 4     | CH4PRIC               | 0                          | W1                  | Channel 4 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 3     | CH3PRIC               | 0                          | W1                  | Channel 3 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 2     | CH2PRIC               | 0                          | W1                  | Channel 2 High Priority Clear                                                |

|       | Write to 1 to clear I | high priority for this cha | nnel.               |                                                                              |

| 1     | CH1PRIC               | 0                          | W1                  | Channel 1 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| 0     | CH0PRIC               | 0                          | W1                  | Channel 0 High Priority Clear                                                |

|       | Write to 1 to clear I | nigh priority for this cha | nnel.               |                                                                              |

| Bit | Name             | Reset                    | Acce     | ss Description                                                                       |

|-----|------------------|--------------------------|----------|--------------------------------------------------------------------------------------|

|     | Value            | Mode                     |          | Description                                                                          |

|     | 6                | DIV64                    |          | Voltage Boost update Frequency = LFACLK/64.                                          |

|     | 7                | DIV128                   |          | Voltage Boost update Frequency = LFACLK/128.                                         |

| 3   | VBOOSTEN         | 0                        | RW       | Voltage Boost Enable                                                                 |

|     | This bit enables | /disables the VBOOST f   | unction. |                                                                                      |

| 2:0 | FDIV             | 0x0                      | RW       | Frame Rate Control                                                                   |

|     |                  | ols the framerate accord |          | nula: $LFACLK_{LCD} = LFACLK_{LCDpre} / (1 + FDIV)$ . Do not change this value while |

# 11.5.27 CMU\_ROUTE - I/O Routing Register

| Offset |   |        |        |      |       |      |       |        |       |       |      |        |         |      | В      | it Po   | ositi | on    |     |      |       |      |       |     |       |     |       |      |          |       |                   |            |

|--------|---|--------|--------|------|-------|------|-------|--------|-------|-------|------|--------|---------|------|--------|---------|-------|-------|-----|------|-------|------|-------|-----|-------|-----|-------|------|----------|-------|-------------------|------------|

| 0x080  | 5 | 8      | 29     | 28   | 27    | 26   | 25    | 24     | 23    | 52    | 21   | 20     | 19      | 18   | 17     | 16      | 15    | 4     | 13  | 12   | 1     | 10   | ი     | 8   | 7     | 9   | 5     | 4    | e        | 2     | -                 | 0          |

| Reset  |   |        |        |      |       |      |       |        |       |       |      |        |         |      |        |         |       |       | ·   |      |       |      |       |     |       |     |       |      | 0x0      | ,     | 0                 | 0          |

| Access |   |        |        |      | -     |      |       |        |       |       |      |        |         |      |        |         |       |       |     |      |       |      |       |     |       |     |       |      | RW       |       | RW                | RW         |

| Name   |   |        |        |      |       |      |       |        |       |       |      |        |         |      |        |         |       |       |     |      |       |      |       |     |       |     |       |      | LOCATION |       | <b>CLKOUT1PEN</b> | CLKOUT0PEN |

| Bit    | 1 | lame   | 1      |      |       |      |       | Re     | eset  |       |      | А      | CCE     | 955  | 5      | De      | escr  | iptio | on  |      |       |      |       |     |       |     |       |      |          |       |                   |            |

| 31:5   | F | Reserv | red    |      |       |      |       | То     | ens   | ure d | comp | oatibi | ility v | with | h futu | ıre d   | evice | es, a | lwa | ys v | vrite | bits | to 0. | Mor | e inf | orm | natio | n in | Sect     | ion 2 | 2.1 (p            | o. 3)      |

| 4:2    | L | OCAT   | ION    |      |       |      |       | 0x0    | )     |       |      | R      | W       |      |        | I/O     | Loc   | atio  | n   |      |       |      |       |     |       |     |       |      |          |       |                   |            |

|        | D | ecide  | s the  | loca | ation | of t | the ( | СМС    | J I/O | pins  | i.   |        |         |      |        |         |       |       |     |      |       |      |       |     |       |     |       |      |          |       |                   |            |

|        | ` | /alue  |        |      | N     | lode |       |        |       |       |      |        |         | [    | Descr  | riptior | ۱     |       |     |      |       |      |       |     |       |     |       |      |          |       |                   |            |

|        | 0 | )      |        |      | L     | 000  | )     |        |       |       |      |        |         | L    | Locat  | ion 0   |       |       |     |      |       |      |       |     |       |     |       |      |          |       |                   |            |

|        | Ľ | 1      |        |      | L     | OC1  |       |        |       |       |      |        |         | L    | Locat  | ion 1   |       |       |     |      |       |      |       |     |       |     |       |      |          |       |                   |            |

|        | 2 | 2      |        |      | L     | OC2  | 2     |        |       |       |      |        |         | L    | Locat  | ion 2   |       |       |     |      |       |      |       |     |       |     |       |      |          |       |                   |            |

| 1      | C | LKOL   | JT1P   | PEN  |       |      |       | 0      |       |       |      | R      | W       |      |        | CL      | κοι   | JT1 I | Pin | Ena  | able  |      |       |     |       |     |       |      |          |       |                   |            |

|        | ۷ | Vhen s | set, t | he C | LKC   | DUT  | 1 pii | n is e | enab  | led.  |      |        |         |      |        |         |       |       |     |      |       |      |       |     |       |     |       |      |          |       |                   |            |

| 0      | C | LKOL   | JT0P   | ΡEΝ  |       |      |       | 0      |       |       |      | R      | W       |      |        | CL      | κοι   | то    | Pin | Ena  | able  |      |       |     |       |     |       |      |          |       |                   |            |

|        | V | Vhen s | set, t | he C | LKC   | DUT  | 0 pii | n is e | enab  | led.  |      |        |         |      |        |         |       |       |     |      |       |      |       |     |       |     |       |      |          |       |                   |            |

# 11.5.28 CMU\_LOCK - Configuration Lock Register

| Offset |    |       |    |    |    |    |    |    |      |       |     |      |       |      | Bi     | it Po | siti  | on    |      |       |       |      |       |     |         |      |       |      |      |        |       |       |

|--------|----|-------|----|----|----|----|----|----|------|-------|-----|------|-------|------|--------|-------|-------|-------|------|-------|-------|------|-------|-----|---------|------|-------|------|------|--------|-------|-------|

| 0x084  | 31 | 30    | 29 | 28 | 27 | 26 | 25 | 24 | 23   | 22    | 21  | 20   | 19    | 18   | 17     | 16    | 15    | 14    | 13   | 12    | 5     | 10   | ი     | 8   | 7       | 9    | 5     | 4    | ю    | 2      | -     | 0     |

| Reset  |    |       |    |    |    |    |    |    |      |       |     |      |       |      |        |       |       |       |      |       |       |      |       |     | 0x0000  |      |       |      |      |        |       |       |

| Access |    | R R R |    |    |    |    |    |    |      |       |     |      |       |      |        |       |       |       |      |       |       |      |       |     |         |      |       |      |      |        |       |       |

| Name   |    |       |    |    |    |    |    |    |      |       |     |      |       |      |        |       |       |       |      |       |       |      |       |     | LOCKKEY |      |       |      |      |        |       |       |

| Bit    | Na | me    |    |    |    |    |    | Re | eset |       |     | A    | ١cc   | ess  | 5      | De    | scri  | ipti  | on   |       |       |      |       |     |         |      |       |      |      |        |       |       |

| 31:16  | Re | serve | ed |    |    |    |    | То | ensi | ure c | omp | atib | ility | with | n futu | ire d | evice | es, a | alwa | ays v | vrite | bits | to 0. | Mor | re int  | form | natio | n in | Sect | tion 2 | .1 (j | o. 3) |

### 12.3.1 Clock Source

Three clock sources are available for use with the watchdog, through the CLKSEL field in WDOG\_CTRL. The corresponding clocks must be enabled in the CMU. The SWOSCBLOCK bit in WDOG\_CTRL can be written to prevent accidental disabling of the selected clocks. Also, setting this bit will automatically start the selected oscillator source when the watchdog is enabled. The PERSEL field in WDOG\_CTRL is used to divide the selected watchdog clock, and the timeout for the watchdog timer can be calculated like this:

#### WDOG Timeout Equation

$$\Gamma_{\text{TIMFOUT}} = (2^{3+\text{PERSEL}} + 1)/f,$$

(12.1)

where f is the frequency of the selected clock.

It is recommended to clear the watchdog first, if PERSEL is changed while the watchdog is enabled.

To use this module, the LE interface clock must be enabled in CMU\_HFCORECLKEN0, in addition to the module clock.

Note

Before changing the clock source for WDOG, the EN bit in WDOG\_CTRL should be cleared. In addition to this, the WDOG\_SYNCBUSY value should be zero.

### 12.3.2 Debug Functionality

The watchdog timer can either keep running or be frozen when the device is halted by a debugger. This configuration is done through the DEBUGRUN bit in WDOG\_CTRL. When code execution is resumed, the watchdog will continue counting where it left off.

### 12.3.3 Energy Mode Handling

The watchdog timer can be configured to either keep on running or freeze when entering EM2 or EM3. The configuration is done individually for each energy mode in the EM2RUN and EM3RUN bits in WDOG\_CTRL. When the watchdog has been frozen and is re-entering an energy mode where it is running, the watchdog timer will continue counting where it left off. For the watchdog there is no difference between EM0 and EM1. The watchdog does not run in EM4, and if EM4BLOCK in WDOG\_CTRL is set, the CPU is prevented from entering EM4.

#### Note

If the WDOG is clocked by the LFXO or LFRCO, writing the SWOSCBLOCK bit will effectively prevent the CPU from entering EM3. When running from the ULFRCO, writing the SWOSCBLOCK bit will prevent the CPU from entering EM4.

### 12.3.4 Register access

Since this module is a Low Energy Peripheral, and runs off a clock which is asynchronous to the HFCORECLK, special considerations must be taken when accessing registers. Please refer to Section 5.3 (p. 20) for a description on how to perform register accesses to Low Energy Peripherals. note that clearing the EN bit in WDOG\_CTRL will reset the WDOG module, which will halt any ongoing register synchronization.

#### Note

Never write to the WDOG registers when it is disabled, except to enable it by setting WDOG\_CTRL\_EN or when changing the clock source using WDOG\_CTRL\_CLKSEL. Make sure that the enable is registered (i.e. WDOG\_SYNCBUSY\_CTRL goes low), before writing other registers.

| Bit | Name                      | Reset                                | Access              | Description                                                                  |  |  |  |  |  |  |  |  |  |  |  |

|-----|---------------------------|--------------------------------------|---------------------|------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|     | Indicates that EBI_TFTF   | PIXEL is full.                       |                     |                                                                              |  |  |  |  |  |  |  |  |  |  |  |

| 9   | TFTPIXEL1EMPTY            | 0                                    | R                   | EBI_TFTPIXEL1 is empty.                                                      |  |  |  |  |  |  |  |  |  |  |  |

|     | Indicates that EBI_TFTF   | PIXEL1 is empty.                     |                     |                                                                              |  |  |  |  |  |  |  |  |  |  |  |

| 8   | TFTPIXEL0EMPTY            | 0                                    | R                   | EBI_TFTPIXEL0 is empty.                                                      |  |  |  |  |  |  |  |  |  |  |  |

|     | Indicates that EBI_TFTF   | licates that EBI_TFTPIXEL0 is empty. |                     |                                                                              |  |  |  |  |  |  |  |  |  |  |  |

| 7:5 | Reserved                  | To ensure co                         | mpatibility with fu | ture devices, always write bits to 0. More information in Section 2.1 (p. 3) |  |  |  |  |  |  |  |  |  |  |  |

| 4   | ECCACT                    | 0                                    | R                   | EBI ECC Generation Active.                                                   |  |  |  |  |  |  |  |  |  |  |  |

|     | Indicates that EBI is gen | erating ECC.                         |                     |                                                                              |  |  |  |  |  |  |  |  |  |  |  |

| 3:1 | Reserved                  | To ensure co                         | mpatibility with fu | ture devices, always write bits to 0. More information in Section 2.1 (p. 3) |  |  |  |  |  |  |  |  |  |  |  |

| 0   | AHBACT                    | 0                                    | R                   | EBI Busy with AHB Transaction.                                               |  |  |  |  |  |  |  |  |  |  |  |

|     | Indicates that EBI is bus | y with an AHB Tra                    | insaction.          |                                                                              |  |  |  |  |  |  |  |  |  |  |  |

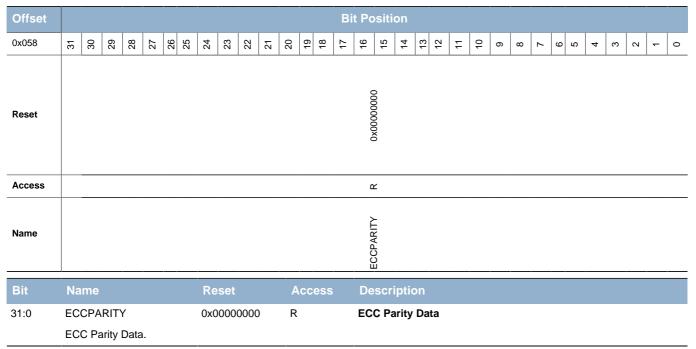

## 14.5.23 EBI\_ECCPARITY - ECC Parity register

# 14.5.24 EBI\_TFTCTRL - TFT Control Register

| Offset |     |                              |     |                                                                                                               |    |      |    |         |     |    |    |          |    |     | Bi   | t Pc  | siti | on   |     |           |   |            |         |             |   |   |   |   |           |   |        |       |

|--------|-----|------------------------------|-----|---------------------------------------------------------------------------------------------------------------|----|------|----|---------|-----|----|----|----------|----|-----|------|-------|------|------|-----|-----------|---|------------|---------|-------------|---|---|---|---|-----------|---|--------|-------|

| 0x05C  | 31  | 30                           | 29  | 28                                                                                                            | 27 | 26   | 25 | 24      | 23  | 22 | 21 | 20       | 19 | 18  | 17   | 16    | 15   | 4    | 13  | 12        | : | 10         | ი       | 8           | 7 | 9 | 5 | 4 | e         | 2 | -      | 0     |

| Reset  |     |                              |     |                                                                                                               |    |      |    | 0       |     |    |    |          |    |     | ,    | 0     |      |      |     | 0         |   | 0×0        | 0       | 0           |   |   | , |   | 0×0       |   | c<br>c | 0X0   |

| Access |     |                              |     |                                                                                                               |    |      |    | RW      |     |    |    |          |    |     |      | RW    |      |      |     | RV        |   | RW         | RW      | RV          |   |   |   |   | RW        |   |        | <br>צ |

| Name   |     |                              |     |                                                                                                               |    |      |    | RGBMODE |     |    |    | DAINAGEL |    |     |      | WIDTH |      | -    |     | COLOR1SRC |   | INTERLEAVE | FBCTRIG | SHIFTDCLKEN |   |   |   |   | MASKBLEND |   |        | 00    |

| Bit    | Na  | ime                          |     |                                                                                                               |    |      |    | Re      | set |    |    | Α        | CC | ess |      | De    | scri | ipti | ion |           |   |            |         |             |   |   |   |   |           |   |        |       |

| 31:25  | Re  | serv                         | ed  | d To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3) |    |      |    |         |     |    |    |          |    |     |      |       |      |      |     |           |   |            |         |             |   |   |   |   |           |   |        |       |

| 24     | RG  | BMO                          | DDE |                                                                                                               |    | 0 RW |    |         |     |    |    |          |    | TF  | r RG | BI    | Mod  | de   |     |           |   |            |         |             |   |   |   |   |           |   |        |       |

|        | Thi | his field sets TFT RGB Mode. |     |                                                                                                               |    |      |    |         |     |    |    |          |    |     |      |       |      |      |     |           |   |            |         |             |   |   |   |   |           |   |        |       |

## ...the world's most energy friendly microcontrollers

|       | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reset                                                                                                                                                                                                                                                                                                         | Acces                                                              | ss Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Mode                                                                                                                                                                                                                                                                                                          |                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RGB565                                                                                                                                                                                                                                                                                                        |                                                                    | RGB data is 565.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RGB555                                                                                                                                                                                                                                                                                                        |                                                                    | RGB data is 555.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23:22 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | To ensure co                                                                                                                                                                                                                                                                                                  | mpatibility w                                                      | ith future devices, always write bits to 0. More information in Section 2.1 (p. 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21:20 | BANKSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x0                                                                                                                                                                                                                                                                                                           | RW                                                                 | Graphics Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | This field sets t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | he Memory Bank containing                                                                                                                                                                                                                                                                                     | g the Frame                                                        | Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Mode                                                                                                                                                                                                                                                                                                          |                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |